Imagination Technologies (IMG.L) 宣布,該公司的多線程 MIPS?* 處理器內(nèi)核能比單線程處理器在手機(jī)和平板電腦等用戶設(shè)備上為LTE基帶處理帶來顯著的性能效益。

2013-02-28 16:11:16 980

980 非信令(Non-signaling)測試方案市場滲透率急速攀升。中國移動為實現(xiàn)全球漫游,計劃于2013年底推出5模13頻智能手機(jī),可望帶動用于產(chǎn)線的非信令測試方案需求迅速增溫,以大幅縮短智能手機(jī)的測試時間,助力智能手機(jī)品牌商搶占市場先機(jī)。

2013-12-25 09:55:28 919

919 設(shè)計人員選擇具有優(yōu)秀調(diào)試能力的FPGA器件,可以縮短開發(fā)周期并降低成本,同時顯著加快上市速度。

2016-11-10 01:14:11 1617

1617

Z/N1解決方案套件陣容現(xiàn)已完整呈現(xiàn),最新推出的RZ/N1L解決方案套件使評估時間縮短多達(dá)3個月。

2018-03-06 14:12:46 6039

6039 在Vivado Implementation階段,有時是有必要分析一下什么原因?qū)е逻\行時間(runtime)過長,從而找到一些方法來縮短運行時間。

2019-05-29 14:37:45 13596

13596

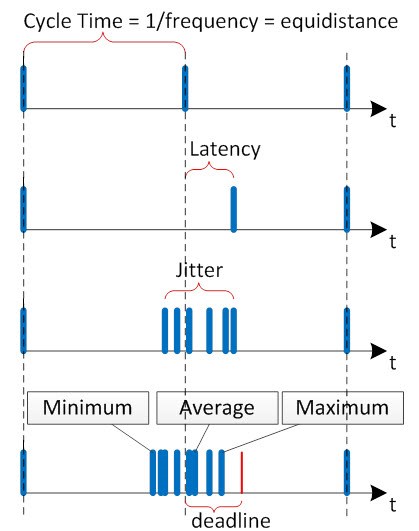

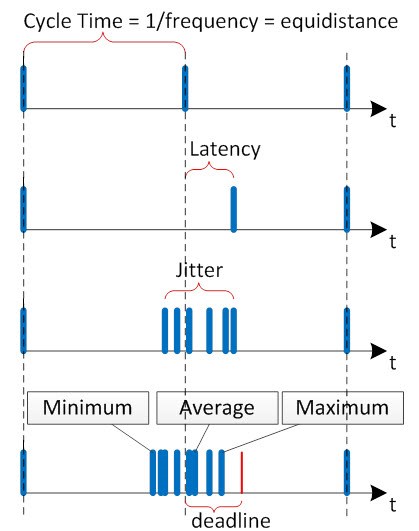

上的 工業(yè)以太網(wǎng)博客系列 中寫過關(guān)于它們的文章。 這些工業(yè)以太網(wǎng)標(biāo)準(zhǔn)支持?jǐn)?shù)十微秒范圍內(nèi)的最小周期時間 - 舉一個具體的例子,PROFINET IRT v2.3支持低至31.25μs的周期時間。然而

2023-02-13 14:46:28 7448

7448

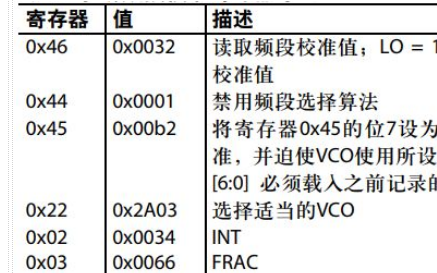

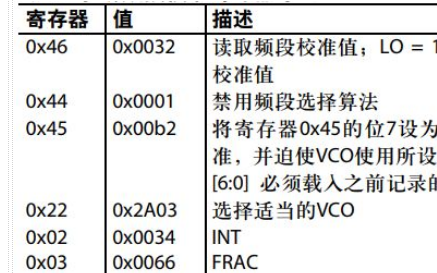

本文以高度集成的解調(diào)器和頻率合成器 ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。

2018-05-22 09:00:04 4813

4813

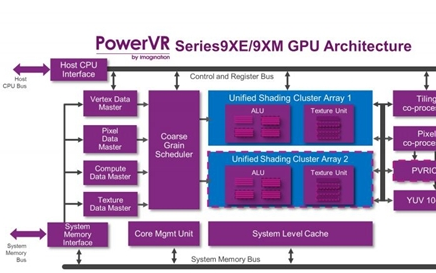

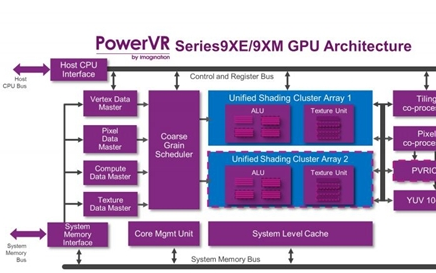

Imagination Technologies宣布推出最新款的增強(qiáng)工具,以幫助開發(fā)者對使用了PowerVR圖形處理器的Android設(shè)備進(jìn)行圖形性能優(yōu)化。

2019-03-21 10:32:32 1049

1049

在蜂窩物聯(lián)網(wǎng)應(yīng)用中使用標(biāo)準(zhǔn)天線,可以省去定制解決方案所需的設(shè)計費用和周期時間,從而大幅縮短上市時間。

2021-01-30 09:53:34 707

707 使用自動校準(zhǔn)模式時,總鎖定時間對某些應(yīng)用來說可能太長。 本應(yīng)用筆記提出一種通過手動選擇頻段來顯著縮短鎖定時間的方案

2021-06-21 09:53:59 4651

4651

為什么Imagination要加入FIDO聯(lián)盟?

2021-01-26 07:53:54

Imagination的光線追蹤等級系統(tǒng)

2020-12-21 06:02:41

Imagination獲得ISO 26262標(biāo)準(zhǔn)的一致性認(rèn)證聲明

2021-02-04 07:51:24

Flexible Access計劃,則此材料將使您能夠解釋所有可用IP的PPA分析數(shù)據(jù)。對于不是成員,它仍然可以提供關(guān)于使用PPA數(shù)據(jù)的寶貴指導(dǎo),并且取決于IP如果您感興趣,請進(jìn)一步?jīng)Q定為您的項目許可哪個

2023-08-08 06:20:44

可提供高通各種芯片文檔,有意詳談。

2014-10-31 08:45:12

周期時間的測量 開關(guān)周期時間Tperiod(uS) 11.6762 開關(guān)管的開關(guān)損耗Pswitch(W) 0.327087666 開關(guān)管的導(dǎo)通損耗Pon-resistance(W) 0.477385448 開關(guān)管的總功耗Ploss(W) 0.804473114

2011-06-10 10:19:20

支持并行、串行等靈活的軟件架構(gòu),…… 通過本開發(fā)板提供的軟硬件實驗環(huán)境,可以使你快速掌握多核網(wǎng)絡(luò)軟件開發(fā)所需要的基本知識。另外,本工作室對有快速提高多核網(wǎng)絡(luò)軟件開發(fā)方面需求的客戶提供專業(yè)的培訓(xùn)課程

2009-04-30 18:28:47

硅技術(shù)引領(lǐng)汽車設(shè)計時代現(xiàn)代汽車中的半導(dǎo)體技術(shù)和產(chǎn)品正在迅猛增加,消費者對附加功能的需求正將汽車從一個以電氣系統(tǒng)為輔的機(jī)械系統(tǒng),變成一個沒有電子系統(tǒng)就無法正常運行的機(jī)電系統(tǒng)。這一發(fā)展趨勢刺激了市場對優(yōu)質(zhì)、強(qiáng)大并具有成本效益的硅解決方案的需求。

2009-12-11 16:07:32

深入的生命周期可見性,豐富的分析,并增加對其硅設(shè)備的控制機(jī)制,包括動態(tài)電壓和頻率縮放(DVFS)。這些特性的組合極大地優(yōu)化了設(shè)備操作的功耗或數(shù)據(jù)吞吐量性能(圖4)。圖4。圖片由 Synopsys 提供

2022-06-13 10:29:50

的網(wǎng)站上,都可以獲得所有這些模型。另外,還有各種計算器可供下載。 總之,PCB設(shè)計人員有大量工具可供選擇,其可幫助順利完成設(shè)計規(guī)劃和創(chuàng)建過程。盡管這些工具提供的答案并不能除去試驗電路板階段,但它們可以迅速地為您提供經(jīng)驗證的一些解決方案供實驗室使用—最終縮短產(chǎn)品上市時間。

2011-10-25 09:45:08

EVAL-AD5687RSDZ,用于AD5687R,四路,12位,串行電壓輸出數(shù)模轉(zhuǎn)換器的評估板。 EVAL-AD5687RSDZ旨在幫助客戶快速對新型AD5687R電路進(jìn)行原型設(shè)計并縮短設(shè)計時間

2019-09-12 08:35:23

請問,F(xiàn)28069 的XRS 周期復(fù)位是由什么引起的?周期時間大約為13.8ms左右,可以確認(rèn)的是:1、不是外圍復(fù)位電路引起的XRS復(fù)位;2、芯片的供電電源很穩(wěn)定,應(yīng)該也不是供電電壓引起的。請各位大神給點意見,該如何定位找到該故障??

2020-06-09 16:00:31

1us2、XE164集成DSP指令,支持復(fù)雜運算最高主頻80MHz集成3個電機(jī)控制單元雙獨立A/D單元,采樣時間小于200ns3、功率板支持23-56V直流輸入,最大7.5A電流4、套件提供15W

2018-12-04 09:52:31

DN415 - 具PowerPath控制功能的開關(guān)USB電源管理器可提供極快的充電時間并產(chǎn)生非常少的熱量

2019-08-06 14:20:17

硬件和軟件套件有助加快并簡化固態(tài)射頻系統(tǒng)開發(fā)經(jīng)優(yōu)化后可供烹飪、照明、工業(yè)加熱/烘干、醫(yī)療/制藥和汽車點火系統(tǒng)的商業(yè)制造商使用系統(tǒng)設(shè)計人員能夠以LDMOS的價格充分利用硅基氮化鎵性能的優(yōu)勢在IMS現(xiàn)場

2017-08-03 10:11:14

過的代碼行后的定時器值

我配置了一個 e-timer(etimer2, channel0) 來測量我的代碼之間的時間間隔。該定時器配置為從 MOTC 源提供時鐘,并除以 1,即 160MHz。我的系統(tǒng)

2023-06-05 12:50:56

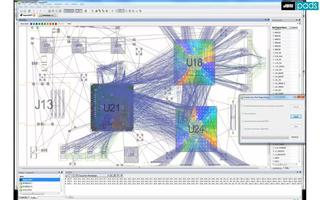

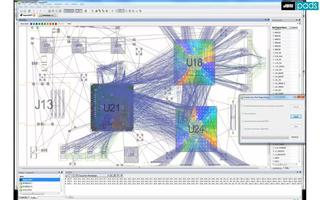

PADS 制造準(zhǔn)備可幫助您優(yōu)化產(chǎn)品質(zhì)量,縮短周期時間和節(jié)省成本。

2019-05-06 11:01:48

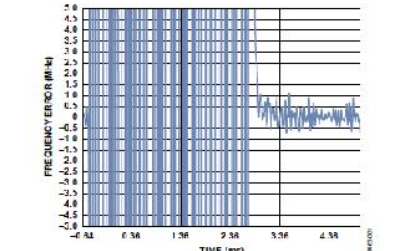

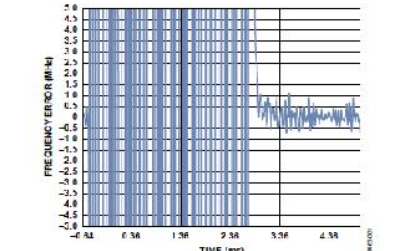

增加;對于給定 PFD 周期,提高環(huán)路帶寬會縮短周跳時間。因此,當(dāng)使用自動校準(zhǔn)模式時,總鎖定時間對某些應(yīng)用來說可能太長。本文提出一種通過手動選擇頻段來顯著縮短鎖定時間的方案,步驟如下:1、按照表 1

2018-11-01 10:42:37

最近公司在做一個開關(guān)電源的仿真,用的是暫態(tài)分析,但是時間總是長不了,幾十毫秒的波形也要運行個20分鐘,我想看到全部的過程,但是要運行幾十個小時,有沒有什么辦法可以加速仿真,縮短運行時間的?求助高手!

2012-07-26 13:39:52

QCC3026是一款基于超低功耗架構(gòu)的入門級閃存可編程藍(lán)牙音頻SoC,專為緊湊型功能優(yōu)化的Qualcomm TrueWireless耳塞而設(shè)計。QCC3026旨在為我們的客戶提供有助于縮短開發(fā)時間并

2021-07-22 09:18:07

本文以戰(zhàn)術(shù)軍用通信系統(tǒng)的首選碼RS(31,15)碼為例,對生成多項式進(jìn)行了優(yōu)化,并采用查表法的原理極大地提高了編碼器運算數(shù)據(jù)的能力,縮短了運算周期,最終利用VHDL語言編譯,在FPGA中實現(xiàn),得到了正確的RS編譯碼。

2021-05-06 09:27:33

【摘要】:表面組裝技術(shù)是當(dāng)今電子工業(yè)的支柱技術(shù)。這些年來隨著市場競爭的日益加劇、產(chǎn)品投放市場的時間日益縮短、生產(chǎn)周期越來越短和新技術(shù)不斷引入,如何提高SMT系統(tǒng)的生產(chǎn)效率就變得越來越重要,因此

2010-04-24 10:09:25

SimpleLink器件范圍內(nèi)的應(yīng)用提供了輕松的代碼可移植性。平臺級軟件的可移植性使工程師能夠?qū)④浖_發(fā)的一次性投入重復(fù)應(yīng)用于平臺內(nèi)的多個其他產(chǎn)品和應(yīng)用,從而大大縮短了設(shè)計時間。 借助SimpleLink SDK

2019-03-27 06:45:01

。ZMP1107_EVB 評估套件主要用于評估和開發(fā) ZMP1107 芯片的多媒體功能和外圍接口,方便客戶對芯片進(jìn)行資源評估和功能開發(fā),同時提供硬件相關(guān)的參考設(shè)計,幫助客戶快速入門,縮短研發(fā)周期。

2022-10-18 07:30:41

ZSP G4 DSP架構(gòu)能否為無線通信提供最佳PPA設(shè)計?

2021-05-24 06:30:07

按照500ms或者1s的時間間隔配置以便于降低功耗。當(dāng)有設(shè)備連接了我的藍(lán)牙設(shè)備以后,我想把這個間隔時間縮短,比如縮短成100ms或者更短,以便于增加數(shù)據(jù)傳輸?shù)乃俾省?請問這個設(shè)想是否可以實現(xiàn),如果可以時間,能否提供一下相關(guān)的例子或者給與一些技術(shù)指導(dǎo)?

2024-02-21 08:22:35

請問stm32的指令周期是怎么樣的呢?我知道它與51類單片機(jī)是不一樣的。看網(wǎng)上說的好像指令周期時間不確定,平均速度大約為1.25MIPS/Mz。不知道對不對?

2016-01-22 20:39:22

【STM32F411 Nucleo試用體驗】之藍(lán)牙和傳感器套件詳細(xì)介紹,讓你感覺意法廠商的科技技術(shù),產(chǎn)品套件的配套使用降底了開發(fā)人員的專業(yè)技術(shù)能力,和開發(fā)周期時間!藍(lán)牙和傳感器套件已經(jīng)把市面上大部份

2016-07-20 23:47:26

優(yōu)化嵌入式Linux的啟動時間之Bootloader注:本文轉(zhuǎn)載自微信公眾號嵌入式客棧——優(yōu)化嵌入式Linux的啟動時間之Bootloader原創(chuàng)逸珺嵌入式客棧2020-03-05導(dǎo)讀:嵌入式

2021-12-16 07:19:02

、機(jī)器周期和時鐘周期之間的關(guān)系:指令周期通常用若干個機(jī)器周期表示,而機(jī)器周期時間又包含有若干個時鐘周期。以51為例,晶振22.1184M,時鐘周期(晶振周期)就是(1/22.1184)μs,一個機(jī)器周期

2021-01-19 10:34:23

問題描述:STM32F103平臺,uCOS-III系統(tǒng)。現(xiàn)在有一個任務(wù)需要周期性執(zhí)行,每0.4ms執(zhí)行一次,周期時間小于uCOS系統(tǒng)Tick時間,所以不能采用uCOS系統(tǒng)的定時器來做。那該如何周期性的執(zhí)行此任務(wù)呢??

2019-11-07 04:35:42

Run-time 縮短到最低限度。目前啟動需要96ms,我希望能達(dá)到Bootloader 優(yōu)化級別:優(yōu)化性能 (-O2) Bootloader 日志詳細(xì)程度:無輸出[x] 退出深度睡眠時跳過圖像驗證

2023-03-01 06:02:37

如何手動縮短PLL鎖定時間?你知道嗎?利用手動頻段選擇,鎖定時間可從典型值4.5 ms 縮短到典型值360 μs。本文以高度集成的解調(diào)器和頻率合成器ADRF6820 為例,告訴大家如何手動選擇頻段以縮短PLL鎖定時間。

2019-07-31 07:54:28

就會發(fā)生周跳。PFD 輸入端的相位誤差積累過快,PLL 來不及校正,電荷泵暫時沿錯誤方向吸入電荷,使鎖定時間急劇縮短。如果PFD 頻率與環(huán)路帶寬的比值提高,周跳也會增加;對于給定PFD 周期,提高環(huán)路

2018-08-04 15:00:17

如何用Bluetooth Developer Studio縮短70%藍(lán)牙開發(fā)時間?

2021-05-21 06:30:46

實現(xiàn)了過程數(shù)據(jù)的實時視圖。機(jī)器與產(chǎn)品的聯(lián)系還提供了產(chǎn)品數(shù)據(jù)的實時視圖。由工業(yè)服務(wù)機(jī)器人操作的自動化機(jī)器和生產(chǎn)單元處理原材料和生產(chǎn)部件。在生產(chǎn)過程中進(jìn)行產(chǎn)品和機(jī)器質(zhì)量檢查,以進(jìn)一步縮短周期時間。這種方式

2022-11-14 06:33:01

的需求。我們的共同客戶可利用此新的PDK 縮短開發(fā)周期,并加快部署創(chuàng)新的產(chǎn)品。欲了解更多詳細(xì)信息,請訪問這里。

2018-10-26 08:54:41

速率市場中,MACOM也將為客戶提供完整的解決方案和服務(wù),進(jìn)一步幫助客戶快速打開新的產(chǎn)品開發(fā)。 MACOM不斷地通過并購,豐富自己的產(chǎn)品線,改善產(chǎn)品組合,致力于降低制造成本,幫助客戶縮短研發(fā)周期

2017-11-17 10:11:47

怎么縮短STlink對STM8燒錄固件的時間

2023-10-09 07:02:16

是否可提供ESP32-S3聯(lián)網(wǎng)bin固件和自適應(yīng)認(rèn)證固件

2023-03-13 09:26:40

成本效益,有助于縮短產(chǎn)品發(fā)布時間TLC6C5912-Q1 集成了熱關(guān)斷防護(hù)功能,可避免過熱和對 IC 造成損壞切換時間緩慢:上升時間 = 207ns 且下降時間 = 128ns,可顯著降低 EMI

2022-09-26 07:40:44

你好!我用PIC18F45 80用20MHz晶體測量兩個正方波脈沖之間的周期時間,在上升沿上設(shè)置CCP1觸發(fā),在ISR中取一個“時間戳”,然后計算MS中的時間,但用頻率為10Hz的波形發(fā)生器進(jìn)行測試

2018-09-13 15:28:23

我已經(jīng)了解到proteus中VSM Logic Analyser 可以同時分析多個端口的電平變化,但總線周期時間太短,即便只有一條指令,也包含許多總線周期,如何才能 記錄下總線周期內(nèi)各個端口的電平變化,得到時序圖?

2015-03-13 19:42:47

PFD頻率與環(huán)路帶寬的比值提高,周跳也會增加;對于給定PFD周期,提高環(huán)路帶寬會縮短周跳時間。因此,當(dāng)使用自動校準(zhǔn)模式時,總鎖定時間對某些應(yīng)用來說可能太長。本應(yīng)用筆記提出一種通過手動選擇頻段來顯著縮短

2018-10-31 10:16:46

每一版本都提供了完整的FPGA設(shè)計流程,并且專門針對特定的用戶群體(工程師)和特定領(lǐng)域的設(shè)計方法及設(shè)計環(huán)境要求進(jìn)行了優(yōu)化。那大家知道賽靈思ISE? 設(shè)計套件11.1版對FPGA有什么優(yōu)化作用嗎?

2019-07-30 06:52:50

手動選擇頻段以縮短 PLL 鎖定時間——ADRF6820

2021-01-21 06:24:47

功能 (印刷電路圖案、電路的輸入/輸出阻抗等),精度更高,阻抗覆蓋范圍更廣( 20 Hz 至 120 MHz)。 在線測量可優(yōu)化設(shè)計環(huán)境中的周期時間或降低生產(chǎn)環(huán)境中

2023-03-07 15:48:32

全球領(lǐng)先的硅產(chǎn)品知識產(chǎn)權(quán)(SIP)平臺解決方案和數(shù)字信號處理器(DSP)內(nèi)核授權(quán)廠商CEVA公司宣布可提供應(yīng)用于CEVA-MM3000圖像和視覺平臺的全新應(yīng)用開發(fā)工具套件(Application

2013-08-06 12:38:58 810

810 單位面積最佳的每 mW 性能。##與前一代相同配置的內(nèi)核相比,根據(jù)最新的業(yè)界標(biāo)準(zhǔn)基準(zhǔn)測試,Series6XT 內(nèi)核最高可達(dá)到 50% 的性能提升。##Imagination 可為開發(fā)人員提供免費的 PowerVR 圖形 SDK,這是一個跨平臺的工具套件,可支持所有的 3D 圖形應(yīng)用程序開發(fā)。

2014-01-13 13:32:30 1428

1428 客戶提供低風(fēng)險、高成本效益的解決方案,并已針對低數(shù)據(jù)傳輸率應(yīng)用進(jìn)行了優(yōu)化設(shè)計,包括資產(chǎn)追蹤、車隊管理、安全監(jiān)控、銷售點、健康監(jiān)控、智能測量,以及數(shù)量不斷增加的各類 IoT 應(yīng)用。

2016-09-08 10:36:37 796

796 多源時間序列中具有顯著時間間隔的Shapelet對挖掘_李鐘麒

2017-01-08 10:11:41 0

0 提供低風(fēng)險、高成本效益的解決方案,并已針對低數(shù)據(jù)傳輸率應(yīng)用進(jìn)行了優(yōu)化設(shè)計,包括資產(chǎn)追蹤、車隊管理、安全監(jiān)控、銷售點、健康監(jiān)控、智能測量,以及數(shù)量不斷增加的各類 IoT 應(yīng)用。 通過利用

2017-02-09 15:36:11 175

175 多功能傳感器,結(jié)合近距離和環(huán)境光傳感可能是智能手機(jī)設(shè)計師誰尋求節(jié)省更多的權(quán)力,減少房地產(chǎn),并縮短其設(shè)計周期,以滿足他們的時間到市場需求的答案。

2017-07-04 09:49:57 11

11 環(huán)境,完美集成了Sigrity工具與CadenceAllegro技術(shù),較之于當(dāng)前市場上依賴于第三方建模工具的產(chǎn)品,Sigrity 2018版本可提供效率更高、出錯率更低的解決方案,大幅度縮短設(shè)計周期

2018-07-25 17:59:00 14045

14045 Abhishek Kapoor與X-Microwave首席執(zhí)行官John Richardson共同探討ADI與X-Microwave之間的合作X-Microwave工具和評估板將縮短設(shè)計周期時間,減少使用多個評估板。

2018-06-06 13:46:00 2891

2891 演講中王強(qiáng)還提到了Imagination近期將要推出PowerVR 3NX神經(jīng)網(wǎng)絡(luò)加速器產(chǎn)品。相比2NX,該產(chǎn)品將提供更多的內(nèi)核選擇,每周期可完成的MAC數(shù)量將提升至4096個,運算能力最高可達(dá)每秒10TOPs,同時PPA特性將得到大幅度提升。

2018-11-13 15:41:08 2856

2856 Abhishek Kapoor與X-Microwave首席執(zhí)行官John Richardson共同探討ADI與X-Microwave之間的合作X-Microwave工具和評估板將縮短設(shè)計周期時間,減少使用多個評估板。

2019-07-04 06:10:00 2336

2336 在遵循管腳特定的規(guī)則和約束的同時,可以在 PCB 上的多個 FPGA 之間自動優(yōu)化信號管腳分配。減少布線層數(shù),最大限度地減少 PCB 上的交叉數(shù)量并縮短總體走線長度,以及減少信號完整性問題,從而提高完成率并縮短 FPGA 的布線時間。

2019-05-14 06:23:00 3276

3276

“瑞薩電子憑借R-Car V3M入門套件可以顯著降低開發(fā)強(qiáng)度并加速上市時間,滿足快速增長的NCAP前置攝像頭市場需求。”瑞薩電子副總裁Jean-Francois Chouteau表示。

2019-08-02 08:39:09 2621

2621 Vishay宣布,為了兌現(xiàn)公司支持多層陶瓷片式電容器(MLCC)客戶的承諾,宣布縮短MLCC供貨周期。

2019-07-15 15:37:10 844

844 全球電子元器件與開發(fā)服務(wù)分銷商e絡(luò)盟獨家推出Raspberry Pi 4入門套件。這款全新入門套件包含Raspberry Pi 4 B型計算機(jī)及e絡(luò)盟自有品牌Multicomp Pro系列產(chǎn)品,支持開箱即用,可為新手用戶大幅縮短新品開發(fā)時間。

2020-03-29 17:49:12 2604

2604 新的方法引入了可重復(fù)使用的形狀記憶聚合物心軸、自動的編織層工藝和基于VARTM復(fù)合材料固化技術(shù)的烤箱,顯著降低成本并縮短周期時間。

2020-04-01 11:29:29 678

678 Imagination 和 Packetcraft 已經(jīng)打造了一套完整的解決方案,可輕松集成至系統(tǒng)級芯片(SoC)中。利用這種集成硬件和軟件的解決方案,客戶可以減少開發(fā)時間并最終縮短產(chǎn)品上市時間,從而獲得顯著優(yōu)勢。

2020-09-20 10:07:51 1615

1615 后,讀取操作必須將極化恢復(fù)到其原始狀態(tài),這會增加讀取操作的周期時間。寫周期需要一個初始的預(yù)充電時間,這可能會增加初始訪問時間。環(huán)境溫度高于85C,由于自由電荷的積累導(dǎo)致FRAM磨損,從而導(dǎo)致影響10年的數(shù)據(jù)保留。 Everspin MRAM將提供最

2020-10-09 16:21:18 269

269 DN415 - 具PowerPath控制功能的開關(guān)USB電源管理器可提供極快的充電時間并產(chǎn)生非常少的熱量

2021-03-21 08:04:42 0

0 定時中斷可用來支持一個周期性的活動,周期時間以1ms為計量單位,周期時間可從5ms~255ms。對于定時中斷0,把周期時間寫入SMB34,對于定時中斷1,把周期時間寫入SMB35。每當(dāng)達(dá)到定時時間值,相關(guān)定時器溢出,執(zhí)行中斷處理程序。

2021-03-24 09:42:08 4127

4127 賽靈思公司昨日宣布推出 Vivado ML 版,這是業(yè)內(nèi)首個基于機(jī)器學(xué)習(xí)( ML )優(yōu)化算法以及先進(jìn)的面向團(tuán)隊協(xié)作的設(shè)計流程打造的 FPGA EDA 工具套件,可以顯著節(jié)省設(shè)計時間與成本。與目前

2021-06-24 11:42:16 1823

1823 賽靈思近日宣布推出 Vivado ML 版,這是業(yè)內(nèi)首個基于機(jī)器學(xué)習(xí)(ML )優(yōu)化算法以及先進(jìn)的面向團(tuán)隊協(xié)作的設(shè)計流程打造的 FPGA EDA 工具套件,可以顯著節(jié)省設(shè)計時間與成本,與目前

2021-07-02 16:40:13 2403

2403

“該平臺的真正目的是讓工程師能夠真正快速地迭代,減少周期時間。我們看到工程師在公司內(nèi)部使用它的一種方式是開發(fā)概念驗證。您甚至可以將其用作測試客戶反饋的工具,”貝克解釋道。

2022-05-24 15:10:47 659

659

復(fù)雜的積層HDI技術(shù)的應(yīng)用不斷擴(kuò)展。導(dǎo)通孔的鍍銅工藝已經(jīng)很成熟,但需要維護(hù)且耗時。目前的導(dǎo)電膏填充物導(dǎo)電性不如實心銅,但可以縮短周期時間,并且具有高導(dǎo)電性和成本效益。

2022-11-02 10:17:06 1643

1643 當(dāng)電容器受到負(fù)載電阻的影響時,它的放電時間會縮短。本文將詳細(xì)探討電容器負(fù)載電阻降低放電時間縮短的原因,并分析其中的關(guān)鍵因素。

2023-06-30 16:16:20 879

879 電子發(fā)燒友網(wǎng)站提供《縮短ZXCT1009電流監(jiān)測器的響應(yīng)時間.pdf》資料免費下載

2023-07-26 15:33:36 0

0 電子發(fā)燒友網(wǎng)站提供《縮短數(shù)據(jù)復(fù)制時間提高生產(chǎn)效率.pdf》資料免費下載

2023-08-29 11:33:19 0

0 電子發(fā)燒友網(wǎng)站提供《Vivado設(shè)計套件用戶指南之功耗分析和優(yōu)化.pdf》資料免費下載

2023-09-14 10:25:07 0

0 2 Imagination 利用 Cadence Cerebrus 生成式 AI 技術(shù)自動優(yōu)化其最新的 5nm GPU 設(shè)計 3 軟件即服務(wù)(SaaS)模型提供了一種經(jīng)濟(jì)實惠且快速的方式,用于訪問大規(guī)模并行化計算

2023-10-18 15:50:01 160

160 CadenceCerebrus生成式AI技術(shù)自動優(yōu)化其最新的5nmGPU設(shè)計軟件即服務(wù)(SaaS)模型提供了一種經(jīng)濟(jì)實惠且快速的方式,用于訪問大規(guī)模并行化計算和軟件許可容量,從

2023-10-19 08:28:11 431

431

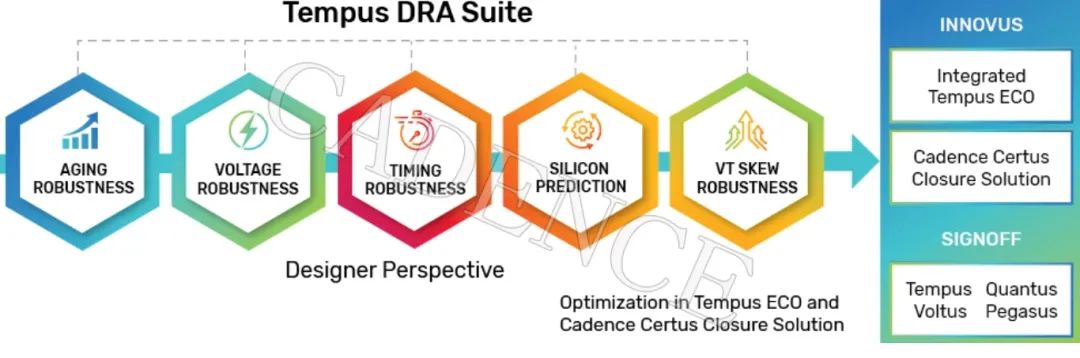

“基于人工智能的cadence cerebrus和更廣泛的cadence數(shù)字進(jìn)程是為復(fù)雜的下一代設(shè)計而設(shè)計的,例如5納米低功耗gpu的imagination。”

2023-10-20 10:04:07 261

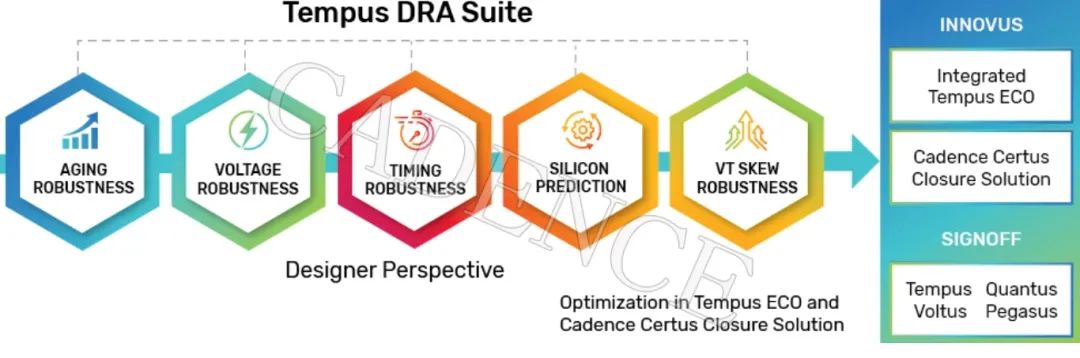

261 實現(xiàn)簽核時,為了保證芯片設(shè)計的耐用性,設(shè)計師會面臨重重挑戰(zhàn),利用 Cadence Tempus 設(shè)計穩(wěn)健性分析(DRA)套件為設(shè)計工程師提供領(lǐng)先的建模技術(shù),可實現(xiàn)最佳功耗、性能和面積目標(biāo)(PPA

2023-11-01 14:50:03 210

210

運動控制系統(tǒng)算法優(yōu)異,可以實現(xiàn)循徑精度、運動速度、周期時間、可程序設(shè)計等機(jī)器人的性能,大幅度提高生產(chǎn)的質(zhì)量、效率以及可靠性3可提供完整的運動控制系統(tǒng)化集成方案。

2023-11-08 10:09:47 194

194

有小伙伴反饋GD32 Timer定時器的周期時間不知如何計算,今天就來安排。

2024-01-22 09:53:55 358

358

根據(jù)瑞銀分析師最近提供給投資者的備忘錄,英偉達(dá)已經(jīng)顯著縮短了其AI GPU的交付周期。這一周期已經(jīng)從去年年底的8-11個月迅速縮短至目前的3-4個月。這一變化引發(fā)了市場的廣泛關(guān)注,分析師們普遍認(rèn)為這背后有兩種可能的原因。

2024-02-18 17:31:09 451

451

電子發(fā)燒友App

電子發(fā)燒友App

評論