門級仿真(gate levelsimulation)也稱之為后仿真,是數(shù)字IC設(shè)計(jì)流程中的一個重要步驟。

2023-06-07 09:55:42 1207

1207

`IC封裝流程`

2011-04-07 10:49:07

集成電路生產(chǎn)流程見下圖:[img][/img]整個流程分為六個部分:單晶硅片制造,IC設(shè)計(jì),光罩制作,IC制造,IC測試和封裝。1.IC生產(chǎn)流程 [單晶硅片制造] 單晶硅片是用來制造IC的,單晶硅

2019-01-02 16:28:35

IC 芯片制造的流程做一下簡單的介紹。一、層層堆棧的芯片架構(gòu)在開始前,我們要先認(rèn)識 IC 芯片是什么。IC,全名集成電路(Integrated Circuit),由它的命名可知它是將設(shè)計(jì)好的電路,以

2022-09-23 17:23:00

GDSⅡ的設(shè)計(jì)流程: 這個可以理解成半定制的設(shè)計(jì)流程,一般用來設(shè)計(jì)數(shù)字電路。 整個流程如下(左側(cè)為流程,右側(cè)為用到的相應(yīng)EDA工具): 一個完整的半定制設(shè)計(jì)流程應(yīng)該是:RTL代碼輸入、功能仿真、邏輯綜合

2012-01-11 13:49:27

1.1 從RTL到GDSⅡ的設(shè)計(jì)流程: 這個可以理解成半定制的設(shè)計(jì)流程,一般用來設(shè)計(jì)數(shù)字電路。整個流程如下(左側(cè)為流程,右側(cè)為用到的相應(yīng)EDA工具): 一個完整的半定制設(shè)計(jì)流程應(yīng)該是:RTL代碼

2018-08-16 09:14:32

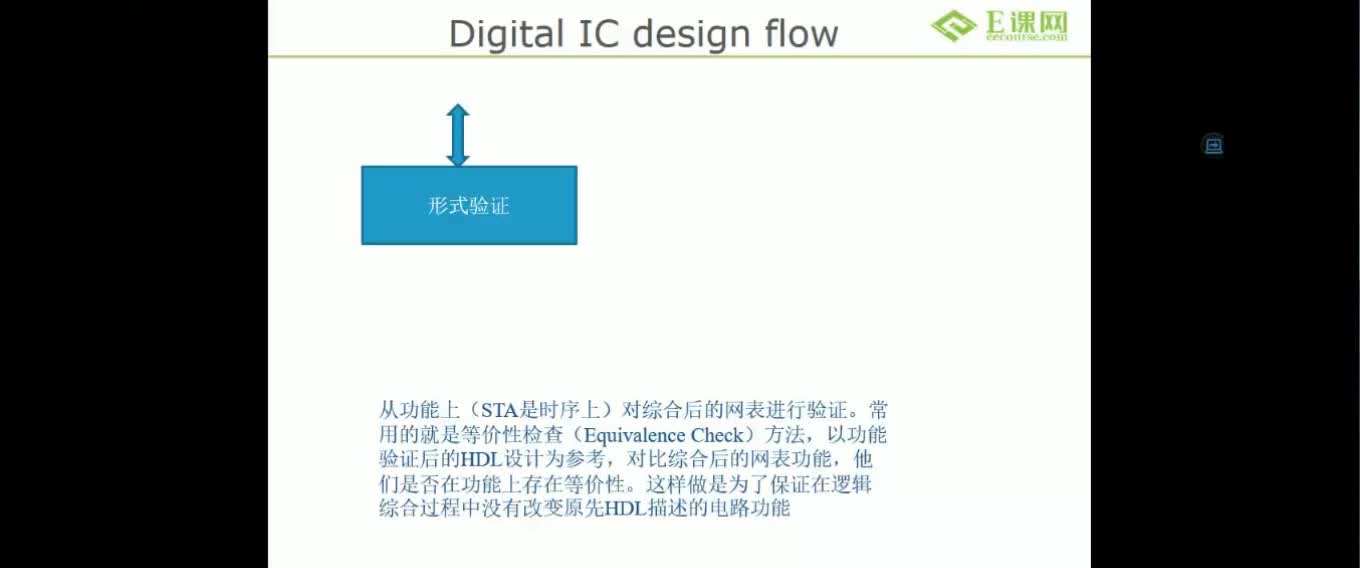

違例時(shí),是沒有辦法正確采樣數(shù)據(jù)和輸出數(shù)據(jù)的,所以以寄存器為基礎(chǔ)的數(shù)字芯片功能肯定會出現(xiàn)問題。STA工具有Synopsys的Prime Time。7. 形式驗(yàn)證這也是驗(yàn)證范疇,它是從功能上(STA是時(shí)序

2018-08-13 17:05:29

關(guān)于IC設(shè)計(jì)的流程是怎樣的?有關(guān)IC設(shè)計(jì)的方法有哪些?

2021-06-21 07:51:54

IC設(shè)計(jì)流程和設(shè)計(jì)方法

2012-08-20 22:15:19

1.使用語言:VHDL/verilog HDL2.各階段典型軟件介紹:輸入工具: SummitSummit公司仿真工具: VCS, VSSSynopsys 公司 綜合器:DesignCompile

2011-12-19 16:20:07

IC設(shè)計(jì)完整流程及工具IC的設(shè)計(jì)過程可分為兩個部分,分別為:前端設(shè)計(jì)(也稱邏輯設(shè)計(jì))和后端設(shè)計(jì)(也稱物理設(shè)計(jì)),這兩個部分并沒有統(tǒng)一嚴(yán)格的界限,凡涉及到與工藝有關(guān)的設(shè)計(jì)可稱為后端設(shè)計(jì)。前端設(shè)計(jì)的主要

2021-07-28 07:51:27

(violation)。這個是數(shù)字電路基礎(chǔ)知識,一個寄存器出現(xiàn)這兩個時(shí)序違例時(shí),是沒有辦法正確采樣數(shù)據(jù)和輸出數(shù)據(jù)的,所以以寄存器為基礎(chǔ)的數(shù)字芯片功能肯定會出現(xiàn)問題。STA工具有Synopsys的Prime

2016-06-29 11:30:46

下出按用途對IC設(shè)計(jì)軟件作一些介紹。IC設(shè)計(jì)工具很多,其中按市場所占份額排行為Cadence、Mentor Graphics和Synopsys。這三家都是ASIC設(shè)計(jì)領(lǐng)域相當(dāng)有名的軟件供應(yīng)商。其它

2012-01-10 10:07:31

想找個線性可控恒流源的IC輸入電源在5伏/9伏左右輸入信號為數(shù)字信號輸出范圍在300mA到1A之間,精度在5毫安,負(fù)載可接12歐有沒有這樣的IC或IC組

2020-05-07 21:57:37

膜制造。 IC后端設(shè)計(jì)工具介紹: 數(shù)字后端設(shè)計(jì)中常用的工具主要由Cadence, Synopsys和Mentor三大公司推出。 邏輯綜合工具:Synopsys DC ,Cadence Genus

2020-12-29 11:53:01

。《數(shù)字IC版圖實(shí)戰(zhàn)培訓(xùn)》是E課網(wǎng)的經(jīng)典課程,已經(jīng)為IC行業(yè)輸送了大量數(shù)字版圖工程師。本次公開課會詳細(xì)介紹IC設(shè)計(jì)行業(yè)情況和數(shù)字版圖工程師的要求,并詳細(xì)介紹我們課程的內(nèi)容,展示我們的實(shí)訓(xùn)環(huán)境。還會開放15

2016-06-14 14:25:40

數(shù)字IC是什么意思?數(shù)字IC前端設(shè)計(jì)流程有哪些?數(shù)字IC后端設(shè)計(jì)流程有哪些?

2021-10-20 06:24:49

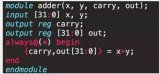

數(shù)字IC設(shè)計(jì)之DC篇:DC流程介紹綜合概念綜合是使用軟件的方法來設(shè)計(jì)硬件, 然后將門級電路實(shí)現(xiàn)與優(yōu)化的工作留給綜合工具的 一種設(shè)計(jì)方法。它是根據(jù)一個系統(tǒng)邏輯功能與性能的要求,在一個包含眾多結(jié)構(gòu)、功能

2021-11-17 07:08:49

數(shù)字IC設(shè)計(jì)工程師-上海職位要求: 1、電子類相關(guān)專業(yè),本科或本科以上學(xué)歷 2、熟悉數(shù)字IC設(shè)計(jì)流程,熟練掌握verilogHDL coding,DC/PT/FT等工具 3、有FPGA設(shè)計(jì)經(jīng)驗(yàn)者優(yōu)先

2015-06-15 10:06:11

數(shù)字電路和與模擬電路的本質(zhì)區(qū)別是什么?數(shù)字IC設(shè)計(jì)流程有哪些?

2021-10-26 06:51:04

數(shù)字IC設(shè)計(jì)的工具有哪些?

2021-06-18 09:47:21

數(shù)字IC設(shè)計(jì)之“數(shù)字SOC全流程漫談從0到1”講師背景:閻如斌老師畢業(yè)于慕尼黑工業(yè)大學(xué)的碩士研究生,具有非常豐富的IC研發(fā)經(jīng)驗(yàn)。在集成電路的從業(yè)10多年之久,同時(shí)也是叩持電子和IC修真院的創(chuàng)始人,并

2021-11-11 06:21:02

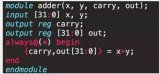

數(shù)字芯片設(shè)計(jì)流程前端設(shè)計(jì)的主要流程:規(guī)格制定芯片規(guī)格: 芯片需要達(dá)到的具體功能和性能方面的要求詳細(xì)設(shè)計(jì)就是根據(jù)規(guī)格要求,實(shí)施具體架構(gòu),劃分模塊功能。HDL編碼使用硬件描述語言(vhdlVerilog

2020-02-12 16:09:48

數(shù)字芯片設(shè)計(jì)流程:功能驗(yàn)證之前與工藝庫沒多大聯(lián)系,驗(yàn)證芯片設(shè)計(jì)的功能是否正確,針對抽象的代碼進(jìn)行功能驗(yàn)證理想值。一致性驗(yàn)證確保生成的網(wǎng)表和代碼設(shè)計(jì)功能一致;DFT之后是數(shù)字后端。靜態(tài)時(shí)序分析,從邏輯

2021-11-10 06:14:28

Cadence工具VirtusoDracula入門介紹Cadence工具Virtuso/Dracula入門介紹.... 21.使用 Virtuso/Diva/Dracula之前的準(zhǔn)備

2012-08-10 18:39:06

EDA設(shè)計(jì)流程及其工具.ppt

2017-01-21 13:07:21

本文以Altera公司的FPGA為目標(biāo)器件,通過開發(fā)實(shí)例介紹FPGA開發(fā)的完整的流程及開發(fā)過程中使用到的開發(fā)工具,包括QuartusII、FPGA CompilerII、Modelsim,并重點(diǎn)解說如何使用這三個工具進(jìn)行協(xié)同設(shè)計(jì)。

2021-04-29 06:04:13

RKNN-Toolkit運(yùn)行非 RKNN 模型時(shí)工具的使用流程是怎樣的?運(yùn)行RKNN 模型時(shí)工具的使用流程是怎樣的?兩者有何不同?

2022-02-10 07:49:45

電路設(shè)計(jì)流程;3、熟練掌握數(shù)字電路設(shè)計(jì)所需知識,如verilog用法和基本電路設(shè)計(jì)技巧;4、熟練掌握各種設(shè)計(jì)相關(guān)EDA工具;5、樂觀積極、勇于接受挑戰(zhàn)。我的QQ:2860394305 有意者簡歷可發(fā):carry.wang@yaxunhr.com

2013-12-13 17:49:21

`IC芯片就像是用樂高積木蓋房子一樣,藉由一層又一層的堆棧,創(chuàng)造自己所期望的造型。然而,蓋房子有相當(dāng)多的步驟,IC制造也是一樣,制造IC究竟有哪些步驟?小編在此介紹下IC芯片制造的流程。層層堆棧

2018-06-14 14:32:27

非常清楚的, 下面就數(shù)字電路聊聊芯片設(shè)計(jì)的一些事情,就是芯片設(shè)計(jì)有哪些活做, 這并不是全面完整的系統(tǒng)介紹,只是個人的了解和總結(jié), 希望拋磚引玉,也許不全面, 不正確, 歡迎同學(xué)們指正和補(bǔ)充 說到數(shù)字芯片

2013-01-04 17:07:12

我大三即將轉(zhuǎn)方向了.我想去IC班,進(jìn)行數(shù)字IC的研究,請問下數(shù)字IC需要學(xué)單片機(jī)作為入門嗎(其實(shí)我不太想學(xué)).而且數(shù)字IC的paper好寫嗎

2015-11-08 07:35:54

`我大三即將轉(zhuǎn)方向了.我想去IC班,進(jìn)行數(shù)字IC的研究,請問下數(shù)字IC需要學(xué)單片機(jī)作為入門嗎(其實(shí)我不太想學(xué)).而且數(shù)字IC的paper好寫嗎?求助謝謝`

2015-11-08 18:00:34

關(guān)于ADPCM壓縮算法流程介紹

2021-06-03 06:44:13

本帖最后由 stormer 于 2017-8-27 09:05 編輯

因?yàn)槭亲鲆纛l電路,所以很多用戶會問你的產(chǎn)品是數(shù)字還是模擬的。就產(chǎn)品本身而言,肯定是數(shù)字和模擬電路都會有。所以我就把發(fā)聲IC

2017-08-27 09:03:40

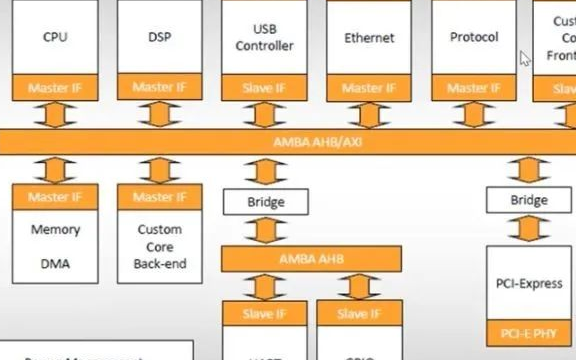

數(shù)字芯片內(nèi)部的架構(gòu)是由哪些部分組成的?數(shù)字IC設(shè)計(jì)的流程主要分為哪幾大步?每個流程使用的EDA工具有哪些?

2021-06-18 08:29:52

為什么需要低功耗設(shè)計(jì)?如何實(shí)現(xiàn)數(shù)字IC低功耗的設(shè)計(jì)?

2021-11-01 06:37:46

`需求IC與FPC貼片后的成品 測試軟件與工具,要求如下:因?yàn)?b class="flag-6" style="color: red">IC是舊IC,所以IC在貼片后需要對FPC成品進(jìn)行測試1.測試位置:FPC下面的一排金手指與IC四周的PIN角是否有開短路,如圖片2.要求測試工具1帶3,直接顯示PASS`

2020-03-23 09:44:03

《ic設(shè)計(jì)流程與使用工具介紹》我認(rèn)為IC設(shè)計(jì)流程按照功能和應(yīng)用場合不同大致可以劃分為三個部分進(jìn)行介紹,分別是數(shù)字IC、模擬IC和FPGA。這三者之間既有相同點(diǎn)又有相異點(diǎn)。在進(jìn)行設(shè)計(jì)時(shí),所使用的軟件

2013-01-07 17:10:35

數(shù)字IC后端設(shè)計(jì)-深圳 s上海 杭州崗位要求:1、對數(shù)字設(shè)計(jì)從netlist到gds流程的基本原理和概念有深刻的認(rèn)識;2、能獨(dú)立承擔(dān)百萬instance規(guī)模的數(shù)字自動布局布線工作;3、熟練

2018-08-02 16:18:53

關(guān)于時(shí)序邏輯等效性的RTL設(shè)計(jì)和驗(yàn)證流程介紹。

2021-04-28 06:13:14

溝通和合作;3、熟練使用設(shè)計(jì)工具進(jìn)行模擬IC線路設(shè)計(jì),熟悉版圖設(shè)計(jì)流程并具備相關(guān)設(shè)計(jì)能力;4、有高壓功率驅(qū)動電路開發(fā)經(jīng)驗(yàn)優(yōu)先5、碩士及以上學(xué)歷,電子專業(yè)相關(guān)數(shù)字IC設(shè)計(jì)工作職責(zé):1、 依照產(chǎn)品定義完成

2016-11-16 15:50:13

有設(shè)計(jì)師熟悉IC和晶圓的制造工藝與流程。而在經(jīng)驗(yàn)方面,模擬IC設(shè)計(jì)師需要至少3年-5年的經(jīng)驗(yàn),優(yōu)秀的模擬IC設(shè)計(jì)師需要10年甚至更長時(shí)間的經(jīng)驗(yàn)。 模擬IC設(shè)計(jì)的輔助工具少,其可以借助的EDA工具遠(yuǎn)不如數(shù)字

2016-12-26 15:06:14

`模擬IC設(shè)計(jì)流程總結(jié)`

2012-08-20 19:49:45

資深數(shù)字IC設(shè)計(jì)工程師-深圳 珠海工作職責(zé):1、 參與SOC芯片架構(gòu)設(shè)計(jì);2、 外設(shè)模塊方案設(shè)計(jì)、RTL實(shí)現(xiàn)及模塊級驗(yàn)證 ;3、 CPU、總線和外設(shè)模塊集成、仿真、FPGA驗(yàn)證和軟硬件調(diào)試;4

2014-10-10 16:20:54

還要學(xué)習(xí)具有電氣性能規(guī)劃的總體設(shè)計(jì)和布局技術(shù),不過為了得到新一代IC,這是必須要完成的變革。 更進(jìn)一步的改變是我們要努力把封裝設(shè)計(jì)作為整個芯片設(shè)計(jì)流程的一個有機(jī)組成部分。該工具的開放式架構(gòu)對這一

2010-01-28 17:34:22

芯片設(shè)計(jì)流程及工具IC的設(shè)計(jì)過程可分為兩個部分,分別為:前端設(shè)計(jì)(也稱邏輯設(shè)計(jì))和后端設(shè)計(jì)(也稱物理設(shè)計(jì)),這兩個部分并沒有統(tǒng)一嚴(yán)格的界限,凡涉及到與工藝有關(guān)的設(shè)計(jì)可稱為后端設(shè)計(jì)。前端設(shè)計(jì)的主要流程

2020-02-12 16:07:15

良好的數(shù)字電路技術(shù)基礎(chǔ),數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)者優(yōu)先;3.熟悉FPGA設(shè)計(jì)與芯片SOC設(shè)計(jì)的方法和流程;4.具有扎實(shí)的RTL級Verilog代碼的編寫能力;5.熟悉EDA工具、布線、參數(shù)提取,時(shí)序分析等一個或

2017-07-13 17:42:23

觸控ic設(shè)計(jì)工程師(數(shù)字IC/模擬IC)職位職能: 集成電路IC設(shè)計(jì)/應(yīng)用工程師 電路工程師/技術(shù)員(模擬/數(shù)字)職位描述: 職位要求: 1 、電子工程、微電子等相關(guān)專業(yè)本科以上學(xué)歷; 2

2013-04-18 17:44:52

群主好,我想請教數(shù)字電路的系統(tǒng)級設(shè)計(jì)驗(yàn)證工具及流程?即系統(tǒng)工程師常用的硬件描述語言,系統(tǒng)驗(yàn)證工具以及設(shè)計(jì)驗(yàn)證的基本流程,多謝!

2012-09-05 15:11:23

電路設(shè)計(jì)流程; 3.熟練掌握數(shù)字電路設(shè)計(jì)所需知識,如verilog用法和基本電路設(shè)計(jì)技巧; 4.熟練掌握各種設(shè)計(jì)相關(guān)EDA工具;5.樂觀積極、勇于接受挑戰(zhàn); 我的QQ:473421885電話:0755-66606920有意者簡歷可發(fā):carry.wang@yaxunhr.com

2015-06-12 15:29:09

本帖最后由 eehome 于 2013-1-5 09:47 編輯

前記:在很多電子網(wǎng)站上看到很多介紹IC或者FPGA設(shè)計(jì)工具系統(tǒng)的資料,但是感覺都不是很綜合。所以這里嘗試做一個2012

2012-12-28 17:00:22

我公司需要數(shù)字功放IC,只要能滿足電壓5-12V時(shí)能工作就行,國產(chǎn)IC也可以。請各位前輩告訴我有哪些型號的IC滿足要求。謝謝或者電話聯(lián)系我 ***

2012-09-28 16:31:32

使用集成電路設(shè)計(jì)相關(guān)EDA工具;4.熟悉IC開發(fā)流程,能熟練進(jìn)行邏輯設(shè)計(jì)、驗(yàn)證、綜合和測試;4.有成功的多款芯片流片經(jīng)驗(yàn)優(yōu)先;6.有SOC、mcu開發(fā)經(jīng)驗(yàn),熟悉MCU架構(gòu)和開發(fā)調(diào)試系統(tǒng)者優(yōu)先;7. 具備

2017-04-13 15:58:15

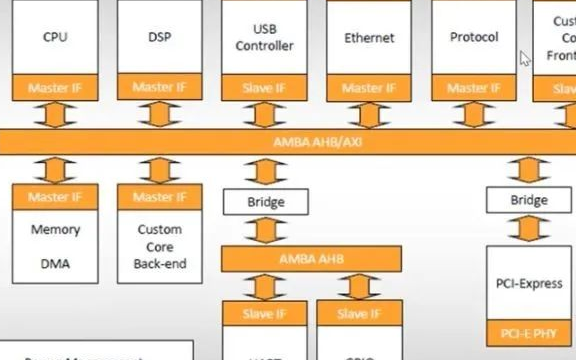

在介紹嵌入式 SoC IC 概念的基礎(chǔ)上,介紹基于重用(re-use)的 SoC IC 設(shè)計(jì)方法和流程, 涉及滿足時(shí)序要求、版圖設(shè)計(jì)流程和測試設(shè)計(jì)的問題, 并給出設(shè)計(jì)計(jì)劃考慮項(xiàng)目。

2009-05-13 16:09:42 28

28 IC封裝工藝流程圖:貼膜,磨片,貼片,裝片,鍵合,電鍍,打印,切筋等流程。

2010-07-18 10:35:26 439

439 IC設(shè)計(jì)流程圖

?

2010-02-06 16:22:26 5013

5013

集成電路設(shè)計(jì)流程 集成電路設(shè)計(jì)方法 數(shù)字集成電路設(shè)計(jì)流程 模擬集成電路設(shè)計(jì)流程 混合信號集成電路設(shè)計(jì)流程 SoC芯片設(shè)計(jì)流程

2011-03-31 17:09:12 380

380 本內(nèi)容提供了 IC卡 的分析工具,現(xiàn)簡單演示如下

2011-07-11 15:31:00 315

315 數(shù)字前端設(shè)計(jì)流程,使用PT進(jìn)行STA lSYNOPSYS Prime Time l只是一個時(shí)序分析工具,本身不對電路做任何修改。 l在ASIC流程中對于電路進(jìn)行任何修改過后都應(yīng)該使用STA工具檢查其時(shí)序,以保證電

2011-10-28 10:28:08 41

41 全書共分7章。第1章介紹了IC設(shè)計(jì)流程、常用工具的使用、Verilog設(shè)計(jì)語言;第2章介紹了時(shí)序電路的設(shè)計(jì);第3章對綜合工具DC進(jìn)行了說明,并分析了基本語言結(jié)構(gòu)的硬件實(shí)現(xiàn);第4章給出了

2011-12-02 13:41:48 0

0 EDA設(shè)計(jì)流程及其工具

2016-12-11 23:38:39 0

0 IC制造流程簡介

2016-12-21 16:48:07 668

668 IC設(shè)計(jì)流程和方法復(fù)旦講義

2017-10-18 10:13:55 22

22 一般的IC設(shè)計(jì)流程可以分為兩大類:全定制和半定制,這里我換一種方式來說明。 1.1 從RTL到GDSⅡ的設(shè)計(jì)流程: 這個可以理解成半定制的設(shè)計(jì)流程,一般用來設(shè)計(jì)數(shù)字電路。 整個流程如下(左側(cè)為流程

2017-10-20 11:38:20 25

25 常有幫助的。然而,網(wǎng)絡(luò)上似乎并沒有有關(guān)于IC設(shè)計(jì)整個流程的稍微詳細(xì)一點(diǎn)的介紹,僅僅只是概略性的說分為設(shè)計(jì)、制造、測試、封裝等四大主要板塊,有的資料介紹又顯得比較分散,只是單獨(dú)講某個細(xì)節(jié),有的只是講某個

2017-12-26 09:27:17 15380

15380

本文開始介紹了mlcc的定義與特性其次詳細(xì)的闡述了mlcc的工藝流程,最后介紹了mlcc的應(yīng)用領(lǐng)域及MLCC在IC電源中的應(yīng)用詳情。

2018-03-15 14:53:04 25239

25239 本文首先介紹了ic設(shè)計(jì)的方法,其次介紹了IC設(shè)計(jì)前段設(shè)計(jì)的主要流程及工具,最后介紹了IC設(shè)計(jì)后端設(shè)計(jì)的主要流程及工具。

2018-04-19 18:04:45 11661

11661 本文檔的主要內(nèi)容詳細(xì)介紹的是IC封裝工藝測試流程的詳細(xì)資料詳解資料免費(fèi)下載。

2018-12-06 16:06:56 132

132 視頻簡介:本視頻介紹了Microchip新推出的一款數(shù)字電源入門工具包,這款工具包采用了全新的dsPIC33EP “GS”系列器件。該器件提供雙分區(qū)閃存,這樣無需斷電便能更新電源。

2019-03-11 06:02:00 4155

4155 IC就是半導(dǎo)體元件產(chǎn)品的統(tǒng)稱,IC按功能可分為:數(shù)字IC、模擬IC、微波IC及其他IC。數(shù)字IC就是傳遞、加工、處理數(shù)字信號的IC,是近年來應(yīng)用最廣、發(fā)展最快的IC品種,可分為通用數(shù)字IC和專用數(shù)字IC。

2019-05-12 10:22:39 84240

84240 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字芯片的設(shè)計(jì)流程思路和技術(shù)說明。

2020-06-09 08:00:00 1

1 ? ? 數(shù)字IC設(shè)計(jì)流程是每個IC從業(yè)者的第一課,無論你是做前端,后端,還是驗(yàn)證,都需要對芯片的整個設(shè)計(jì)流程有個基本的了解。 本文章主要介紹以下三點(diǎn)內(nèi)容: 一. 數(shù)字IC設(shè)計(jì)的流程及每個流程需要

2020-12-09 10:12:11 6448

6448

嵌入式系統(tǒng)中數(shù)字濾波的算法及軟件流程(嵌入式開發(fā)工具軟件是什么)-嵌入式系統(tǒng)中數(shù)字濾波的算法及軟件流程 ? ? ? ? ? ? ??

2021-07-30 12:45:20 15

15 數(shù)字IC設(shè)計(jì)之“數(shù)字SOC全流程漫談從0到1”講師背景:閻如斌老師畢業(yè)于慕尼黑工業(yè)大學(xué)的碩士研究生,具有非常豐富的IC研發(fā)經(jīng)驗(yàn)。在集成電路的從業(yè)10多年之久,同時(shí)也是叩持電子和IC修真院的創(chuàng)始人

2021-11-05 20:51:02 15

15 數(shù)字IC就是傳遞、加工、處理數(shù)字信號的IC,是近年來應(yīng)用最廣、發(fā)展最快的IC品種,可分為通用數(shù)字IC和專用數(shù)字IC。數(shù)字前端以設(shè)計(jì)架構(gòu)為起點(diǎn),以生成可以布局布線的網(wǎng)表為終點(diǎn);是用設(shè)計(jì)的電路實(shí)現(xiàn)想法

2021-11-06 16:51:05 26

26 數(shù)字IC設(shè)計(jì)之DC篇:DC流程介紹綜合概念綜合是使用軟件的方法來設(shè)計(jì)硬件, 然后將門級電路實(shí)現(xiàn)與優(yōu)化的工作留給綜合工具的 一種設(shè)計(jì)方法。它是根據(jù)一個系統(tǒng)邏輯功能與性能的要求,在一個包含眾多結(jié)構(gòu)、功能

2021-11-09 20:06:00 13

13 如今,ic以更快速度、更小體量、更大容量“活躍”在人們視線中,其復(fù)雜程度遠(yuǎn)超人們想象,那么,ic開發(fā)難嗎?ic開發(fā)的流程又是怎樣的呢?

2022-05-25 16:52:03 2391

2391 數(shù)字電路設(shè)計(jì)是數(shù)字電路最為關(guān)鍵及重要的一步,今天我們將從各個流程為大家介紹完整的數(shù)字電路設(shè)計(jì)!

2022-07-10 17:14:16 6046

6046 數(shù)字IC是傳遞、加工、處理數(shù)字信號的集成電路(Integrated Circuit, IC), 一般將其分為通用數(shù)字IC和專用數(shù)字IC。

2022-09-21 10:10:05 2644

2644 瑞薩 IC 工具箱軟件手冊

2023-01-10 19:02:06 3

3 數(shù)字 IC 設(shè)計(jì)是一個程序過程,涉及將規(guī)格和功能轉(zhuǎn)換為數(shù)字塊,然后進(jìn)一步轉(zhuǎn)換為邏輯電路。許多與數(shù)字 IC 設(shè)計(jì)相關(guān)的限制來自代工工藝和技術(shù)限制。

設(shè)計(jì)技能和獨(dú)創(chuàng)性是數(shù)字 IC 設(shè)計(jì)的更高級別階段以及確保設(shè)計(jì)盡可能高效地滿足規(guī)范的系統(tǒng)和流程開發(fā)的關(guān)鍵。

2023-03-16 10:34:26 2730

2730 驗(yàn)證其實(shí)是一個“證偽”的過程,從流程到工具,驗(yàn)證工程師的終極目的都只有一個。

2023-05-31 10:34:49 1069

1069 IC設(shè)計(jì)流程從設(shè)計(jì)到驗(yàn)證是一個復(fù)雜而精細(xì)的過程,需要多個設(shè)計(jì)工具和驗(yàn)證手段的支持。不同的設(shè)計(jì)流程可能會有所差異,具體的設(shè)計(jì)流程也會根據(jù)項(xiàng)目需求和技術(shù)發(fā)展的變化而有所調(diào)整。

2023-06-27 17:07:20 264

264 瑞薩 IC 工具箱軟件手冊

2023-06-30 19:43:14 0

0 IC設(shè)計(jì)是一門非常復(fù)雜的科學(xué),在IC生產(chǎn)流程中,IC芯片主要由專業(yè)IC設(shè)計(jì)公司進(jìn)行規(guī)劃、設(shè)計(jì),如聯(lián)發(fā)科、高通、Intel等國際知名大廠,都自行設(shè)計(jì)各自專精的IC芯片,提供不同規(guī)格、效能的芯片給下游客戶選擇。

2023-07-19 08:58:59 981

981

IC設(shè)計(jì)需要掌握深入的電子學(xué)知識、半導(dǎo)體物理學(xué)、數(shù)字電路設(shè)計(jì)、模擬電路設(shè)計(jì)等多個學(xué)科領(lǐng)域的知識。此外,熟悉相關(guān)的工藝和EDA工具,以及了解芯片的設(shè)計(jì)規(guī)則和標(biāo)準(zhǔn)也是非常重要的。

2023-07-31 15:21:09 838

838 首屆IDAS設(shè)計(jì)自動化產(chǎn)業(yè)峰會將于9月18日在武漢中國光谷科技會展中心舉行。作為國內(nèi)領(lǐng)先的系統(tǒng)級驗(yàn)證EDA解決方案提供商,芯華章受邀參展,將帶來完整的數(shù)字驗(yàn)證全流程工具及客制化解決方案,與全球行業(yè)

2023-08-29 09:10:02 554

554

在IC設(shè)計(jì)中,設(shè)計(jì)師使用電路設(shè)計(jì)工具(如EDA軟件)來設(shè)計(jì)和模擬各種電路,例如邏輯電路、模擬電路、數(shù)字信號處理電路等。然后,根據(jù)設(shè)計(jì)電路的規(guī)格要求,進(jìn)行布局設(shè)計(jì)和布線,確定各個電路元件的位置和連線方式。最后,進(jìn)行物理設(shè)計(jì),考慮電磁兼容性、功耗優(yōu)化、時(shí)序等問題,并生成芯片制造所需的掩膜信息。

2023-08-30 17:07:54 1622

1622 英諾達(dá)發(fā)布了自主研發(fā)的EnFortius?凝鋒?RTL級功耗分析工具,可以在IC設(shè)計(jì)流程早期對電路設(shè)計(jì)進(jìn)行優(yōu)化。

2023-11-01 10:28:22 322

322 如今的芯片大多數(shù)都同時(shí)具有數(shù)字模塊和模擬模塊,因此芯片到底歸屬為哪類產(chǎn)品是沒有絕對標(biāo)準(zhǔn)的,通常會根據(jù)芯片的核心功能來區(qū)分。在數(shù)模混合芯片的實(shí)際工作中,數(shù)字IC與模擬IC工程師也是遵照各自的流程分別開展工作。

2023-12-20 11:29:14 162

162

電子發(fā)燒友App

電子發(fā)燒友App

評論