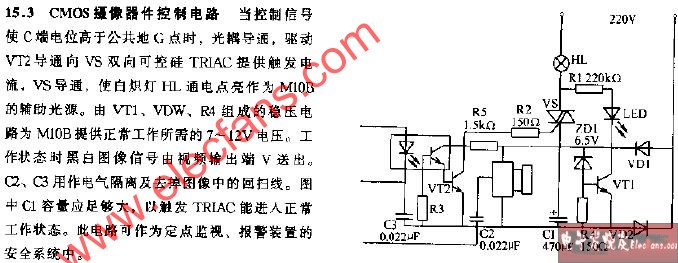

作為一個微電子專業的IC learner,這個學期也有一門課:《微電子器件》,今天我就來聊聊基本的器件:CMOS器件及其電路。在后面會聊聊鎖存器和觸發器。

今天的主要內容如下所示:

·CMOS單元電路與版圖

·CMOS門電路

·CMOS的功耗表示

老實說,CMOS比較偏微電子器件,微電子器件還真難...這里我就說一些做數字設計或許要了解的東西吧(以后要是有必要,會補充)。

1、MOS晶體管結構與工作原理簡述

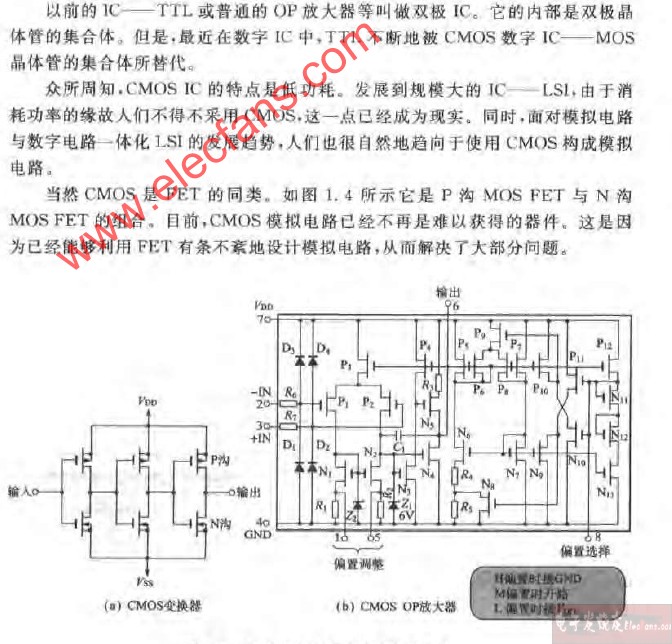

我們或多或少知道,晶體管在數字電路中的主要作用就是一個電子開關,通過電壓或者電流,控制這個“開關”開還是關。晶體管大概有兩種分類:一種是雙極性晶體管(BJT,bipolar ?junction ?transistor),另外一種是金屬-氧化物-半導體場效應晶體管(MOSFET或者MOS,metal-oxide-semiconductor ?field effect transistor)。我們這里主要來聊聊MOS了,那個BJT在現在數字IC設計中已經不是主流工藝了。

①MOS晶體管分為PMOS和NMOS,是哪一類MOS取決于襯底和摻雜濃度。至于是怎么形成的,這太復雜了,簡單的三言兩語說不清楚,這里干脆就不說了,我們直接來看他們的截面圖和簡單地講解它們的工作原理好了(以下均以NMOS為例)。

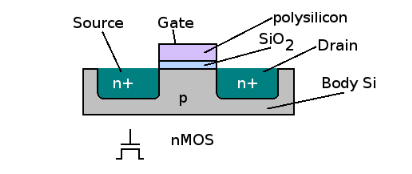

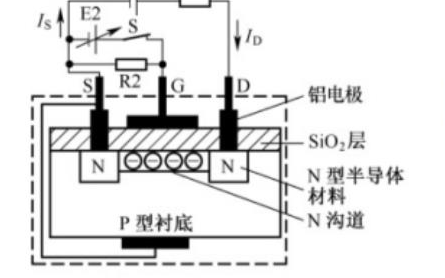

NMOS晶體管的橫截面結構如下所示:

最底層是硅晶元圓襯底(substrate)(Body Si那里),最頂上是導電的柵極(gate),中間是二氧化硅構成的絕緣層。在過去柵極是由金屬構成的,因此叫做金屬-氧化物-半導體,現在的柵極使用的是多晶硅(poly)。MOS結構中,金屬(多晶硅)與半導體襯底之間的二氧化硅會形成一個電容。

好吧,上面那一段看不懂也沒關系,也不重要,需要你記住的是,上述的NMOS晶體管中,襯底是P型的,襯底上有兩個n型的摻雜區域分別稱為源極(Source)和漏極(Drain)(其實你把左邊定義為漏而右邊定義為源也沒有問題,因為這個時候這個器件是對稱的,在連接電源和地之后,S和D才真正確定),中間最上面的稱為柵極(Gate),這就是NMOS的三個電極了(實際上的MOS是一個4端器件,它的襯底也是一個端)。下面來說一下他們怎么工作。

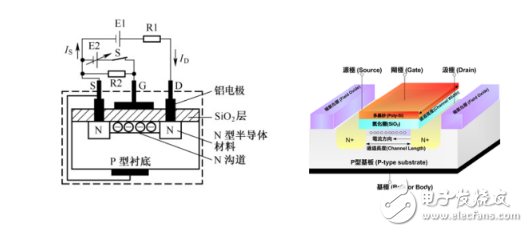

前面我們說了,晶體管的作用就是大致就是一個開關,在電流或者電壓的控制下進行開和關,對于NMOS晶體管,我們現在給它加上電壓,讓它開始工作:

? ? ? ?

?

如上左圖所示,加上電壓后,所謂的源極,就相當于電子的源頭;所謂的漏極,就相當于漏出電子的開口;而中間的柵極,就像控制開關一樣:一方面通過控制在柵極施加的高電平電壓,使源漏之間出現溝道,電子通過溝道從源極流向漏極,電流的方向也就是從漏到源了,從而進行導電,也就是“開關”打開的的時候(由于是形成的N溝道,也就是電子導電,因此成為N型CMOS)。另一方面再通過控制在柵極施加低電平電壓,讓溝道關斷,因此就源漏之間就關斷了,也就是“開關”關斷的時候。上面就是NMOS的結構和工作流程了。(PMOS的工作流程恰好相反:通過控制在柵極施加的低電平電壓,進行打開,而通過控制在柵極施加高電平電壓,讓溝道關斷。)

注意:柵極的電壓達到一定數值時,溝道才會形成,溝道形成時的電壓稱為閾值電壓(Vth)。

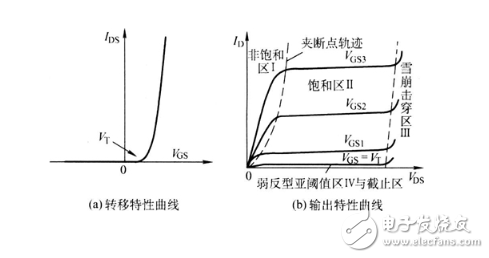

②下面我們來看一下I-V特性曲線(注意這兩個稱呼,一個是轉移特性曲線,一個是輸出特性曲線):

在前面我們知道,對于NMOS,源極(S)是接地的,漏極(D)是接數字電源的,在工作的時候,一般Vds是不變的,然后根據柵極(G)上的電壓決定溝道是否導通。工作的時候,Vg的值(也就是輸入信號的電壓值)是一個定值,要么高電平(可能有波動),要么是低電平,從這里我們也知道NMOS工作的時候,是有電流從電源(VDD)流到地(GND)的(也就是從D流到S的),在電源電壓不變的時候,這個電流隨著柵極上的電壓增大而增大。

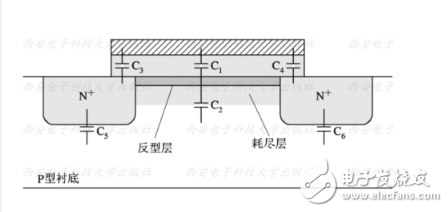

③接著我們看看MOS的內部自個形成的電容(寄生電容),如下圖所示:

主要分為:

(1)柵和溝道之間的氧化層電容C1;

(2)襯底和溝道之間的耗盡層電容C2;

(3)多晶硅柵與源和漏的交疊而產生的電容C3?和C4;

(4)源/漏區與襯底之間的結電容C5與C6。

好吧,其實這些個MOS這個電容我們看看就好了,畢竟我們不是做器件的。

2、CMOS單元電路與版圖

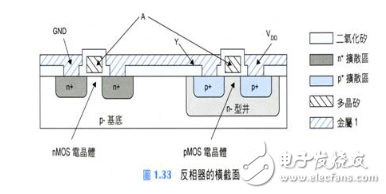

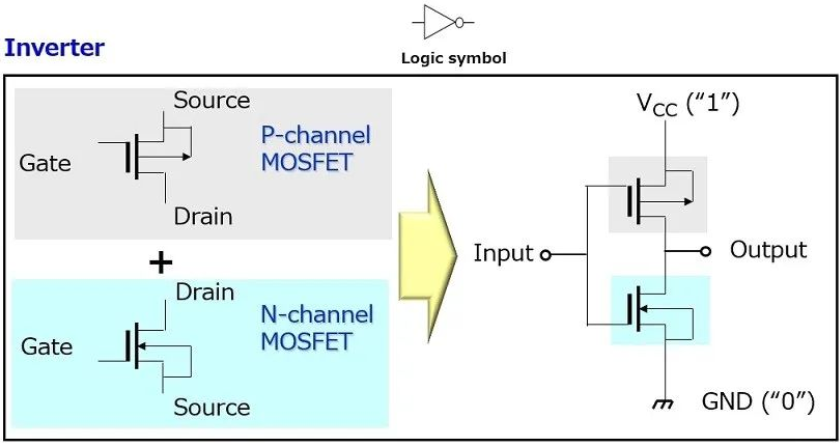

在現在工藝中,我們主要使用的是成為CMOS(互補型半導體,Complementary MOS)的工藝,這種工藝主要就是把PMOS和NMOS這兩類晶體管構成一個單元,稱為CMOS單元或者反相器單元,其結構把PMOS和NMOS同時集成在一個晶元上然后柵極相連,漏極相連,下面是它的結構圖(關于電路符號和功能將在后面講):

在上圖中,左邊是NMOS,右邊是PMOS。A是共連柵極輸入,Y是共連漏極輸出,VDD連接PMOS的源極,GND連接GND。

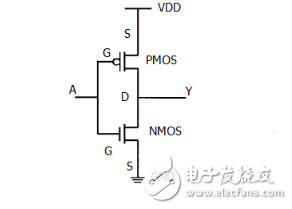

下面電路符號圖了,上面的那個CMOS反相器對于的電路符號圖如下所示:

現在我們就來分析一下這個CMOS反相器的工作原理來說明這個為什么CMOS工藝是主流吧:

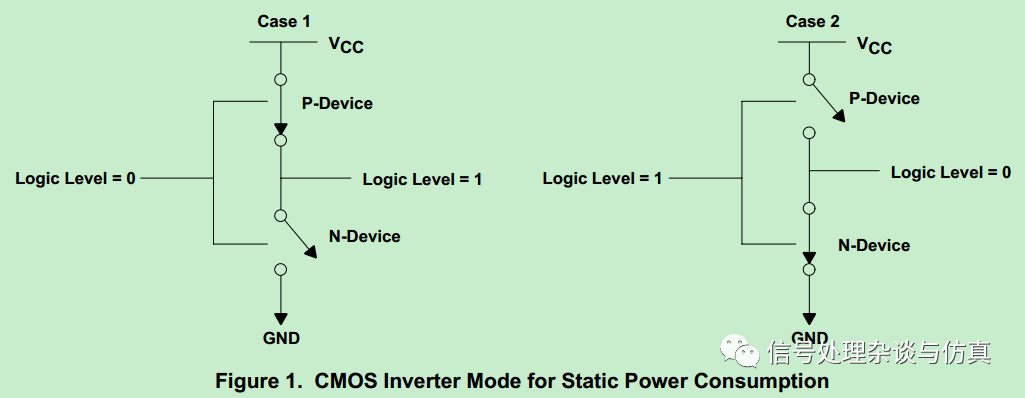

A當輸入信號A=1時,PMOS關斷,NMOS打開,輸出信號Y的電壓相當于GND的電壓,也就是Y=0;在這個過程中,從VDD到GND這一個供電回路都沒有導通,因此理論不存在電流從VDD流到GND,因此功耗為0.

B當輸入信號A=0時,PMOS打開,而NMOS關閉,輸出信號Y=VDD=1,但是從VDD到GND這一個供電回路也沒有導通,因此理論上也不存在電流從VDD流到GND,因此功耗也為0。

C因此可以得出,理論上反相器進行傳輸信號時,沒有功耗(好吧,我們應該這樣說:功耗極其地低),這就是為什么使用CMOS的工藝的原因。

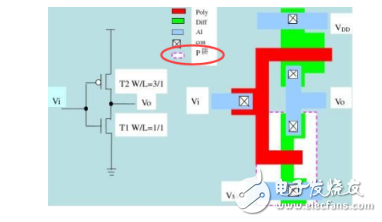

下面我們來看一下CMOS單元的版圖:

左邊是CMOS的電路符號,右邊是版圖(這個版圖先湊合著看),下面來說一下這個版圖吧:

首先是從下往上看,金屬(藍色)連接到數字地(Vss)上面;白色背景紅色虛線邊框的P阱區域是為說明,下面的綠色摻雜區域形成的是NMOS,上面綠色摻雜區域形成的是PMOS;

然后 ??綠色的摻雜區域 ?分布在 ?紅色的多晶硅附近,然后多晶硅連在一起(也就是把PMOS和NMOS的柵極連在一起),然后通過金屬引出(那個X表示通孔)為輸入Vi。

然后下面的NMOS的源極通過通孔跟金屬連在一起(綠色跟藍色通過X連在一起);NMOS和PMOS的漏極通過通孔連接到同一塊金屬上面然后當做輸出。

PMOS的源極通過通孔連接到金屬然后連接到了數字電源上。

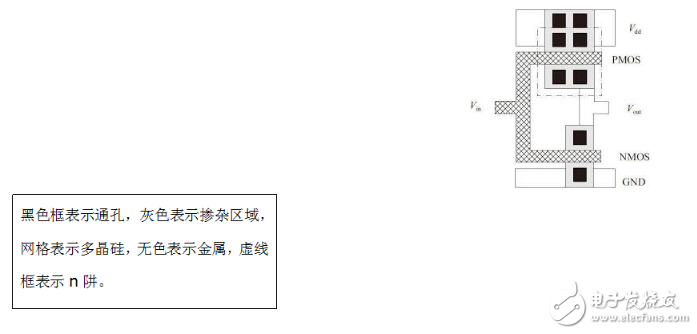

更加抽象(好看一點)的圖如下所示:

版圖的基本知識就到這好了,更詳細的知識還是查看更專業的書籍吧。

3、CMOS門電路

①CMOS非門:上面的一個CMOS單元的功能就是非門的功能了,因此CMOS非門也就是這個CMOS的單元,也稱為反相器。其電路結構就是反相器的電路結構。

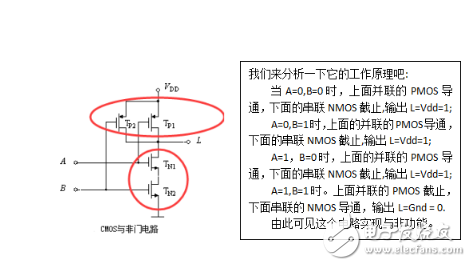

②(二輸入)CMOS與非門(NAND):

直接上圖吧,CMOS與非門的電路符號結構如下所示:

(PMOS的電路符號柵極處本來應該有個小圈圈,表示低電平有效的)

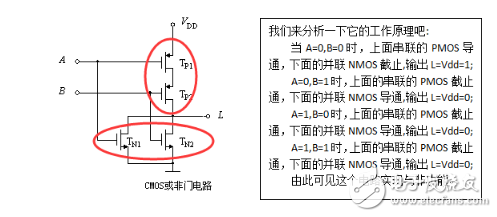

③(二輸入)CMOS或非門(NOR)的電路符號和工作原理如下所示:

(PMOS的電路符號柵極處本來應該有個小圈圈,表示低電平有效的)

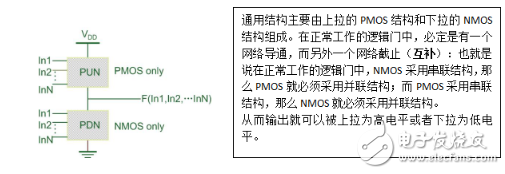

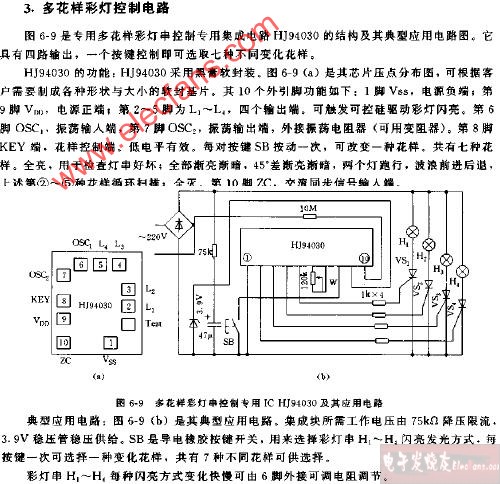

數字邏輯電路都可以由上面的三種電路化簡構成,也就是說一個電路可以由NAND或者NOR電路構成,我們來看看他們的特點來推導數字CMOS電路的特點。

容易知道(反正我們就當做結論好了):

反相邏輯門的通用結構如下所示:

此外我們也注意到,使用到與功能的時候,NMOS網絡是串聯的;使用或功能時,NMOS網絡是并聯的。因此可以這么記憶:要NOMS都一起,才能一起(與),只要NMOS其中一個就可以(或),與還是或,可以根據NMOS的串并結構判斷。

然后設計多少個輸入的NXXX門,就把多少個NMOS串/并聯起來,然后PMOS就是并/串就可以了。

4、CMOS的功耗表示

功耗是單位時間內消耗的能量,在數字系統中的功耗主要包括靜態功耗和動態功耗,我們將從CMOS電路角度聊聊靜態功耗和動態功耗。

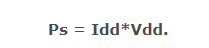

CMOS的靜態功耗:當CMOS不翻轉/不工作時的功耗。在CMOS都不工作時,也就是晶體管都處于截止狀態的時候,從VDD到GND并不是完全沒有電流流過的,還是有些微電流從電源流到地,這個靜態電流Idd稱為電源和地之間的漏電流,跟器件有關(至于漏電流是怎么引起的,這里就不再闡述了)。初中的時候,我們就學過P=UI,因此靜態功耗就可以這樣表示?:

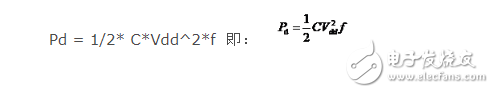

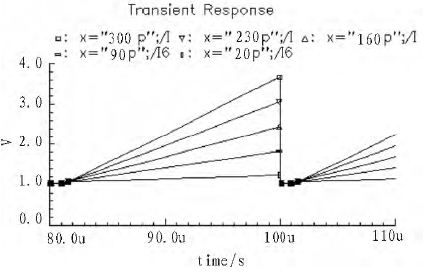

CMOS的動態功耗是信號在0和1變化之間,電容充放電所消耗的功耗。我們知道,不僅僅CMOS器件有寄生電容,導線間也有電容。將電容C充電到電壓Vdd所需要的能量CVdd^2。如果電容每秒變換f次(也就是電容的切換頻率為f,在一秒內,電容充電f/2次,放電f/2次),由于放電不需要從電源那里獲取功耗,因此動態功耗就可以這樣表示:

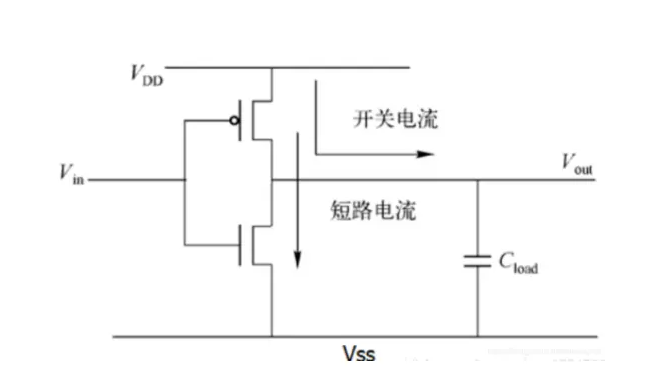

PS:上面主要是列舉了一些主要的功耗,比如動態功耗中除了翻轉時電容消耗功耗外,還有在柵極信號翻轉的時候PMOS和NMOS同時導通引起的短路功耗。

這里不一一陳述,主要是考慮上面的那兩種功耗。也許后面記載低功耗設計的時候會詳細說明一下。

電子發燒友App

電子發燒友App

評論