全球電子設計創新企業Cadence設計系統公司日前宣布其與TSMC在3D IC設計基礎架構開發方面的合作。

2012-06-11 09:47:43 1071

1071 楷登電子今日正式發布Cadence? Virtuoso?定制 IC設計平臺的技術升級和擴展,進一步提高電子系統和 IC設計的生產力。新技術涉及Virtuoso 系列幾乎所有產品,旨在為系統工程師提供更穩健的設計環境和生態系統,助其實現并分析復雜芯片、封裝、電路板和系統。

2018-04-11 16:40:16 9290

9290 Cadence Integrity 3D-IC 平臺是業界首個全面的整體 3D-IC 設計規劃、實現和分析平臺,以全系統的視角,對芯片的性能、功耗和面積 (PPA) 進行系統驅動的優化,并對 3D-IC 應用的中介層、封裝和印刷電路板進行協同設計。

2022-05-23 17:13:53 4218

4218 這是一個業界用于打造差異化定制芯片的領先平臺,可借助生成式 AI 技術顯著提升設計生產力; Virtuoso Studio 與 Cadence 最前沿的技術和最新的底層架構集成,助力設計工

2023-04-20 15:52:13 508

508

各位大佬好,我正在學習IC設計,對于Cadence Virtuoso這個軟件有一些入門級的小問題:我從AnaglogLib拷貝NMOS管和PMOS管到自己的library下面,打開他們的CDF參數看

2017-10-16 00:26:33

Cadence設計系統公司發布了Cadence Allegro系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強。改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

業界首個用于多芯片設計和高級封裝的綜合性的 3D-IC 設計平臺,其主要亮點有: Integrity 3D-IC 將設計規劃、實施和系統分析集成在一個統一的座艙中設計人員可以通過集成的散熱、功率消耗

2021-10-14 11:19:57

:“我們選擇Cadence作為我們RFSiP技術的合作伙伴,因為Cadence有相應的技術和能力,能夠和我們共同制定一套在FREESCALE能被廣泛采用的解決方案,從而顯著提升我們的RFSiP技術

2008-06-27 10:24:12

Cadence設計系統公司發布Cadence?Allegro?系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強.改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-08-28 15:28:45

Cadence設計系統公司發布Cadence?Allegro?系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強.改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2008-06-19 09:36:24

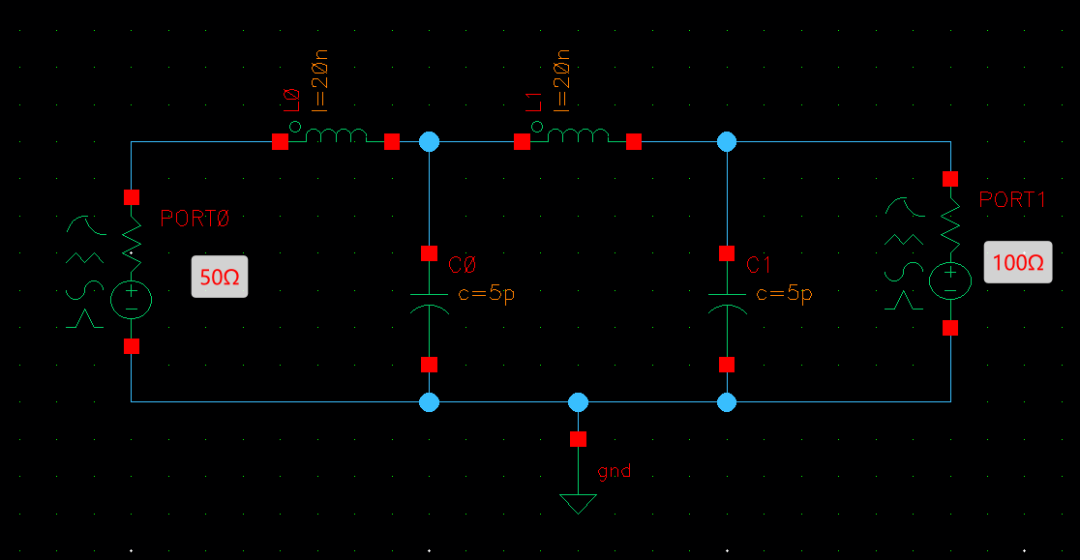

電路工作到了后期需要匯報或者寫文章需要設計原圖 ,這里整理一下Cadence設計原理圖常用導出方案。 前期工具用的好,后期處理沒煩惱,Cadence自帶工具其實很強大,只是你沒嘗試用。 仿真環境:虛擬機Linux下Cadence617 原理圖繪制工具:virtuoso

2021-01-15 07:48:05

cadence virtuoso教程? 1990-2006 Cadence Design Systems, Inc. All rights reserved.Printed

2012-08-10 18:37:59

由于skill 語言提供編程接口甚至與<br/>C 語言的接口所以可以以Cadence 為平臺進行擴展用戶還可以開發自己的<br/>

2008-07-12 23:11:21

cadence講義_IC設計_清華微電子所

2012-08-12 17:30:13

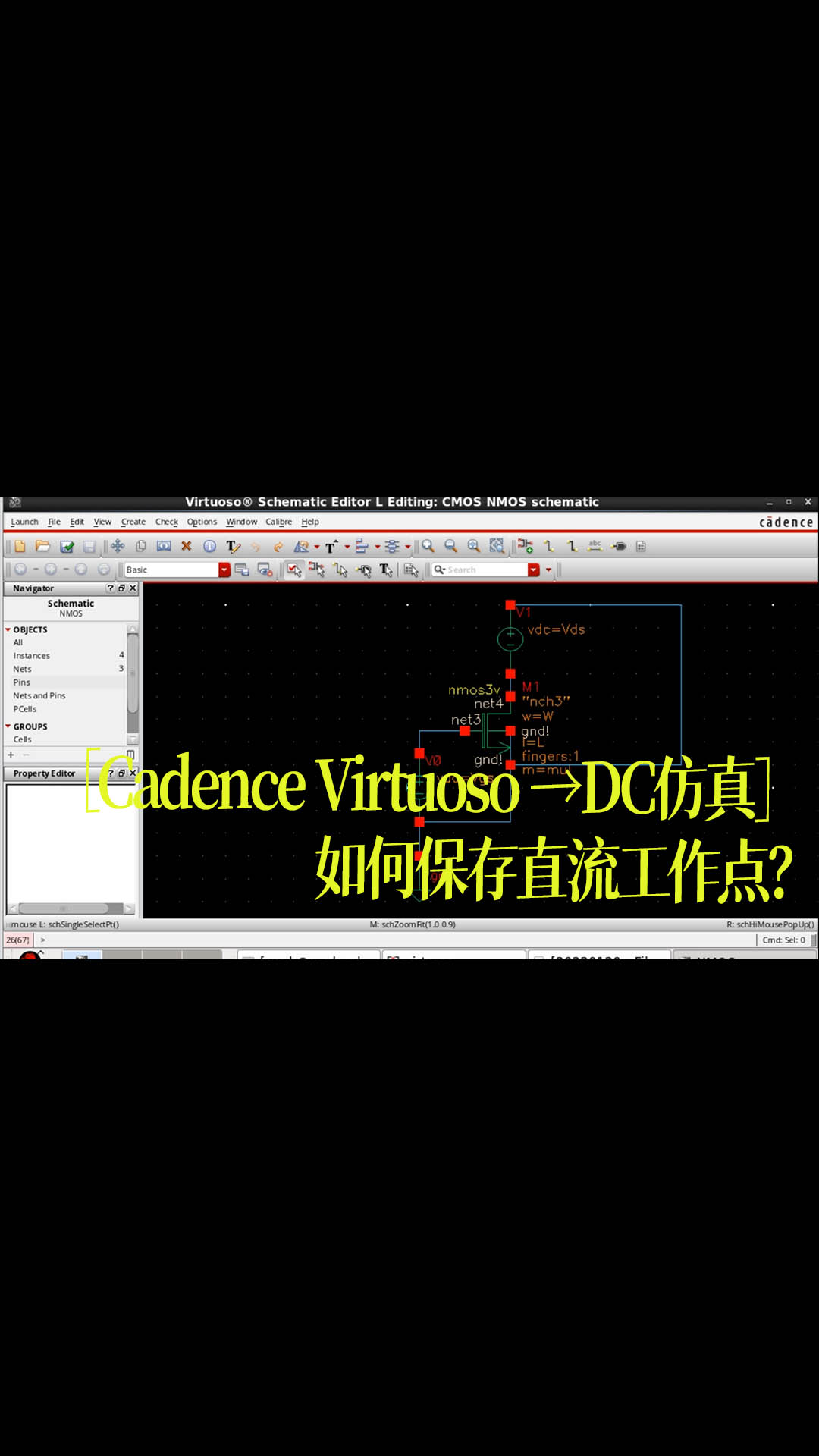

or subcircuit, `nmos_6p0'. Either include the。。。。仿真前需要設置model libraries,這個怎么設置啊。我用的是virtuoso 6.1.7

2018-07-19 20:16:30

大家好,本人剛入ic行,這幾天用virtuoso畫版圖在LVS檢測過程中出現了如圖所示的報錯,有沒有哪位大神知道怎么改,麻煩賜教,很急謝謝!

2017-07-25 17:17:22

自動白平衡的FPGA實現采用FPGA對自動白平衡進行運算有什么優點?

2021-04-13 06:20:46

加密芯片的特點,區分位兩大方案,即單片機與加密IC固定算法認證的模式和單片機中的部分代碼移植到加密IC中的模式。從目前的加密效果看,采用智能卡平臺的加密芯片,使用客戶自定義算法移植的加密模式,被證明

2011-04-08 14:31:03

LED實現白光有哪幾種方式?采用熒光粉來制作彩色LED有什么優點?

2021-06-01 06:18:35

組件架構的一個優點就是應用可以隨時間的流逝而發展進化。除此之外,使用組件還有一些可以使對以有應用的升級更加 方便和靈活的優點,如應用的定制,組件庫以及分布式組件等。

2020-03-11 09:01:29

本帖僅致那些跟我一樣奮斗在安裝路上的小白們,過程很辛苦,所以寫下來,讓之后安裝的人有個參考,節省點時間為了安裝cadence ic5141 ,可謂是嘔心瀝血,歷經萬難前后十天,除了每天睡覺,重要的課

2013-05-28 23:43:37

的迭代方法大大提升。 完全集成于Cadence Virtuoso? 平臺,提供統一的設計流程,提升了設計人員在模擬和定制模塊進行EMIR簽收的工作效率。 利用了Cadence Quantus QRC寄生

2018-09-30 16:11:32

深圳WINCE專業平臺開發團隊,我們致力提供WINCE平臺的硬件定制,內核驅動定制一條龍服務:********三星平臺************ARM9(S3C2440,S3C2416,S3C2451

2010-04-12 09:46:25

請問給位大佬,我這有一款1621(lcd驅動)的原理,我需要仿真芯片功能,對于ic需要的讀寫時序怎么提供?我實在cadence virtuoso上操作。謝謝

2018-07-16 13:51:50

二極管的主要參數有哪些?單相電風扇采用電子式調速器有何優點?

2021-09-27 08:39:55

基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖該如何去設計?怎樣去驗證一種基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖?

2021-06-22 06:12:49

基于Cadence的IC設計

2012-08-16 16:51:16

的設計平臺。在綜合比較后,本文選定了CadenceVirtuoso全定制IC設計工具。VirtUOSO是Cadence公司推出的用于模擬/數字混合電路仿真和射頻電路仿真的專業軟件。基于此平臺

2018-11-26 10:56:11

您是否正在使用Cadence Virtuoso進行功率放大器設計?您想運行信封跟蹤模擬嗎?包絡跟蹤是一種響應于調制的RF輸入信號的功率電平來調整功率放大器的偏置電壓以獲得更高效率的方法。已在

2019-02-21 16:18:37

布局結構,最后根據芯片內各個信號的關系來進行電路布線的操作。以上的操作都可以在Cadence的IC 5.1集成設計環境下的Virtuoso中完成,當完成布局布線后全定制Asic的版圖基本就確定了,然后

2013-01-07 17:10:35

打開virtuoso的一些功能一、Connectivity --> Mark net 如圖所示,此功能就是可以選中相關連的層(通常大家會采用skill 來達到這一功能),這里講的是調用tech

2018-11-26 16:20:19

招兼職Cadence,IC設計等各類相關講師,要求有一定項目經歷,表達能力強,待遇高,可周末,有意者請與我聯系。地點北京, QQ:1489302364,郵件:hailang869@163.com,羅先生

2012-03-30 10:44:10

ACS712是什么?線性電流傳感器IC ACS712的特色和優點有哪些?

2021-09-30 09:10:50

Cadence Virtuoso與PCB設計軟件,如Altium Designer等; 4.對天線、基帶均有一定了解,具備系統級分析能力,能就實際產品性能問題優化射頻電路的設計,提供解決方案; 5.熟練掌握

2015-07-03 18:01:37

本文介紹了一種MEMS 器件設計,及在Cadence Virtuoso 設計環境與集成電子產品一起仿真的新方法。采用德州儀器的數字微反射鏡器件(DMD)的例子,我們展示新的MEMS - IC 設計方法如何可

2010-09-23 11:42:15 0

0 Cadence Allegro SiP and IC Packaging 16.3版推出

Cadence設計系統公司宣布,利用最新的系統封裝(SiP)和IC封裝軟件,封裝設計者將在芯片封裝協同設計過程中和整個半導體設計鏈中

2009-11-04 08:52:51 1826

1826 芯邦采用Cadence Incisive Xtreme III系統提升SoC驗證實效

全球電子設計創新領先企業Cadence設計系統公司今天宣布,位于中國深圳的、無晶圓廠集成電路設計領先企業芯邦科

2010-03-02 10:32:47 573

573 意法推出新評估平臺Cadence OrCAD PSpice

意法半導體宣布成功開發一個新的評估平臺,客戶可以仿真意法半導體先進的模擬和功率芯片。Cadence® OrCAD®, PSpice®是一項穩健

2010-04-13 10:53:50 970

970 電子設計創新企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,中國科學院計算技術研究所(簡稱計算所)采用了Cadence? Incisive?Xtreme Ⅲ? 系統,來加速其下一代6400萬門以上龍芯3號高級多

2011-05-27 10:49:34 646

646 Giantec最近采用Cadence軟件設計并成功流片了一款用于低功耗微控制器的存儲器產品,這款低功耗微控制器應用于智能卡、智能電表和消費電子產品。

2011-09-22 18:08:05 896

896 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence? Virtuoso?統一定制/模擬(IC6.1)以及Encounter?統一數字流程生產其混合信號芯片。

2011-09-27 11:06:26 1483

1483 本章是Cadence IC 5.1.41 是設計 的簡明入門教程,目的是讓讀者在剛接觸該軟件的時候對它的基本功能有一個總體的了解。本章主要內容如下:[1] 啟動Cadence IC 前的準備;[2]Command Interpret

2011-12-02 16:56:58 158

158 全球EDA領導廠商SpringSoft今天宣布,現即提供Laker3?定制IC設計平臺與模擬原型(Analog Prototyping)工具。

2012-04-25 14:46:43 2346

2346

Cadence 設計系統公司日前宣布,汽車零部件生產商Denso公司在改用了Cadence定制/模擬與數字流程之后,在低功耗混合信號IC設計方面實現了質量與效率的大幅提升。將Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 909

909 Cadence教程:基于Cadence的IC設計

2013-04-07 15:46:14 0

0 為專注于解決先進節點設計的日益復雜性,全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布,臺積電已與Cadence在Virtuoso定制和模擬設計平臺擴大合作以設計和驗證其尖端IP。

2013-07-10 13:07:23 842

842 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布推出用于實現電學感知設計的Virtuoso?版圖套件,它是一種開創性的定制設計方法,能提高設計團隊的設計生產力和定制IC的電路性能。

2013-07-15 17:13:14 2080

2080 基于Wide I/O接口的3D堆疊,在邏輯搭載存儲器設計上進行了驗證 ,可實現多塊模的整合。它將臺積電的3D堆疊技術和Cadence?3D-IC解決方案相結合,包括了集成的設計工具、靈活的實現平臺,以及最終的時序物理簽收和電流/熱分析。

2013-09-26 09:49:20 1346

1346 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,海思半導體(HiSilicon Semi)進一步擴大采用Cadence? Palladium? XP 驗證運算平臺作為其仿真方案,運用于移動和數字媒體System-on-Chip (SoC) 與 ASIC開發。

2014-05-13 16:19:03 2137

2137 美國加州圣何塞,2014年9月30日 ─ 全球知名的電子設計創新領導者Cadence設計系統公司(NASDAQ: CDNS)今日宣布其豐富的IP組合與數字和定制/模擬設計工具可支持臺積電全新的超低功耗(ULP)技術平臺。

2014-10-08 19:24:35 907

907 基于cadence IC5141差分放大器的設計spectre仿真與layout繪制1

2016-02-19 16:43:05 175

175 IC design 集成電路的設計流程以及cadence的簡介,使用方法和入門須知。

2016-03-14 14:11:33 25

25 4月15日,中國上海—楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日宣布Cadence? Virtuoso? 版圖依賴效應(Layout-Dependent Effects

2016-04-15 10:09:07 1939

1939 2017年1月5日,中國上海 —— 楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日與國家集成電路設計北京產業化基地—中關村芯園(北京)有限公司聯合宣布,雙方將簽訂平臺合作協議,將Cadence最前沿的設計工具平臺和創新技術注入到中關村芯園的集成電路公共服務平臺之中。

2017-01-05 15:06:07 1252

1252 2017年4月18日,中國上海 – 楷登電子(美國Cadence公司,NASDAQ: CDNS)今日正式發布針對7nm工藝的全新Virtuoso? 先進工藝節點平臺。通過與采用7nm FinFET

2017-04-18 11:09:49 1165

1165 (Virtuoso系統設計平臺),結合Cadence Virtuoso平臺與Allegro? 及Sigrity?技術,打造一個正式的、優化的自動協同設計與驗證流程。

2017-06-13 14:26:28 2937

2937 電路、對基帶低頻大信號有高線性度要求的模塊、發射端大電流的PA 模塊、鎖相環頻率綜合器中的數字塊,以及非線性特性的VCO等各具特點的電路。眾多的電路單元及其豐富的特點必然要求在這種系統的設計過程中有一個功能豐富且強大的設計平臺。在綜合比較后,本文選定了Cadence Virtuoso 全定制IC 設計工具。

2018-06-06 09:37:00 10797

10797

選項、Spectre電路模擬器、Voltus-Fi客制電源完整性解決方案、Pegasus驗證系統以及VirtuosoR客制IC設計平臺,其中包括Virtuoso布局套裝EXL、Virtuoso原理圖編輯器及Virtuoso ADE產品套裝。

2019-05-07 16:29:20 2491

2491 加利福尼亞州圣何塞 , Dec。 1,2015 /PRNewswire/- 凱德斯設計系統公司(納斯達克股票代碼:CDNS)今天宣布推出新的Virtuoso?Advanced-Node平臺,該平臺

2019-08-08 15:40:13 982

982 cadence 公司 IC5141 工具主要包括集成平臺 design frame work II、原理圖編輯工具 virtuoso schematic editor、仿真工具、版圖編輯工具

2020-07-21 08:00:00 3

3 安裝Cadence IC617+MMSIM151+Calibre的IC設計環境

2021-04-07 09:08:10 9

9 Cadence 3D-IC Integrity 平臺在統一的環境中提供 3D 芯片和封裝規劃、實現和系統分析。

2021-10-28 14:53:35 2114

2114 這篇博客記錄一下virtuoso中進行CMOS反相器和靜態寄存器的電路設計以及功能仿真,適合入門。還做了版圖設計,但是自己對原理不是不清楚,在此就不記錄了。virtuoso電路設計環境基本教學

2021-11-07 10:21:01 36

36 創建邏輯內存器件的 3D 堆疊配置,優化 3D 堆疊設計的 PPA 結果。 客戶可以放心采用 Cadence Integrity 3D-IC 平臺和 Samsung Foundry 的多 Die 實現

2021-11-19 11:02:24 3347

3347 與 Cadence 資深技術專家,涵蓋最完整的先進技術交流平臺,從封裝和板級設計,系統分析方案到定制/模擬設計,覆蓋設計全流程的技術分享。您也將有機會和開發 Cadence 工具的技術專家們面對面的直接溝通。

2021-12-09 09:55:55 1599

1599 中國上海,2022年4月21日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Cadence? Fidelity? CFD 軟件平臺,為多物理場仿真的性能和準確度開創新時代。

2022-04-21 11:36:50 1955

1955 基于Cadence的IC設計

2022-05-31 17:11:24 0

0 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其數字和定制 / 模擬設計流程已獲得 TSMC N3E 和 N4P 工藝認證,支持最新的設計規則手冊(DRM)。

2022-06-17 17:33:05 4800

4800 設計。得益于兩家企業的持續合作,使用 Cadence Integrity 3D-IC 平臺的參考流程現已啟用,以推進 Samsung Foundry 的 3D-IC 設計方法。使用 Cadence 平臺

2022-10-25 11:05:04 621

621 聯華電子(NYSE:UMC;TWSE:2303)與楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平臺的 Cadence 3D-IC 參考工作流程已通過聯電的芯片堆棧技術認證,將進一步縮短產品上市時間。

2023-02-03 11:02:23 1417

1417 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,瑞薩電子(Renesas Electronics)已采用全新的人工智能(AI)驅動的 Cadence Verisium 驗證

2023-03-15 09:07:00 539

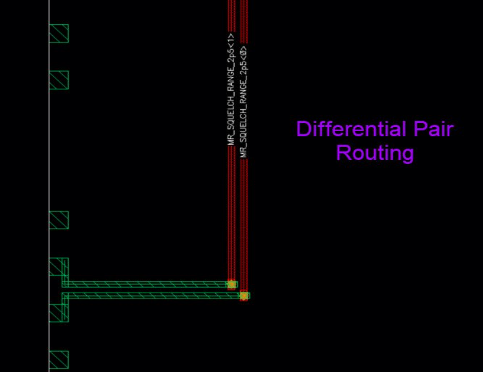

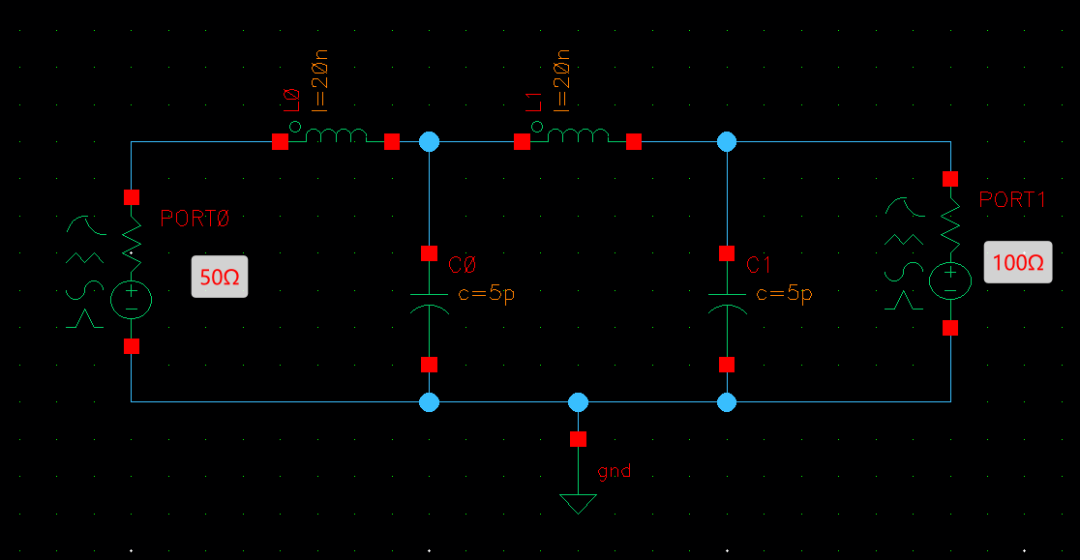

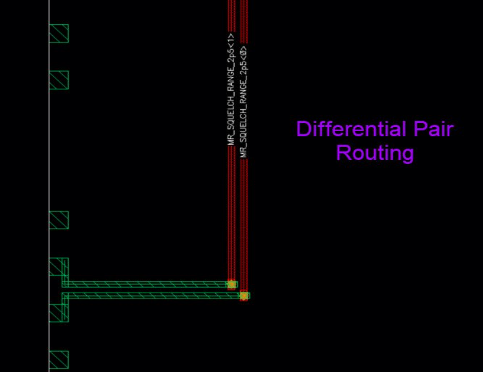

539 交互式路由允許您在自動路由之前完成關鍵網絡,并在自動路由后完成未布線的不完整網絡。Virtuoso 交互式和輔助路由功能允許您在 Virtuoso 環境中以交互方式路由連接,以滿足關鍵的設計約束和規則。在所有工藝節點上啟用交互式和自動布線功能,包括最先進的工藝技術。

2023-04-20 10:58:23 2071

2071

,包括最新的 N3E 和 N2 工藝技術。這一新的生成式設計遷移流程由 Cadence 和臺積電共同開發,旨在實現定制和模擬 IC 設計在臺積電工藝技術之間的自動遷移。與人工遷移相比,已使用該流程的客戶成功地將遷移時間縮短了 2.5 倍。

2023-05-06 15:02:15 801

801 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Integrity 3D-IC 平臺的新設計流程,以支持 TSMC 3Dblox 標準。TSMC

2023-05-09 09:42:09 615

615 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發

2023-05-09 10:09:23 708

708 了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-06-13 12:15:02 557

557

●?Samsung Foundry 有眾多 PDK 系列,可搭配 Virtuoso Studio 用于簡化模擬、定制和射頻設計,最高支持 SF 2nm 技術 ●?Virtuoso Studio

2023-06-30 10:08:30 681

681 內容提要 1 輕松實現節點到節點的設計和 layout 遷移 2 將定制/模擬設計遷移速度提升 2 倍 3 Cadence Virtuoso Studio 針對所有 Samsung Foundry

2023-07-04 10:10:01 471

471 已經過 SF2 和 SF3 流程認證 ●? Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ● Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 已經過 SF2 和 SF3 流程認證 ●?Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ●Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已針對

2023-07-05 10:12:14 381

381 平臺支持 Samsung 新的 3D CODE 標準,助力設計人員創建多種先進的封裝技術。 ?? Cadence 和 Samsung 的技術為客戶提供全面、定制化的解決方案。適用于能夠縮短 3D-IC

2023-07-06 10:05:04 329

329 了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-07-11 12:15:02 241

241

了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-09-01 12:20:01 413

413

Cadence Virtuoso定制設計平臺的一套全面的集成電流(IC)設計系統,能夠在多個工藝節點上加速定制IC的精確芯片設計,其定制設計平臺為模擬、射頻及混合信號IC提供了極其方便、快捷而精確的設計方式。

2023-09-11 15:14:16 3199

3199

本篇文章將講述如何在Cadence IC中使用ADE GXL對電路進行優化設計。

2023-09-11 16:07:01 1388

1388

● AI 驅動的 Cadence Virtuoso Studio 助力 IC 設計在 TSMC 的制程技術之間實現遷移時自動優化電路 ●? 新的生成式設計技術可將設計遷移時間縮短

2023-09-27 10:10:04 301

301 和移動 IC 中國上海,2023 年 10 月 10 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布其數字和定制/模擬流程已通

2023-10-10 16:05:04 270

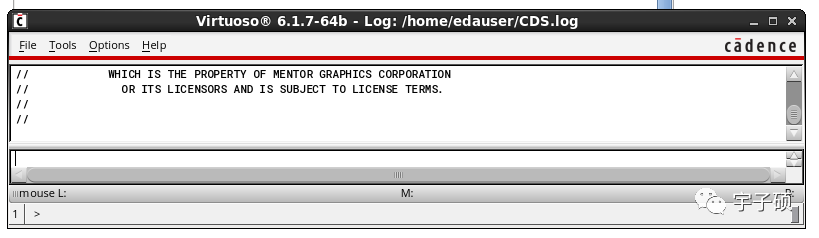

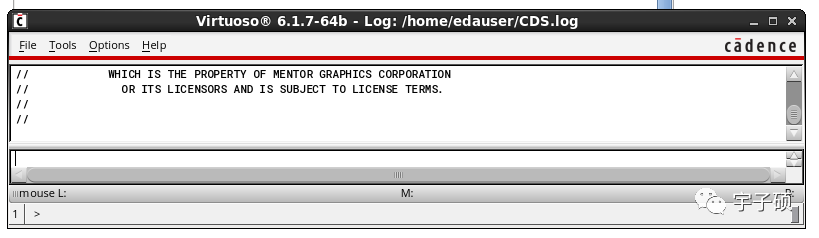

270 首先,在相應終端下鍵入virtuoso,啟動后出現以下窗口。

2023-10-18 15:47:46 742

742

雙方的共同客戶可獲取 Cadence 的全流程系統級設計驗證和實現解決方案以及接口 IP,依托 Neoverse CSS 加速開發基于 Arm 的定制 SoC 中國上海,2023 年 10 月 25

2023-10-25 10:40:02 197

197

基于Cadence的IC設計

2022-12-30 09:21:19 6

6 基于 Cadence 30 年的行業知識和領先地位,全新人工智能定制設計解決方案 Virtuoso Studio 采用了多項創新功能和新的基礎架構,實現無與倫比的生產力,以及超越經典設計界限的全新集成水平。在本文中,您將了解優異的模擬設計工具如何變得更好,并助您解決挑戰性的設計問題。

2024-01-09 12:22:02 445

445

電子發燒友App

電子發燒友App

評論