一、項(xiàng)目背景

LED燈的理論、教學(xué)板的原理圖,已經(jīng)在案例1位閃爍燈中有詳細(xì)的描述,在此不再講述,有興趣的讀者可以返回去閱讀。

二、設(shè)計(jì)目標(biāo)

本工程使用4個(gè)LED燈---LED1~LED4,實(shí)現(xiàn)一個(gè)呼吸燈的功能。這4個(gè)燈具體的變化情況為:

第1個(gè)燈隔1秒后,亮1秒;然后第2個(gè)燈隔1秒后,亮2秒;然后第3個(gè)燈隔1秒后,亮3秒,最后第4個(gè)燈隔1秒,亮4秒。如此循環(huán)往復(fù)。

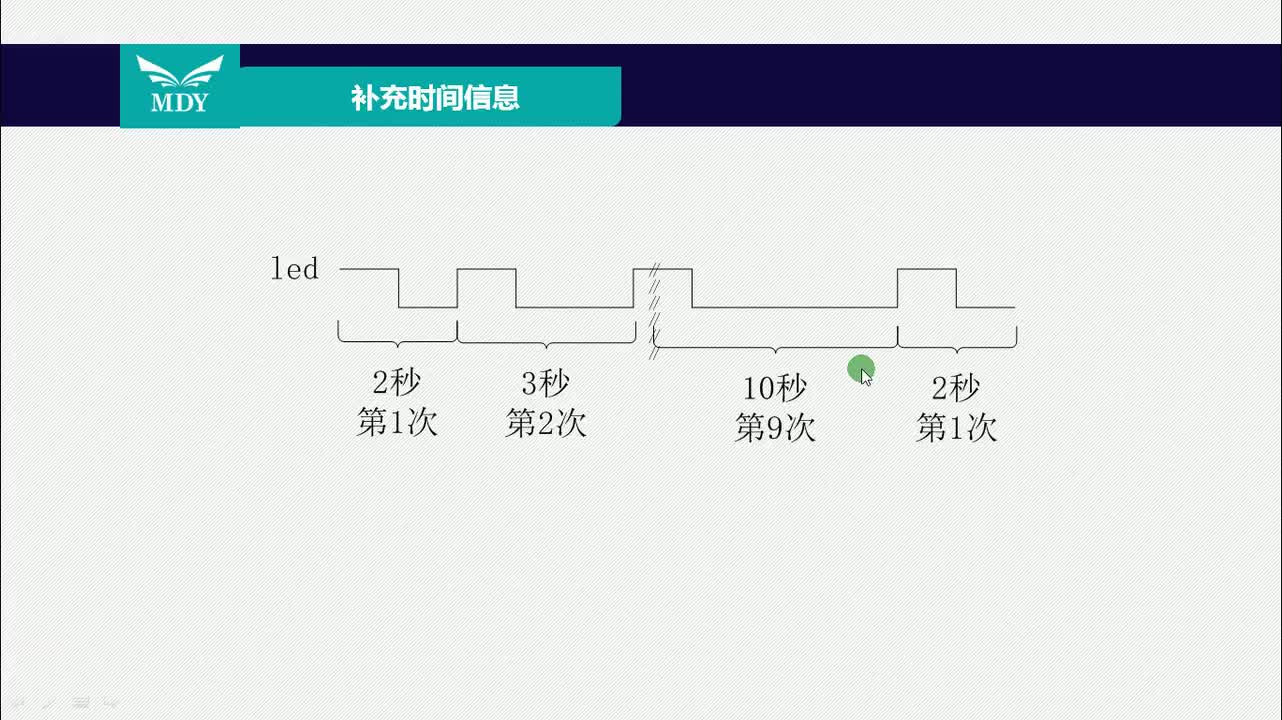

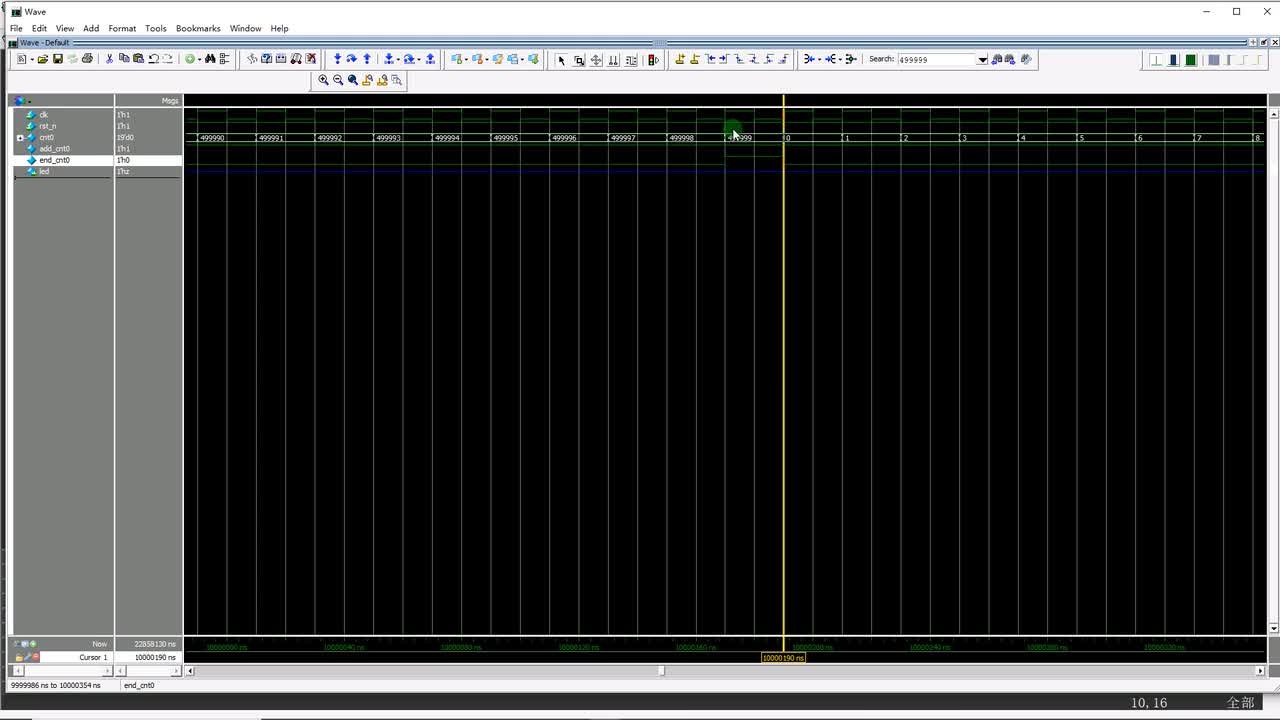

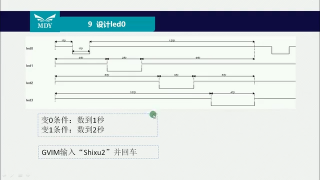

下面是波形圖:

上板效果圖如下圖所示。

三、模塊設(shè)計(jì)

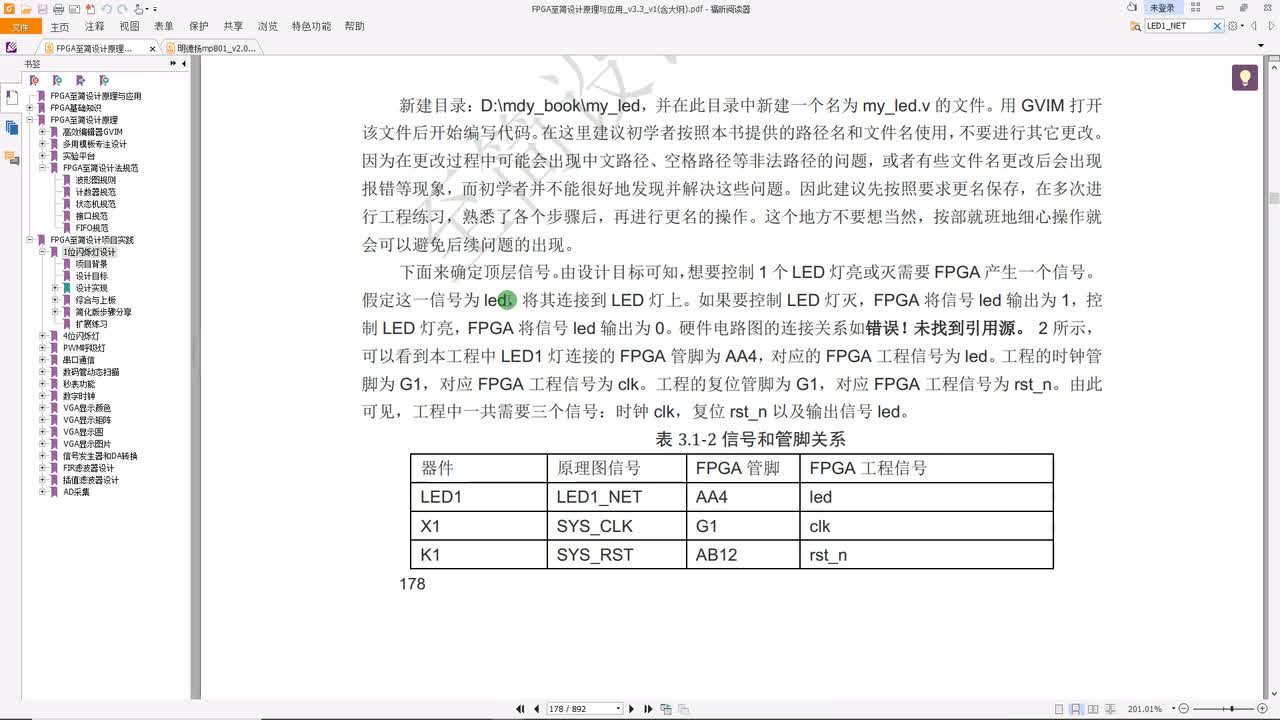

我們先分析一下板子上的LED燈。每個(gè)LED燈都有一個(gè)信號(hào)來(lái)控制,該信號(hào)為0,則燈亮,如果該信號(hào)為1,則燈來(lái)。現(xiàn)在我們要控制4個(gè)LED燈亮滅,那就需要4個(gè)信號(hào),假設(shè)分別為led0、led1、led2和led3。這4個(gè)信號(hào)分別連接到4個(gè)led燈上。如果要讓LED0燈0亮,LED1~3燈來(lái),那FPGA就讓led0信號(hào)為0,led1~3信號(hào)都為1。

綜上所述,我們這個(gè)工程需要6個(gè)信號(hào):時(shí)鐘clk,復(fù)位rst_n、led0、led1、led2和led3。

我們?cè)俜治鲆幌鹿δ苄枨螅?個(gè)燈隔1秒后,亮1秒;然后第2個(gè)燈隔1秒后,亮2秒;然后第3個(gè)燈隔1秒后,亮3秒,最后第4個(gè)燈隔1秒,亮4秒。如此循環(huán)往復(fù)。

上面的功能需求,也可以翻譯成:對(duì)于LED0,復(fù)位后,先滅1秒,亮1秒,然后再滅12秒,循環(huán)往復(fù);對(duì)于LED1,復(fù)位后,先滅3秒,亮2秒,然后再滅9秒,循環(huán)往復(fù);對(duì)于LED2,復(fù)位后,先滅6秒,亮3秒,然后再滅5秒,循環(huán)往復(fù);對(duì)于LED3,先滅10秒,亮4秒,循環(huán)往復(fù)。

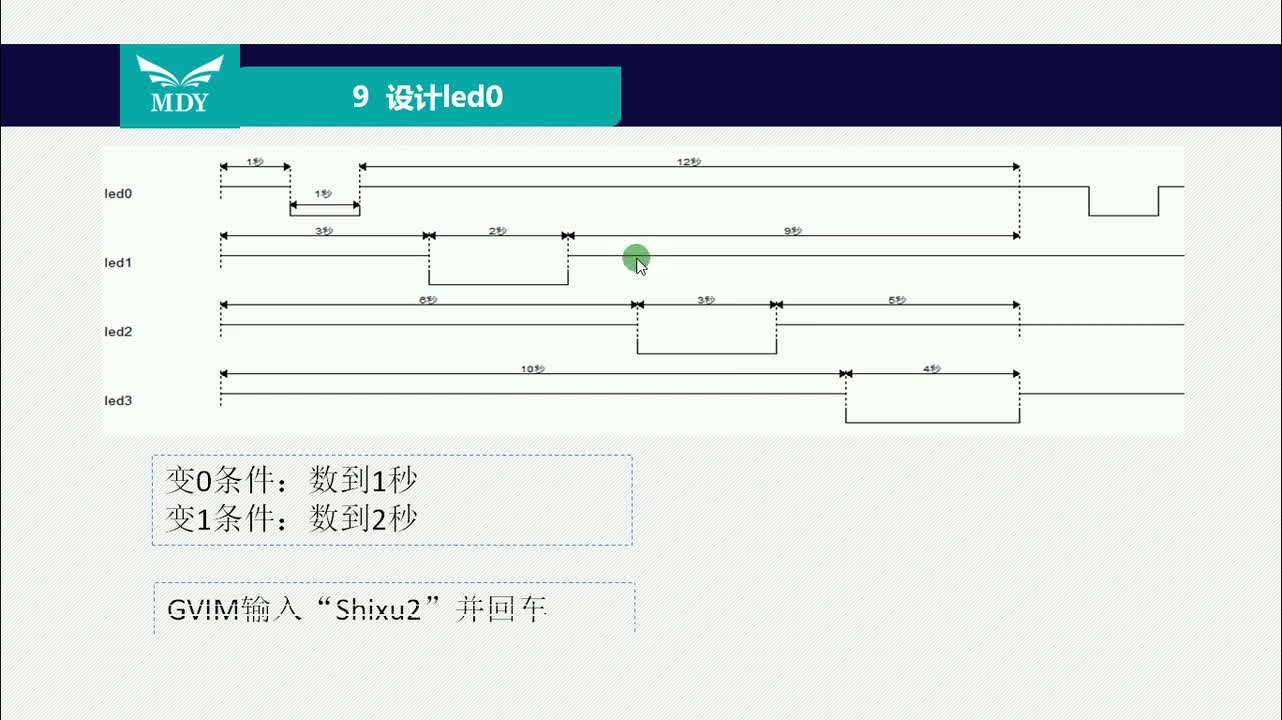

再將其翻譯成信號(hào)來(lái)理解:

復(fù)位后,讓信號(hào)led0=1并持續(xù)1秒,然后讓led0=0并持續(xù)1秒,然后讓led0=1持續(xù)12秒。循環(huán)往復(fù)。

復(fù)位后,讓信號(hào)led1=1并持續(xù)3秒,然后讓led1=0并持續(xù)2秒,然后讓led1=1持續(xù)9秒。循環(huán)往復(fù)。

復(fù)位后,讓信號(hào)led2=1并持續(xù)6秒,然后讓led2=0并持續(xù)3秒,然后讓led2=1持續(xù)5秒。循環(huán)往復(fù)。

復(fù)位后,讓信號(hào)led3=1并持續(xù)10秒,然后讓led3=0并持續(xù)4秒。循環(huán)往復(fù)。

再將其翻譯成波形如下圖所示。

由圖中可看到,信號(hào)led0~led3的變化單位最小是1秒,同時(shí)4個(gè)信號(hào)都是經(jīng)過(guò)14秒后就循環(huán)一次。由至簡(jiǎn)設(shè)計(jì)法的思想,很容易就得出我們需要2個(gè)計(jì)數(shù)器,1個(gè)計(jì)數(shù)器用來(lái)計(jì)算1秒時(shí)間,另1個(gè)計(jì)數(shù)器用來(lái)計(jì)算14秒。有了這兩個(gè)計(jì)數(shù)器,led0~led3的變化時(shí)間就有了標(biāo)準(zhǔn)。

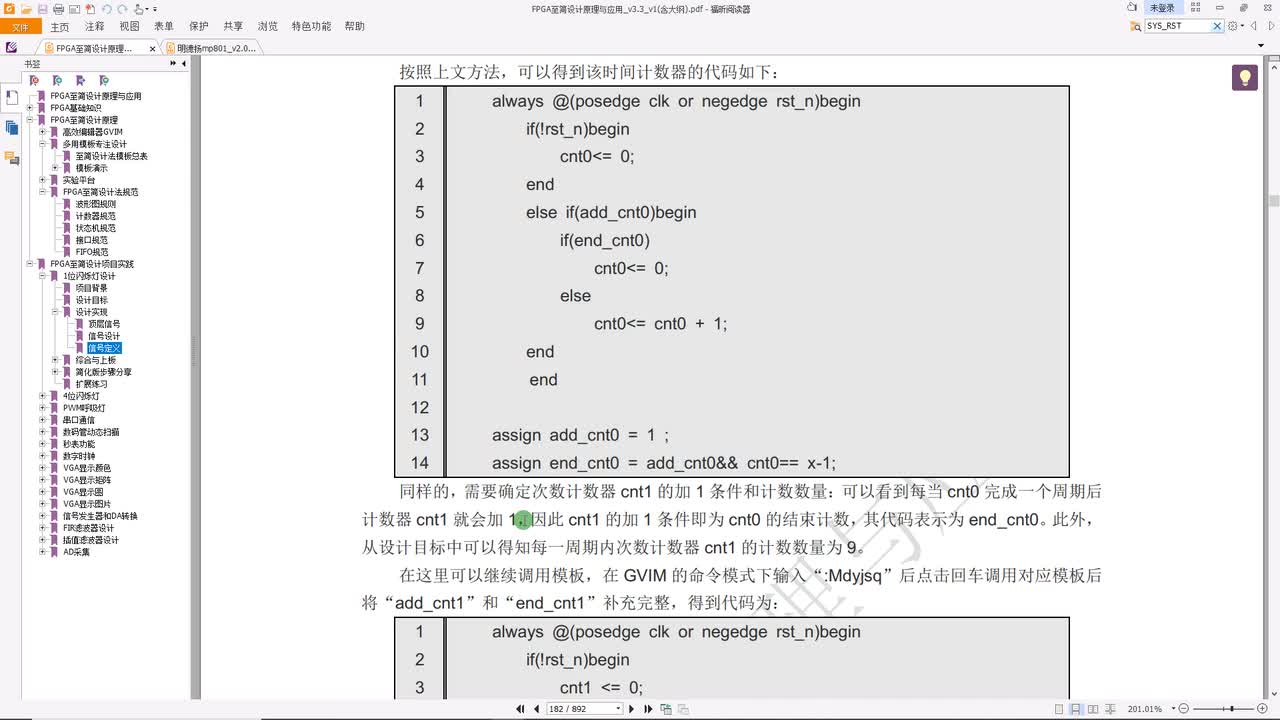

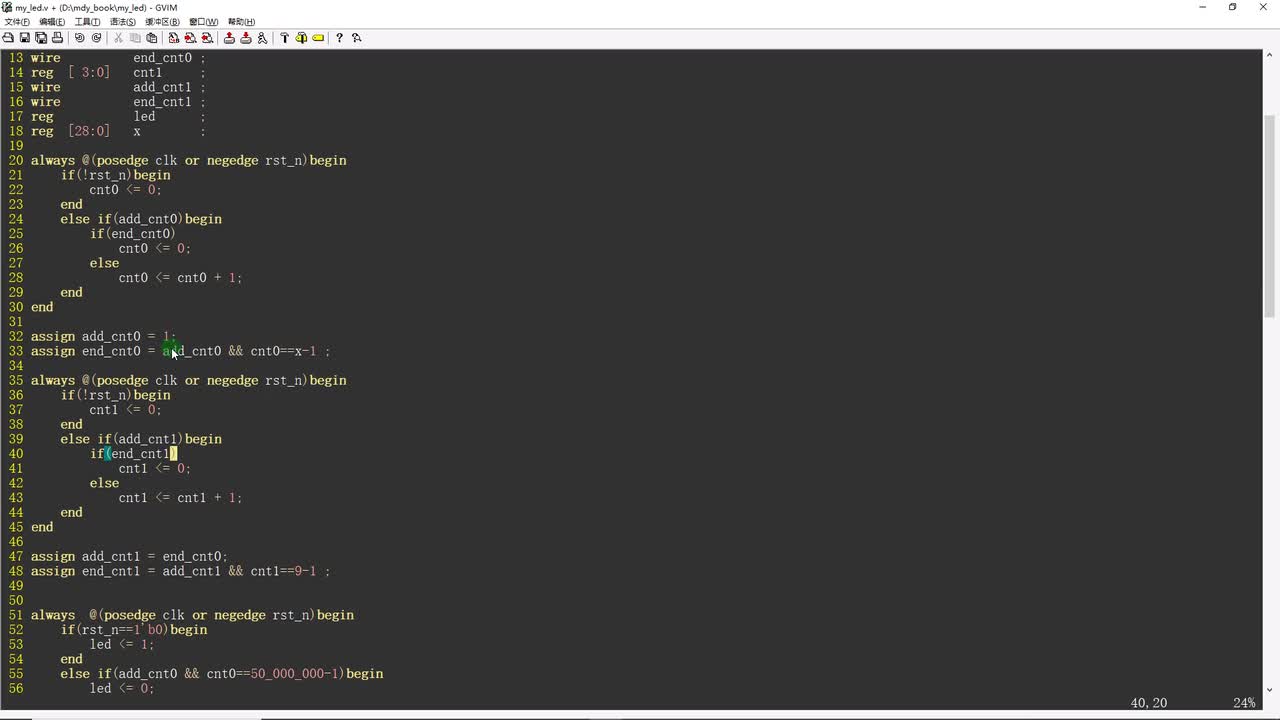

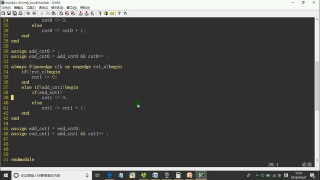

我們用1個(gè)計(jì)數(shù)器用來(lái)計(jì)算1秒時(shí)間,該計(jì)數(shù)器名稱為cnt0。本工程的工作時(shí)鐘是50MHz,即周期為20ns,計(jì)數(shù)器計(jì)數(shù)到1_000_000_000/20=50_000_000個(gè),我們就能知道1秒時(shí)間到了。該計(jì)數(shù)器是不停地計(jì)數(shù),永遠(yuǎn)不停止的,可以認(rèn)為加1條件一直有效,可寫(xiě)成:assign add_cnt==1。綜上所述,該計(jì)數(shù)器的代碼如下。

我們?cè)儆?個(gè)計(jì)數(shù)器用來(lái)表示14秒,名稱為cnt1。該計(jì)數(shù)器表示次數(shù),自然是每隔1秒就加1,那就是end_cnt0。該計(jì)數(shù)器一共要數(shù)14次。所以代碼為:

有了兩個(gè)計(jì)數(shù)器,我們來(lái)思考輸出信號(hào)led0的變化。概括起來(lái),led0有兩種變化點(diǎn):變0和變1。變0的原因都是計(jì)數(shù)到1秒時(shí)間,也就是add_cnt1 && cnt1==1-1時(shí),led0變0。變1的原因,則是數(shù)到2秒時(shí)間時(shí),即add_cnt1 && cnt1==2-1時(shí),led0變1。所以led0信號(hào)的代碼如下:

接下來(lái)我們思考輸出信號(hào)led1的變化。概括起來(lái),led1有兩種變化點(diǎn):變0和變1。變0的原因都是計(jì)數(shù)到3秒時(shí)間,也就是add_cnt1 && cnt1==3-1時(shí),led1變0。變1的原因,則是數(shù)到5秒時(shí)間時(shí),即add_cnt1 && cnt1==5-1時(shí),led1變1。所以led1信號(hào)的代碼如下:

接下來(lái)我們思考輸出信號(hào)led2的變化。概括起來(lái),led2有兩種變化點(diǎn):變0和變1。變0的原因都是計(jì)數(shù)到6秒時(shí)間,也就是add_cnt1 && cnt1==6-1時(shí),led2變0。變1的原因,則是數(shù)到9秒時(shí)間時(shí),即add_cnt1 && cnt1==9-1時(shí),led2變1。所以led2信號(hào)的代碼如下:

接下來(lái)我們思考輸出信號(hào)led3的變化。概括起來(lái),led3有兩種變化點(diǎn):變0和變1。變0的原因都是計(jì)數(shù)到10秒時(shí)間,也就是add_cnt1 && cnt1==10-1時(shí),led3變0。變1的原因,則是數(shù)到14秒時(shí)間時(shí),即add_cnt1 && cnt1==14-1,也就是end_cnt1時(shí),led3變1。所以led3信號(hào)的代碼如下:

此次,主體程序已經(jīng)完成。接下來(lái)是將module補(bǔ)充完整。

將module的名稱定義為huxiled。并且我們已經(jīng)知道該模塊有六個(gè)信號(hào):clk、rst_n、led0、led1、led2、led3。為此,代碼如下:

其中clk、rst_n是輸入信號(hào),led0、led1、led2、led3是輸出信號(hào),并且六個(gè)信號(hào)都是1比特的,根據(jù)這些信息,我們補(bǔ)充輸入輸出端口定義。代碼如下:

接下來(lái)定義信號(hào)類型。

cnt0是用always產(chǎn)生的信號(hào),因此類型為reg。cnt0計(jì)數(shù)的最大值為500_000_000,需要用29根線表示,即位寬是29位。因此代碼如下:

add_cnt0和end_cnt0都是用assign方式設(shè)計(jì)的,因此類型為wire。并且其值是0或者1,1個(gè)線表示即可。因此代碼如下:

cnt1是用always產(chǎn)生的信號(hào),因此類型為reg。cnt1計(jì)數(shù)的最大值為8,需要用4根線表示,即位寬是4位。因此代碼如下:

add_cnt1和end_cnt1都是用assign方式設(shè)計(jì)的,因此類型為wire。并且其值是0或者1,1根線表示即可。因此代碼如下:

led0、led1、led2、led3是用always方式設(shè)計(jì)的,因此類型為reg。并且其值是0或者1,1根線表示即可。因此代碼如下:

至此,整個(gè)代碼的設(shè)計(jì)工作已經(jīng)完成。下一步是新建工程和上板查看現(xiàn)象。

四、綜合工程和上板

新建工程

首先在d盤(pán)中創(chuàng)建名為“huxiled”的工程文件夾,將寫(xiě)的代碼命名為“huxiled.v”,頂層模塊名為“huxiled”。

然后打開(kāi)Quartus Ⅱ,點(diǎn)擊File下拉列表中的New Project Wzard.。.新建工程選項(xiàng)。

3.再出現(xiàn)的界面中直接點(diǎn)擊Next。

4.之后出現(xiàn)的是工程文件夾、工程名、頂層模塊名設(shè)置界面。按照之前的命名進(jìn)行填寫(xiě),然后點(diǎn)擊Next。

5.之后是文件添加界面。點(diǎn)擊紅色箭頭處,添加之前寫(xiě)的“huxiled.v”文件,點(diǎn)擊右側(cè)的“Add”按鈕,之后文件還會(huì)出現(xiàn)在黑色箭頭處,點(diǎn)擊,之后點(diǎn)擊“Next”。

器件型號(hào)選擇界面。在上方紅色箭頭處選擇Cyclone ⅣE,在中間紅色箭頭處選擇EP4CE6F17C8,然后點(diǎn)擊“Next”。

EDA工具界面。直接點(diǎn)擊“Next”。

8.之后出現(xiàn)的界面,點(diǎn)擊“Finish”。

綜合

1.新建工程步驟完成后,就會(huì)出現(xiàn)以下界面。選中要編譯的文件,點(diǎn)擊編譯按鈕。

2.編譯成功后會(huì)出現(xiàn)一下界面,點(diǎn)擊“OK”。

配置管腳

1.點(diǎn)擊箭頭所指的管腳配置按鈕。

2.下圖是我們要用的原理圖,其中箭頭所指就是我們要配置的六個(gè)管腳,分別是clk、rst、led0、led1、led2、led3。

3.在下圖箭頭處雙擊填上對(duì)應(yīng)的管腳號(hào),回車(chē)即可。

布局布線

管腳配置完成后,在進(jìn)行一次編譯。

連接開(kāi)發(fā)板

圖中,下載器接入電腦USB接口,電源接入電源,然后摁下下方藍(lán)色開(kāi)關(guān)。

上板

1.雙擊箭頭所指位置。

2.會(huì)出現(xiàn)如下界面,點(diǎn)擊“Start”,會(huì)在“Progress”出顯示進(jìn)度。

3.進(jìn)度條中提示成功后,即可在開(kāi)發(fā)板上觀察到相應(yīng)的現(xiàn)象。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論