濾波電容:用在電源整流電路中,用來(lái)濾除交流成分,使輸出的直流更平滑。去耦電容:用在放大電路中不需要交流的地方,用來(lái)消除自激,使放大器穩(wěn)定工作?旁路電容:用在有電阻連接時(shí),接在電阻兩端使交流信號(hào)順利

2019-08-26 09:41:50

PCB PDN design guidelines (PCB電源完整性設(shè)計(jì)指導(dǎo)) ------PCB平面圖指南一、 不帶電源平面1.為每個(gè)有源設(shè)備至少提供一個(gè)“本地”去耦電容器,并為板上分布的每個(gè)

2021-12-28 06:07:45

類(lèi)型的頻率響應(yīng)很重要。隨便選用電容,會(huì)讓設(shè)計(jì)低阻抗 PDS 系統(tǒng)的努力付之東流。如何設(shè)計(jì)出合格的 PDS要設(shè)計(jì)出合格的 PDS,需要使用各種電容(見(jiàn)圖 1)。PCB 上使用的典型電容值只能將直流或

2020-11-18 09:18:02

類(lèi)型的頻率響應(yīng)很重要。隨便選用電容,會(huì)讓設(shè)計(jì)低阻抗 PDS 系統(tǒng)的努力付之東流。如何設(shè)計(jì)出合格的 PDS要設(shè)計(jì)出合格的 PDS,需要使用各種電容(見(jiàn)圖 1)。PCB上使用的典型電容值只能將直流或接近

2022-05-07 11:30:38

是否通過(guò)走線或通過(guò)一對(duì)過(guò)孔將去耦電容連接到IC電源引腳的問(wèn)題。我們看到通孔技術(shù)是優(yōu)越的,因?yàn)樗档土穗姼校?dāng)我們?cè)噲D確保去耦電容在50-100] Vias和Planes在本文中,我們將探討與通孔

2018-07-27 11:59:50

對(duì)于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠(yuǎn),最外層放置容值最大的。但是,所有對(duì)該芯片去耦的電容都盡量

2018-09-18 15:56:26

個(gè)很全方面講解的。下面這些內(nèi)容是我轉(zhuǎn)載的一片關(guān)于電容去耦半徑的講解,相信你看了之后可以很牛x的回答和避免類(lèi)似問(wèn)題的發(fā)生。 老師 問(wèn):為什么去耦電容就近擺放呢?學(xué)生 答:因?yàn)樗杏行О霃脚叮诺倪h(yuǎn)了失效

2018-08-28 14:41:28

的相關(guān)文章。下面這篇文章是我轉(zhuǎn)載于博士的一片關(guān)于電容去耦半徑的講解,相信你看了之后可以很牛x的回答和避免類(lèi)似問(wèn)題的發(fā)生。 老師 問(wèn): 為什么去耦電容就近擺放呢?學(xué)生 答: 因?yàn)樗杏行О霃脚叮诺倪h(yuǎn)了

2018-09-12 10:46:08

個(gè)很全方面講解的。下面這些內(nèi)容是我轉(zhuǎn)載的一篇關(guān)于電容去耦半徑的講解,相信你看了之后可以很牛x的回答和避免類(lèi)似問(wèn)題的發(fā)生。 老師問(wèn): 為什么去耦電容就近擺放呢? 學(xué)生答: 因?yàn)樗杏行О霃脚叮诺倪h(yuǎn)了

2018-09-17 17:40:22

PCB抗干擾設(shè)計(jì),電源線、地線、去耦電容如何配置?

2021-03-17 07:04:11

什么是PCB中的板級(jí)去耦呢?如何設(shè)計(jì)板級(jí)去耦。

2021-01-22 06:28:39

個(gè)高頻去耦電容。每個(gè)電解電容邊上都要加一個(gè)小的高頻旁路電容。 (2) 用大容量的鉭電容或聚酯電容而不用電解電容作電路板上的充放電儲(chǔ)能電容。使用管狀電容時(shí),外殼要接地 (3) 對(duì)進(jìn)入印制板的信號(hào)要加濾波

2017-03-16 09:46:27

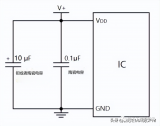

。二、降低沖擊電流影響的措施:(1)降低供電電源內(nèi)阻和供電線阻抗(2)匹配去耦電容三、何為去耦電容在 ic(或電路)電源線端和地線端加接的電容稱(chēng)為去耦電容。四、去耦電容如何取值去耦電容取值一般為

2011-02-24 14:30:32

?正題:在設(shè)計(jì)電子線路時(shí),比較多考慮的是產(chǎn)品的實(shí)際性能,而不會(huì)太多考慮產(chǎn)品的電磁兼容特性和電磁騷擾的抑制及電磁抗干擾特性,在實(shí)際PCB設(shè)計(jì)中可采用以下電路措施: (1)為每個(gè)集成電路設(shè)一個(gè)高頻去耦電容

2016-12-13 17:10:29

以下電路措施:(1)為每個(gè)集成電路設(shè)一個(gè)高頻去耦電容。每個(gè)電解電容邊上都要加一個(gè)小的高頻旁路電容。(2) 用大容量的鉭電容或聚酯電容而不用電解電容作電路板上的充放電儲(chǔ)能電容。使用管狀電容時(shí),外殼要接地

2016-12-07 17:04:14

。 (21) 弱信號(hào)電路,低頻電路周?chē)灰纬呻娏鳝h(huán)路。 (22) 信號(hào)都不要形成環(huán)路,如不可避免,讓環(huán)路區(qū)盡量小。 (23) 每個(gè)集成電路一個(gè)去耦電容。每個(gè)電解電容邊上都要加一個(gè)小的高頻旁路

2018-09-18 15:40:54

1.PCB設(shè)計(jì)之電容的結(jié)構(gòu)和特性給導(dǎo)體加電位,導(dǎo)體就帶上電荷。但對(duì)于相同的電位,導(dǎo)體容納電荷的數(shù)量卻因它本身結(jié)構(gòu)的不同而不同。導(dǎo)體能夠容納電荷的能力稱(chēng)為PCB設(shè)計(jì)之電容。 通常,某導(dǎo)體容納的電荷Q

2019-08-13 10:49:30

。對(duì)于小電容,因去耦半徑很小,應(yīng)盡可能的靠近需要去耦的芯片,這正是大多數(shù)資料上都會(huì)反復(fù)強(qiáng)調(diào)的,小電容要盡可能近的靠近芯片放置。 PCB布局時(shí)去耦電容擺放技巧與安裝 尖峰電流的抑制方法 1、在電路板

2023-04-11 16:26:00

振或鐘振)要盡量靠近用到該時(shí)鐘的器件;⑥. 在每個(gè)集成電路的電源輸入腳和地之間,需加一個(gè)去耦電容(一般采用高頻性能好的獨(dú)石電容);電路板空間較密時(shí),也可在幾個(gè)集成電路周?chē)?b class="flag-6" style="color: red">加一個(gè)鉭電容。⑦. 繼電器線圈

2014-09-23 09:32:40

盡量短,去耦電容引腳盡量短。 (18) 關(guān)鍵的線要盡量粗,并在兩邊加上保護(hù)地。高速線要短要直。 (19) 對(duì)噪聲敏感的線不要與大電流,高速開(kāi)關(guān)線平行。 (20) 石英晶體下面以及對(duì)噪聲敏感的器件

2018-11-28 17:05:55

,去耦電容引腳盡量短。 (18) 關(guān)鍵的線要盡量粗,并在兩邊加上保護(hù)地。高速線要短要直。 (19) 對(duì)噪聲敏感的線不要與大電流,高速開(kāi)關(guān)線平行。 (20) 石英晶體下面以及對(duì)噪聲敏感的器件下面不要

2018-12-21 09:29:36

經(jīng)常聽(tīng)說(shuō)pcb設(shè)計(jì)要加淚滴,至今任然不知道什么是淚滴,它長(zhǎng)啥樣啊,有沒(méi)有圖示?要怎樣加呢?

2015-07-22 19:36:35

` 本帖最后由 eehome 于 2013-1-5 10:08 編輯

去耦電容和旁路電容的區(qū)別`

2012-08-14 11:49:42

信號(hào)完整性之去耦電容與旁路電容

2019-11-19 14:52:05

去耦電容分為哪幾種?如何去放置去耦電容呢?在設(shè)計(jì)中如何防止上電及正常工作時(shí)出現(xiàn)總線沖突呢?

2021-11-03 07:17:04

一些。每10片左右集成電路要加一片充放電電容,或1個(gè)蓄能電容,可選10μF左右。最好不用電解電容,電解電容是兩層薄膜卷起來(lái)的,這種卷起來(lái)的結(jié)構(gòu)在高頻時(shí)表現(xiàn)為電感。要使用鉭電容或聚碳酸酯電容。去耦電容的選用

2012-03-08 23:42:09

去耦電容和旁路電容的區(qū)別詳解

2017-01-19 09:06:12

電子線路中的同一個(gè)電容,有時(shí)候會(huì)稱(chēng)它去耦電容,有時(shí)候又會(huì)稱(chēng)它為旁路電容。 電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,但是,當(dāng)我們從不同的角度去看時(shí),它所起的作用是不同的,所以才有

2021-05-25 06:14:19

去耦電容在PCB板設(shè)計(jì)中的應(yīng)用在板設(shè)計(jì)中應(yīng)充分考慮電磁兼容方面的問(wèn)題,合理地使用去耦電容在PCB板防止電磁干擾中具有重要作用, 本文就去耦電容的容量及其具體應(yīng)用作了較為全面、詳細(xì)的敘述,同時(shí)還介紹了增強(qiáng)去耦電容效果的一些實(shí)用方法。[hide][/hide]

2009-12-09 14:08:29

去耦電容的有效使用方法之一是用多個(gè)(而非1個(gè))電容進(jìn)行去耦。使用多個(gè)電容時(shí),使用相同容值的電容時(shí)和交織使用不同容值的電容時(shí),效果是不同的。

2019-08-02 06:56:29

去耦和旁路概述:旁路:空載時(shí)為了得到想要的輸出信號(hào)而加的電容。去耦:帶載時(shí)為了不讓負(fù)載對(duì)前級(jí)信號(hào)產(chǎn)生影響而加的電容。 耦合的產(chǎn)生:電路中總是存在驅(qū)動(dòng)的源和被驅(qū)動(dòng)的負(fù)載。如果負(fù)載電容比較大,驅(qū)動(dòng)電路

2015-08-26 21:56:00

何為去耦技術(shù)?正確去耦有何必要性?去耦電容有哪些類(lèi)型?不良去耦技術(shù)對(duì)性能的影響是什么

2021-03-11 08:14:14

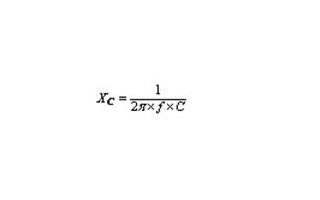

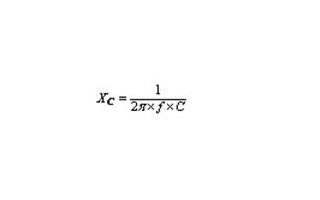

1.電源附近去耦電容的選擇很多IC管腳的VCC會(huì)增加一個(gè)0.1uf的去耦電容,因?yàn)?b class="flag-6" style="color: red">電容的濾波曲線在谷底最低的位置濾波效果最好。當(dāng)IC內(nèi)部的邏輯門(mén)頻率是是10MHz-50MHz的時(shí)候,0.1uf電容

2021-12-31 07:29:16

的分立電容去耦。在達(dá)到200~300 MHz以上頻率的電流工作狀態(tài)后,0.1μF與0.01μF并聯(lián)的去耦電容由于感性太強(qiáng),轉(zhuǎn)換速度緩慢,不能提供滿(mǎn)足需要的充電電流。 在PCB上放置元件時(shí),必須提供

2018-11-27 15:19:23

請(qǐng)問(wèn)去耦電容的選擇按照這個(gè)圖上的規(guī)則來(lái)選對(duì)嗎

2018-11-19 11:21:51

一個(gè)原型設(shè)計(jì)電路板省去了比較麻煩的去耦電容器;但獲得的任何結(jié)果都無(wú)法與預(yù)期結(jié)果相匹配。最后,添加一個(gè)去耦電容器,問(wèn)題解決了。什么我們需要使用去耦電容器?它的作用到底是什么?

2021-04-02 07:46:38

解釋對(duì)應(yīng)的分別是低頻和高頻兩種情況,但本質(zhì)上都是希望減小PDN上的電壓突變,這就是去耦。2.為什么要有那么多的去耦電容而不是選擇一個(gè)等效的大電容?這個(gè)問(wèn)題也是要分情況,對(duì)于低頻來(lái)說(shuō),很多個(gè)小的去耦電容

2019-05-07 06:22:23

去耦旁路電路,不同規(guī)格的電容在PCB布局時(shí)該怎么擺

2021-03-17 07:33:04

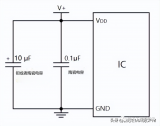

我們都知道小電容濾高頻,大電容濾低頻,為了更好的濾波效果,一般輸入電源或者輸出電源都是采用一個(gè)大容值電容加一個(gè)小容值電容進(jìn)行濾波,比如1uF+0.1uF; 我們先來(lái)了解一下去耦和旁路的區(qū)別

2021-01-11 16:31:51

電容在高速 PCB 設(shè)計(jì)中起著重要的作用,通常也是 PCB 上用得最多的器件。在 PCB 中,電容通 常分為濾波電容、去耦電容、儲(chǔ)能電容等。 1 電源輸出電容,濾波電容 我們通常把電源模塊

2023-04-20 10:32:14

對(duì)于已經(jīng)知道了電容的具體特性和適用范圍,以及去耦原理,那么就知道了去耦的具體方法了嗎?不是的,下面我們將講解一下,具體安裝到電路板上之后的去耦原理以及具體如何防止電容的準(zhǔn)則!

2021-03-04 08:11:41

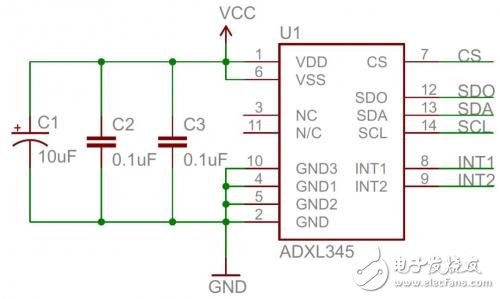

4片,每一片各10個(gè)管腳,四片共40個(gè)電源管腳,單片如圖 Demo給出的去耦電容一共十幾個(gè),貌似容值還有規(guī)律0.1u 0.1p 1p的各四組等 去耦電容如圖 我的第一個(gè)問(wèn)題是去耦電容 為什么要這么選擇

2016-12-13 09:34:14

擾的影響可降至最低。例如,如果走線寬度為5密耳,則兩條并行走線之間的最小距離應(yīng)為10密耳或更大。隨著新材料和新的元器件不斷出現(xiàn),PCB設(shè)計(jì)人員還必須繼續(xù)應(yīng)對(duì)電磁兼容性和干擾問(wèn)題。

技巧4:去耦電容

去

2023-12-19 09:53:34

`各位大神,請(qǐng)問(wèn)FPGA去耦電容如何布局、布線?1.根據(jù)文檔,一般去耦電容的數(shù)量都少于電源引腳,那么去耦電容要放到哪些管腳旁邊呢?2.以下三種方案哪種好?2.1電容放在PCB top層FPGA外圍

2017-08-22 14:57:10

想為cyclone V 系列的5CEFA7F27這款FPGA設(shè)計(jì)去耦電容電路,但是不知道該如何下手。參考了altera公司的一塊開(kāi)發(fā)板,給出的FPGA的去耦電容電路如下所示,但是感覺(jué)這個(gè)去耦電容電路

2016-07-09 10:11:21

親愛(ài)的先生/女士,我們?cè)谖覀兊恼{(diào)制解調(diào)器板上使用兩個(gè)xc7k160t-1ffgi,基于我們使用xpe進(jìn)行功率估算的邏輯利用率。根據(jù)UG483(PCB設(shè)計(jì)指南)遵循每個(gè)組的去耦電容器數(shù)量)。第17頁(yè)表

2020-08-17 10:48:12

一、名詞定義:旁路(bypass)電容: pass是通過(guò)的意思,bypass指從靠近的地方,從旁邊通過(guò)。大路不走走小路,主路不走走輔路。所以, 旁路電容可以理解成把信號(hào)高頻成分旁路掉的電容。去耦

2022-11-04 22:29:20

專(zhuān)業(yè)allegro pcb設(shè)計(jì),10 看工作經(jīng)驗(yàn),要的加Q279312621

2017-09-19 17:05:43

系統(tǒng)需要用到大量的理論知識(shí)以及與之相對(duì)應(yīng)的實(shí)際應(yīng)用,這篇文檔將會(huì)用到許多重要的概念。感謝原作者和中文對(duì)照作者們。目錄:?PCBS 101?優(yōu)秀的高速PCB設(shè)計(jì)練習(xí)–電源/地系統(tǒng)的效率–正確使用去耦電容

2017-07-26 17:37:44

PCB設(shè)計(jì)

VDD_CPU_BIG0/1

01

如下圖(上)所示的濾波電容,原理圖上靠近RK3588的VDD_CPU_BIG電源管腳綠線以?xún)?nèi)的去耦電容,務(wù)必放在對(duì)應(yīng)的電源管腳背面,電容GND PAD盡量

2023-08-10 16:37:25

,如不可避免,讓環(huán)路區(qū)盡量小。(23) 每個(gè)集成電路一個(gè)去耦電容。每個(gè)電解電容邊上都要加一個(gè)小的高頻旁路電容。(24) 用大容量的鉭電容或聚酷電容而不用電解電容作電路充放電儲(chǔ)能電容。使用管狀電容時(shí),外殼要接地。

2018-03-10 21:32:11

。 (21) 弱信號(hào)電路,低頻電路周?chē)灰纬呻娏鳝h(huán)路。 (22) 信號(hào)都不要形成環(huán)路,如不可避免,讓環(huán)路區(qū)盡量小。 (23) 每個(gè)集成電路一個(gè)去耦電容。每個(gè)電解電容邊上都要加一個(gè)小的高頻旁路電容

2019-02-01 22:35:31

除了電阻之外,在我們的設(shè)計(jì)中,用的最多的器件便是電容。不要輕視這些小小的電容,他們的作用非常大,如果在電路中用的地方不好,會(huì)非常影響電路的功能。 在PCB設(shè)計(jì)過(guò)程中電源的管腳為什么要加許多電容?

2019-08-26 11:28:36

什么是PCB中的板級(jí)去耦呢?如何設(shè)計(jì)板級(jí)去耦?

2021-01-25 06:33:18

SOIC 的去耦局部的高頻濾波器可以?xún)?yōu)化小小效果,去耦電容 可以減小回路電感經(jīng)驗(yàn)法則–Via resistance ≈ 1mΩ, Via inductance ≈ 1nHLQFP/LFCSP 去耦

2020-10-13 09:04:13

我在百度百科看到這樣一句話(huà):為了防止多級(jí)子系統(tǒng)間電源的相互串?dāng)_,一般在每級(jí)子系統(tǒng)的電源輸入端加0.1u的電容來(lái)去耦;我就想起我的一個(gè)問(wèn)題,我這幾天做了一個(gè)功放,前級(jí)用LM324放大,后級(jí)用

2013-05-09 19:41:13

`關(guān)于去耦電容旁路電容的總結(jié)`

2012-08-20 14:01:15

一般去耦電容的容量選取原則是什么?

2021-06-08 06:38:27

怎么分清濾波電容、去耦電容、旁路電容?其實(shí)并不難~

2021-01-22 07:53:58

用于電容傳感器接口的模擬前端元件有哪些?基于PCB設(shè)計(jì)的電容傳感器

2021-04-22 06:48:21

通用電容傳感器模擬前端測(cè)量方法用于電容傳感器接口的模擬前端元件基于PCB設(shè)計(jì)的電容傳感器

2021-04-09 06:17:02

Walt Kester在上篇文章中,我們介紹了去耦的基礎(chǔ)知識(shí)及其在實(shí)現(xiàn)集成電路(IC)期望性能方面的重要性。在本篇文章中,我們將詳細(xì)探討用于去耦的基本電路元件——電容。實(shí)際電容及其寄生效應(yīng)圖1所示為

2018-10-19 10:58:00

,也就是說(shuō),對(duì)于10MHz以下的噪聲有較好的去耦效果,對(duì)40MHz以上的噪聲幾乎不起作用。1μF、10μF的電容,并行共振頻率在2MHz以上,去除高頻噪聲的效果要好一些。每10片左右集成電路要加一片充放電電容

2018-12-07 09:39:59

集成電路的電源,地之間都要加一個(gè)去耦電容。去耦電容有兩個(gè)作用:一方面是本集成電路的蓄能電容,提供和吸收該集成電路開(kāi)門(mén)關(guān)門(mén)瞬間的充放電能;另一方面旁路掉該器件的高頻噪聲。數(shù)字電路中典型的去耦電容為0.1uf

2013-03-08 16:33:18

一、電源濾波技術(shù):常用的濾波措施有:去耦電容、電感、磁珠等。常用的濾波場(chǎng)景有:電源濾波、接口濾波等。在進(jìn)行PCB設(shè)計(jì)時(shí),濾波器件的擺放位置相當(dāng)關(guān)鍵,對(duì)于電容類(lèi)去耦的濾波原則是靠近濾波區(qū)域位置放置最佳

2021-11-11 08:03:08

在ug373“Virtex-6 FPGA PCB設(shè)計(jì)指南”v1.3中,不需要用于Vccaux和Vcco的去耦電容(表2-1至2-2),而在我讀過(guò)的早期版本中,數(shù)字并非都是零(我不記得確切的數(shù)字)。這些0與ug373以及ML605原理圖中的以下描述相矛盾。對(duì)此有什么正確的答案?

2020-06-08 11:03:50

電源去耦電容為何要接近IC電源引腳?是什么原因呢?

2023-04-21 17:36:30

電源端為什么要加那么多去耦電容,而不是用一個(gè)等效的大電容代替!如輸入為5V的電源,并聯(lián)10個(gè)0.1u的電容后接地。為什么不是直接接一個(gè)1u的電容而是接10個(gè)0.1u電容。論容值 1u=0.1u*10 。求解!!

2023-03-28 16:12:56

找到一個(gè)很全方面講解的。下面這些內(nèi)容是我轉(zhuǎn)載的一篇關(guān)于

電容去耦半徑的講解,相信你看了之后可以很牛x的回答和避免類(lèi)似問(wèn)題的發(fā)生。 老師問(wèn): 為什么

去耦電容就近擺放呢? 學(xué)生答: 因?yàn)樗杏行О霃脚叮?/div>

2019-09-06 18:13:24

和供電線阻抗 (2)匹配去耦電容 三、何為去耦電容 在IC(或電路)電源線端和地線端加接的電容稱(chēng)為去耦電容。 四、去耦電容如何取值 去耦電容取值一般為0.01~0.1uf,頻率越高,去耦電容值越小

2017-05-04 10:48:07

在設(shè)計(jì)的時(shí)候 是不是板子上加的去耦電容越多越好?我看原理圖工程師有的地方加很多

2019-05-08 04:15:39

本資料包括在高速PCB設(shè)計(jì)中電源/地的設(shè)置要求,正確使用去耦電容的方法,分析了電阻,電容在高速設(shè)計(jì)中的特性;混合信號(hào)布線中的接地方式,電源的濾波及去耦方式;小信號(hào)布線走線損耗和預(yù)防PCB溫度問(wèn)題。

2019-03-25 15:51:27

電容在高速PCB設(shè)計(jì)中的應(yīng)用:探討高速PCB設(shè)計(jì)電容的應(yīng)用。電容是電路板上不可缺少的一個(gè)部分,并且起到了至關(guān)重要的作用,探討他具備至關(guān)重要的價(jià)值。您在設(shè)計(jì)中是否有這樣

2009-08-16 13:11:56 0

0 高速PCB設(shè)計(jì)電容的應(yīng)用,很有參考意義

2016-12-16 22:07:10 0

0 高速PCB設(shè)計(jì)電容的應(yīng)用

2017-01-28 21:32:49 0

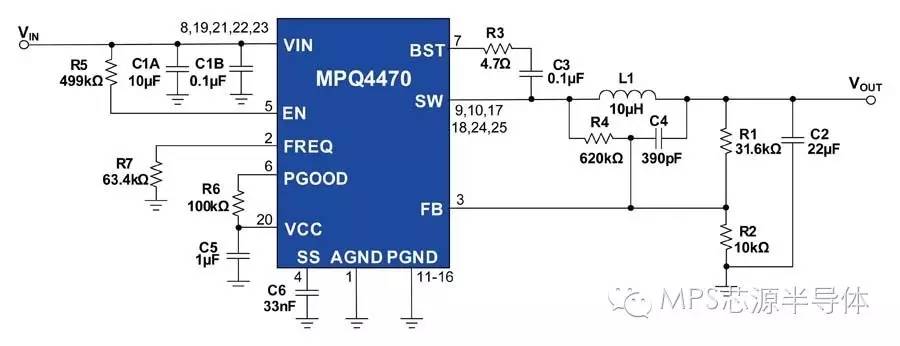

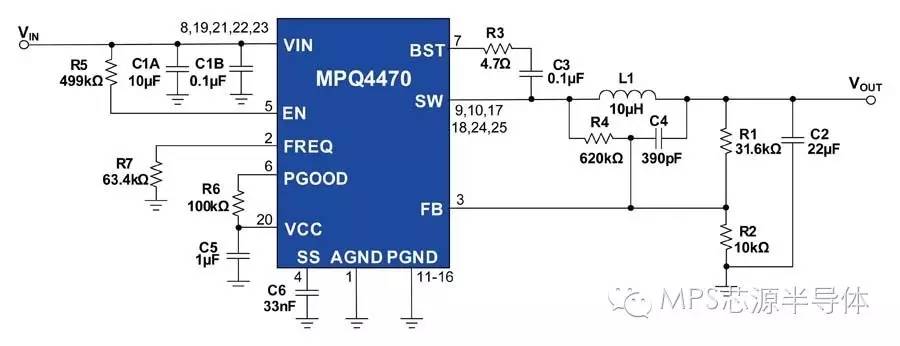

0 MPQ4470采用對(duì)稱(chēng)的輸入引腳配置,使其在PCB設(shè)計(jì)時(shí)可以放置對(duì)稱(chēng)電容,不僅減小了高頻環(huán)路的面積,而且對(duì)稱(chēng)的環(huán)路也抵消了大部分的電磁輻射,EMI性能因此得到了很大的提升。配以適當(dāng)?shù)妮斎隕MI濾波器

2019-10-11 17:05:08 3465

3465

小編給大家分享一下PCB設(shè)計(jì)電容中必須要知道的知識(shí)點(diǎn),期待對(duì)大家的PCB設(shè)計(jì)有作用。 去耦電容:電源附近的 旁路電容:芯片的電源管腳根部,10-0.1-0.01uF電容組,用于濾除高頻噪聲,防止自己

2020-08-12 10:38:44 6857

6857

今天給大家分享的是:去耦電容,去耦電容PCB設(shè)計(jì)和布局。

2023-07-05 09:37:14 888

888

其中一個(gè)附屬文件就可能包含PCB設(shè)計(jì)用到全部去耦電容。如果電容數(shù)低于或高于期望值,就將在可能出現(xiàn)電源線dv/dt問(wèn)題地方標(biāo)注紅色記號(hào)。

2023-10-31 15:06:37 159

159 高速PCB設(shè)計(jì)電容的應(yīng)用

2022-12-30 09:22:16 29

29 高速PCB設(shè)計(jì)電容的應(yīng)用

2023-03-01 15:37:57 2

2 本篇介紹PCB設(shè)計(jì)時(shí)處理去耦電容和旁路電容的注意事項(xiàng)。

去耦電容(另見(jiàn)退耦電容、緩沖電容、儲(chǔ)能電容等),可以放置在電源電路公共出口處,或者外部電源輸入PCB的連接器旁。較大的電路板可以放置多個(gè),但通常2、3個(gè)就夠了。

2023-11-21 15:33:26 392

392 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論