1. 一般規(guī)則

1.1 PCB板上預(yù)劃分數(shù)字、模擬、DAA信號布線區(qū)域。

1.2 數(shù)字、模擬元器件及相應(yīng)走線盡量分開并放置於各自的布線區(qū)域內(nèi)。

1.3 高速數(shù)字信號走線盡量短。

1.4 敏感模擬信號走線盡量短。

1.5 合理分配電源和地。

1.6 DGND、AGND、實地分開。

1.7 電源及臨界信號走線使用寬線。

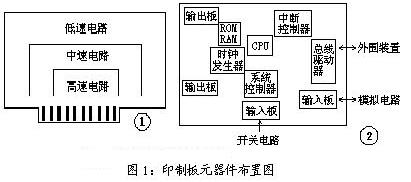

1.8 數(shù)字電路放置於并行總線/串行DTE接口附近,DAA電路放置於電話線接口附近。

2. 元器件放置

2.1 在系統(tǒng)電路原理圖中:

a) 劃分數(shù)字、模擬、DAA電路及其相關(guān)電路;

b) 在各個電路中劃分數(shù)字、模擬、混合數(shù)字/模擬元器件;

2.2 初步劃分數(shù)字、模擬、DAA電路在PCB板上的布線區(qū)域(一般比例2/1/1),數(shù)字、模擬元器件及其相應(yīng)走線盡量遠離并限定在各自的布線區(qū)域內(nèi)。

Note:當(dāng)DAA電路占較大比重時,會有較多控制/狀態(tài)信號走線穿越其布線區(qū)域,可根據(jù)當(dāng)?shù)匾?guī)則限定做調(diào)整,如元器件間距、高壓抑制、電流限制等。

2.3 初步劃分完畢後,從Connector和Jack開始放置元器件:

a) Connector和Jack周圍留出插件的位置;

b) 元器件周圍留出電源和地走線的空間;

c) Socket周圍留出相應(yīng)插件的位置。

2.4 首先放置混合型元器件(如Modem器件、A/D、D/A轉(zhuǎn)換芯片等):

a) 確定元器件放置方向,盡量使數(shù)字信號及模擬信號引腳朝向各自布線區(qū)域;

b) 將元器件放置在數(shù)字和模擬信號布線區(qū)域的交界處。

2.5 放置所有的模擬器件:

a) 放置模擬電路元器件,包括DAA電路;

b) 模擬器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信號走線的一面;

c) TXA1、TXA2、RIN、VC、VREF信號走線周圍避免放置高噪聲元器件;

d) 對於串行DTE模塊,DTE EIA/TIA-232-E

系列接口信號的接收/驅(qū)動器盡量靠近Connector并遠離高頻時鐘信號走線,以減少/避免每條線上增加的噪聲抑制器件,如阻流圈和電容等。

2.6 放置數(shù)字元器件及去耦電容:

a) 數(shù)字元器件集中放置以減少走線長度;

b) 在IC的電源/地間放置0.1uF的去耦電容,連接走線盡量短以減小EMI;

c) 對并行總線模塊,元器件緊靠

Connector邊緣放置,以符合應(yīng)用總線接口標準,如ISA總線走線長度限定在2.5in;

d) 對串行DTE模塊,接口電路靠近Connector;

e) 晶振電路盡量靠近其驅(qū)動器件。

2.7 各區(qū)域的地線,通常用0 Ohm電阻或bead在一點或多點相連。

3. 信號走線

3.1 Modem信號走線中,易產(chǎn)生噪聲的信號線和易受干擾的信號線盡量遠離,如無法避免時要用中性信號線隔離。

Modem易產(chǎn)生噪聲的信號引腳、中性信號引腳、易受干擾的信號引腳如下表所示:

MODEM信號線

RS-232C串行口信號分為三類:傳送信號、聯(lián)絡(luò)信號和地線

(1)傳送信號:指TXD(發(fā)送數(shù)據(jù)信號線)和RXD(接收數(shù)據(jù)信號線)。經(jīng)由TXD傳送和RXD接收的信息格式為:一個傳送單位(字節(jié))由起始位、數(shù)據(jù)位、奇偶校驗位和停止位組成。

(2)聯(lián)絡(luò)信號:指RTS、CTS、DTR、DSR、DCD和RI六個信號,各自功能為:

RTS(請求傳送),是PC向MODEM發(fā)出的聯(lián)絡(luò)信號。高電平表示PC機請求向MODEM傳送數(shù)據(jù)

CTS(清除發(fā)送),是MODEM向PC機發(fā)出的聯(lián)絡(luò)信號。高電平表示MODEM響應(yīng)PC發(fā)出的RTS信號,且準備向遠程MODEM發(fā)送數(shù)據(jù)。

DTR(數(shù)據(jù)終端就緒),是PC向MODEM發(fā)出的聯(lián)絡(luò)信號。高電屏表示PC機處于就緒狀態(tài),本地MODEM 和遠程MODEM之間可以建立通信信道。若為低電屏,則強迫MODEM終止通信。

DSR(數(shù)據(jù)裝置就緒),是MODEM向PC機發(fā)出的聯(lián)絡(luò)信號。它指出本地MODEM的工作狀態(tài),高電平表示 MODEM沒有處于測試通話狀態(tài),可以和遠程MODEM建立通道。

DCD(傳送檢測),是MODEM向PC發(fā)出的狀態(tài)信號。高電平表示本地DCE接收到遠程MODEM發(fā)來的載波信號。

RI(振鈴指示),是MODEM向PC發(fā)出的狀態(tài)信號。高電平表示本地MODEM收到遠程MODEM發(fā)來的振鈴信號。

(3)地線信號(GND),為相連的PC和MODEM提供同一電勢參考點。

56K高速Modem是1997年才開始上市的撥號高速調(diào)制解調(diào)器,它的傳輸速率之所以能有高于傳統(tǒng)電話線路上33.6Kbps的極限速率,是因為它采用了完全不同于33.6K的調(diào)制解調(diào)技術(shù),其工件原理和使用要求與33.6 K高速Modem相比也有一定的區(qū)別。

DTE與DCE之間的連接標準有CCITTV.10/X.26;

3.2 數(shù)字信號走線盡量放置在數(shù)字信號布線區(qū)域內(nèi);

模擬信號走線盡量放置在模擬信號布線區(qū)域內(nèi);

(可預(yù)先放置隔離走線加以限定,以防走線布出布線區(qū)域)

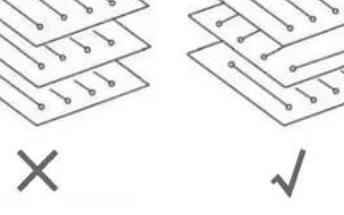

數(shù)字信號走線和模擬信號走線垂直以減小交叉耦合。

3.3 使用隔離走線(通常為地)將模擬信號走線限定在模擬信號布線區(qū)域。

a) 模擬區(qū)隔離地走線環(huán)繞模擬信號布線區(qū)域布在PCB板兩面,線寬50-100mil;

b) 數(shù)字區(qū)隔離地走線環(huán)繞數(shù)字信號布線區(qū)域布在PCB板兩面,線寬50-100mil,其中一面PCB板邊應(yīng)布200mil寬度。

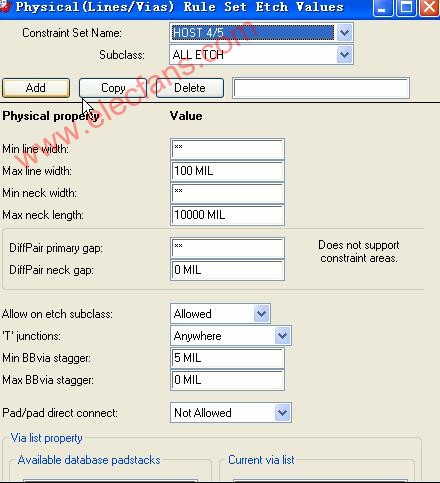

3.4 并行總線接口信號走線線寬》10mil(一般為12-15mil),如/HCS、/HRD、/HWT、/RESET。

3.5 模擬信號走線線寬》10mil(一般為12-15mil),如MICM、MICV、SPKV、VC、VREF、TXA1、TXA2、RXA、TELIN、TELOUT。

3.6 所有其它信號走線盡量寬,線寬》5mil(一般為 10mil),元器件間走線盡量短(放置器件時應(yīng)預(yù)先考慮)。

3.7 旁路電容到相應(yīng)IC的走線線寬》25mil,并盡量避免使用過孔。

3.8 通過不同區(qū)域的信號線(如典型的低速控制/狀態(tài)信號)應(yīng)在一點(首選)或兩點通過隔離地線。如果走線只位於一面,隔離地線可走到PCB的另一面以跳過信號走線而保持連續(xù)。

3.9 高頻信號走線避免使用90度角彎轉(zhuǎn),應(yīng)使用平滑圓弧或45度角。

3.10 高頻信號走線應(yīng)減少使用過孔連接。

3.11 所有信號走線遠離晶振電路。

3.12 對高頻信號走線應(yīng)采用單一連續(xù)走線,避免出現(xiàn)從一點延伸出幾段走線的情況。

3.13 DAA電路中,穿孔周圍(所有層面)留出至少60mil的空間。

3.14 清除地線環(huán)路,以防意外電流回饋影響電源。

4. 電源

4.1 確定電源連接關(guān)系。

4.2 數(shù)字信號布線區(qū)域中,用10uF電解電容或鉭電容與0.1uF瓷片電容并聯(lián)後接在電源/地之間。在PCB板電源入口端和最遠端各放置一處,以防電源尖峰脈沖引發(fā)的噪聲干擾。

4.3 對雙面板,在用電電路相同層面中,用兩邊線寬為 200mil的電源走線環(huán)繞該電路。(另一面須用數(shù)字地做相同處理)

4.4 一般地,先布電源走線,再布信號走線。

5. 地

5.1雙面板中,數(shù)字和模擬元器件(除DAA)周圍及下方未使用之區(qū)域用數(shù)字地或模擬地區(qū)域填充,各層面同類地區(qū)域連接在一起,不同層面同類地區(qū)域通過多個過孔相連:Modem DGND引腳接至數(shù)字地區(qū)域,AGND引腳接至模擬地區(qū)域;數(shù)字地區(qū)域和模擬地區(qū)域用一條直的空隙隔開。

5.2 四層板中,使用數(shù)字和模擬地區(qū)域覆蓋數(shù)字和模擬元器件(除DAA);Modem DGND引腳接至數(shù)字地區(qū)域,AGND引腳接至模擬地區(qū)域;數(shù)字地區(qū)域和模擬地區(qū)域用一條直的空隙隔開。

5.3 如設(shè)計中須EMI過濾器,應(yīng)在接口插座端預(yù)留一定空間,絕大多數(shù)EMI器件(Bead/電容)均可放置在該區(qū)域;未使用之區(qū)域用地區(qū)域填充,如有屏蔽外殼也須與之相連。

5.4 每個功能模塊電源應(yīng)分開。功能模塊可分為:并行總線接口、顯示、數(shù)字電路(SRAM、EPROM、Modem)和DAA等,每個功能模塊的電源/地只能在電源/地的源點相連。

5.5 對串行DTE模塊,使用去耦電容減少電源耦合,對電話線也可做相同處理。

5.6 地線通過一點相連,如可能,使用Bead;如抑制EMI需要,允許地線在其它地方相連。

5.7 所有地線走線盡量寬,25-50mil。 。

5.8 所有IC電源/地間的電容走線盡量短,并不要使用過孔。

6. 晶振電路

6.1 所有連到晶振輸入/輸出端(如XTLI、XTLO)的走線盡量短,以減少噪聲干擾及分布電容對Crystal的影響。XTLO走線盡量短,且彎轉(zhuǎn)角度不小於45度。(因XTLO連接至上升時間快,大電流之驅(qū)動器)

6.2 雙面板中沒有地線層,晶振電容地線應(yīng)使用盡量寬的短線連接至器件上離晶振最近的DGND引腳,且盡量減少過孔。

6.3 如可能,晶振外殼接地。

6.4 在XTLO引腳與晶振/電容節(jié)點處接一個100 Ohm電阻。

6.5 晶振電容的地直接連接至 Modem的GND引腳,不要使用地線區(qū)域或地線走線來連接電容和Modem的GND引腳。

7. 使用EIA/TIA-232接口的獨立Modem設(shè)計

7.1 使用金屬外殼。 如果須用塑料外殼,應(yīng)在內(nèi)部貼金屬箔片或噴導(dǎo)電物質(zhì)以減小EMI。

7.2 各電源線上放置相同模式的Choke。

7.3 元器件放置在一起并緊靠EIA/TIA-232接口的Connector。

7.4 所有EIA/TIA-232器件從電源源點單獨連接電源/地。電源/地的源點應(yīng)為板上電源輸入端或調(diào)壓芯片的輸出端。

7.5 EIA/TIA-232電纜信號地接至數(shù)字地。

針對模擬信號,再作一些詳細說明:

模擬電路的設(shè)計是工程師們最頭疼、但也是最致命的設(shè)計部分,盡管目前數(shù)字電路、大規(guī)模集成電路的發(fā)展非常迅猛,但是模擬電路的設(shè)計仍是不可避免的,有時也是數(shù)字電路無法取代的,例如 RF 射頻電路的設(shè)計!這里將模擬電路設(shè)計中應(yīng)該注意的問題總結(jié)如下,有些純屬經(jīng)驗之談,還望大家多多補充、多多批評指正!

(1)為了獲得具有良好穩(wěn)定性的反饋電路,通常要求在反饋環(huán)外面使用一個小電阻或扼流圈給容性負載提供一個緩沖。

(2)積分反饋電路通常需要一個小電阻(約 560 歐)與每個大于 10pF 的積分電容串聯(lián)。

(3)在反饋環(huán)外不要使用主動電路進行濾波或控制 EMC 的 RF 帶寬,而只能使用被動元件(最好為 RC 電路)。僅僅在運放的開環(huán)增益比閉環(huán)增益大的頻率下,積分反饋方法才有效。在更高的頻率下,積分電路不能控制頻率響應(yīng)。

(4)為了獲得一個穩(wěn)定的線性電路,所有連接必須使用被動濾波器或其他抑制方法(如光電隔離)進行保護。

(5)使用 EMC 濾波器,并且與 IC 相關(guān)的濾波器都應(yīng)該和本地的 0V 參考平面連接。

(6)在外部電纜的連接處應(yīng)該放置輸入輸出濾波器,任何在沒有屏蔽系統(tǒng)內(nèi)部的導(dǎo)線連接處都需要濾波,因為存在天線效應(yīng)。另外,在具有數(shù)字信號處理或開關(guān)模式的變換器的屏蔽系統(tǒng)內(nèi)部的導(dǎo)線連接處也需要濾波。

(7)在模擬 IC 的電源和地參考引腳需要高質(zhì)量的 RF 去耦,這一點與數(shù)字 IC 一樣。但是模擬 IC 通常需要低頻的電源去耦,因為模擬元件的電源噪聲抑制比(PSRR)在高于 1KHz 后增加很少。在每個運放、比較器和數(shù)據(jù)轉(zhuǎn)換器的模擬電源走線上都應(yīng)該使用 RC 或 LC 濾波。電源濾波器的拐角頻率應(yīng)該對器件的 PSRR 拐角頻率和斜率進行補償,從而在整個工作頻率范圍內(nèi)獲得所期望的 PSRR 。2 p% U- S; y3 a8 f

(8)對于高速模擬信號,根據(jù)其連接長度和通信的最高頻率,傳輸線技術(shù)是必需的。即使是低頻信號,使用傳輸線技術(shù)也可以改善其抗干擾性,但是沒有正確匹配的傳輸線將會產(chǎn)生天線效應(yīng)。

(9)避免使用高阻抗的輸入或輸出,它們對于電場是非常敏感的。

(10)由于大部分的輻射是由共模電壓和電流產(chǎn)生的,并且因為大部分環(huán)境的電磁干擾都是共模問題產(chǎn)生的,因此在模擬電路中使用平衡的發(fā)送和接收(差分模式)技術(shù)將具有很好的 EMC 效果,而且可以減少串?dāng)_。平衡電路(差分電路)驅(qū)動不會使用 0V 參考系統(tǒng)作為返回電流回路,因此可以避免大的電流環(huán)路,從而減少 RF 輻射。

(11)比較器必須具有滯后(正反饋),以防止因為噪聲和干擾而產(chǎn)生的錯誤的輸出變換,也可以防止在斷路點產(chǎn)生振蕩。不要使用比需要速度更快的比較器(將 dV/dt 保持在滿足要求的范圍內(nèi),盡可能低)。

(12)有些模擬 IC 本身對射頻場特別敏感,因此常常需要使用一個安裝在 PCB 上,并且與 PCB 的地平面相連接的小金屬屏蔽盒,對這樣的模擬元件進行屏蔽。注意,要保證其散熱條件。

CPLD是Complex PLD的簡稱,顧名思義,其是一種較PLD為復(fù)雜的邏輯元件。CPLD是一種整合性較高的邏輯元件。由于具有高整合性的特點,故其有性能提升,可靠度增加,PCB面積減少及成本下降等優(yōu)點。CPLD元件,基本上是由許多個邏輯方塊(Logic Blocks)所組合而成的。而各個邏輯方塊均相似于一個簡單的PLD元件(如22V10)。邏輯方塊間的相互關(guān)系則由可變成的連線架構(gòu),將整個邏輯電路合成而成。

常見的CPLD元件有Altera公司的Max5000及Max7000系列。Cypress的Max340及Flash370系列等,一般來說CPLD元件的可邏輯閘數(shù)(gate count)約在1000~7000 Gate 之間。

電子發(fā)燒友App

電子發(fā)燒友App

評論