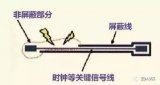

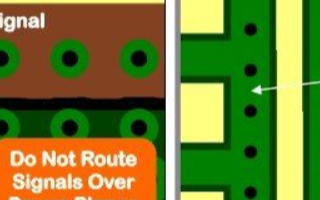

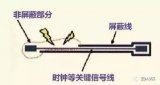

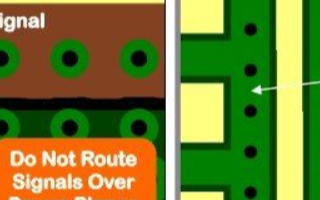

所有的高速信號必須有良好的回流路徑,盡可能地保證時鐘等高速信號的回流路徑最小,否則會極大的增加輻射,并且輻射的大小和信號路徑和回流路徑所包圍的面積成正比。

2019-04-03 09:30:51 6902

6902

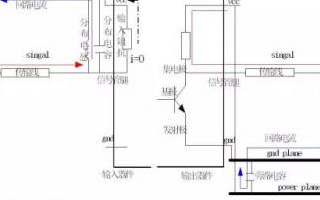

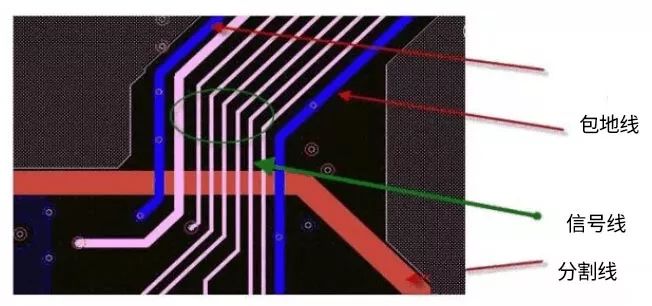

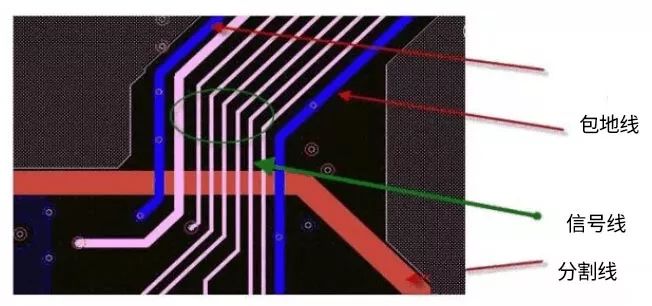

時鐘信號是由PCIE主機給到PCIE從機的,所以信號流向是指向左下角的。而此時的信號回流路徑包含包地路徑和地平面路徑。

2020-11-19 15:26:00 3513

3513 網絡搜索“什么是高速信號”或“低速信號與高速信號的區別”,出現一堆解釋,例如:

2023-12-01 17:44:41 750

750

構成諧振,即當布線長度為信號波長1/4的時候的整數倍時,此布線將產生諧振,而諧振就會輻射電磁波,產生干擾。圖7 諧振規則規則八:回流路徑規則所有的高速信號必須有良好的回流路徑。盡可能地保證時鐘等高速信號

2018-11-28 11:14:18

信號路徑設計是如何影響輸出信號的抖動性能的?為了解決這一問題,有哪些不同的設計方法?

2021-04-12 06:24:23

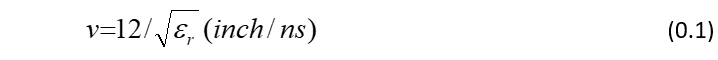

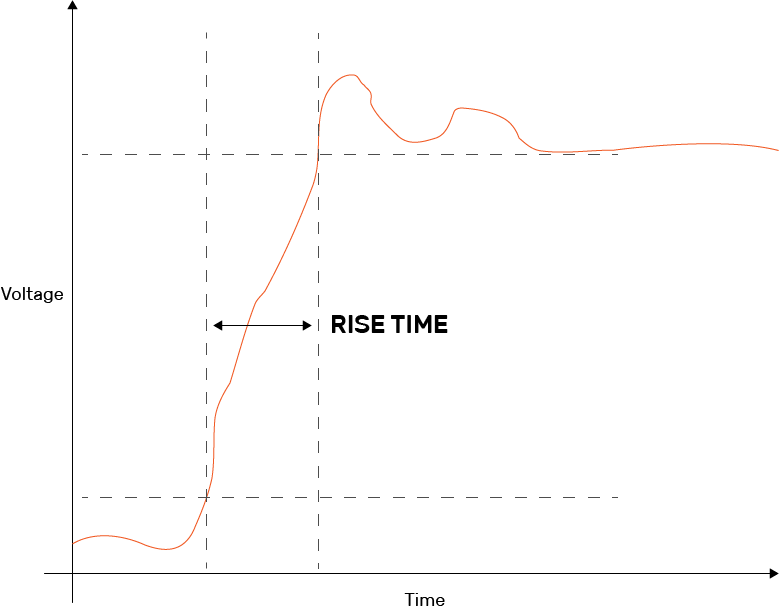

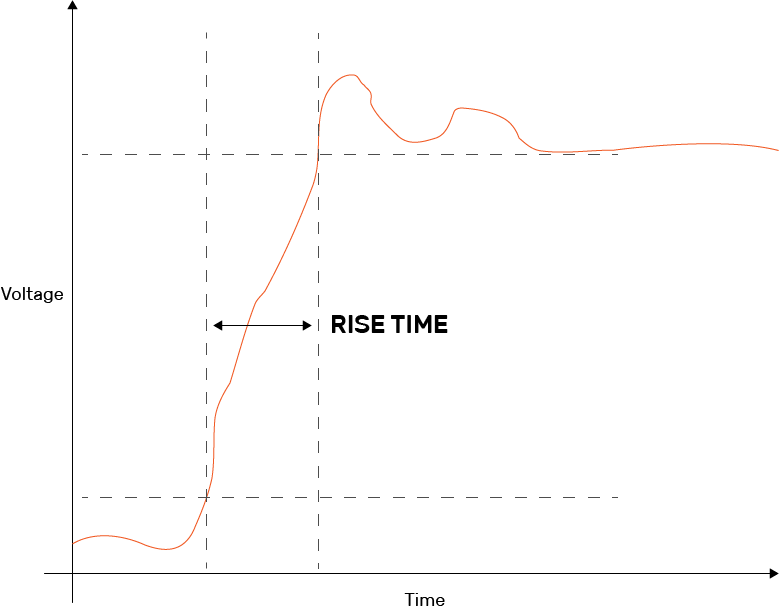

1、為什么要用信號的上升(下降)時延長短來判斷是否為高速信號?A:信號越“陡”,需要保持信號完整的頻率分量也就越多(福利葉變換可知;一般數字信號保持5倍頻最多,因為取5倍頻已經考慮到了信號90

2017-12-16 21:58:50

1、為什么要用信號的上升(下降)時延長短來判斷是否為高速信號?A:信號越“陡”,需要保持信號完整的頻率分量也就越多(福利葉變換可知;一般數字信號保持5倍頻最多,因為取5倍頻已經考慮到了信號90

2019-06-25 02:08:18

高速信號和低速信號有什么區別,怎么定義高速和低速呢

2014-12-18 10:13:52

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

高速DAP仿真器 BURNER

2023-03-28 13:06:20

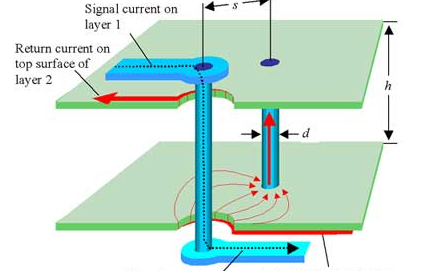

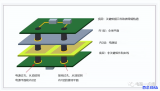

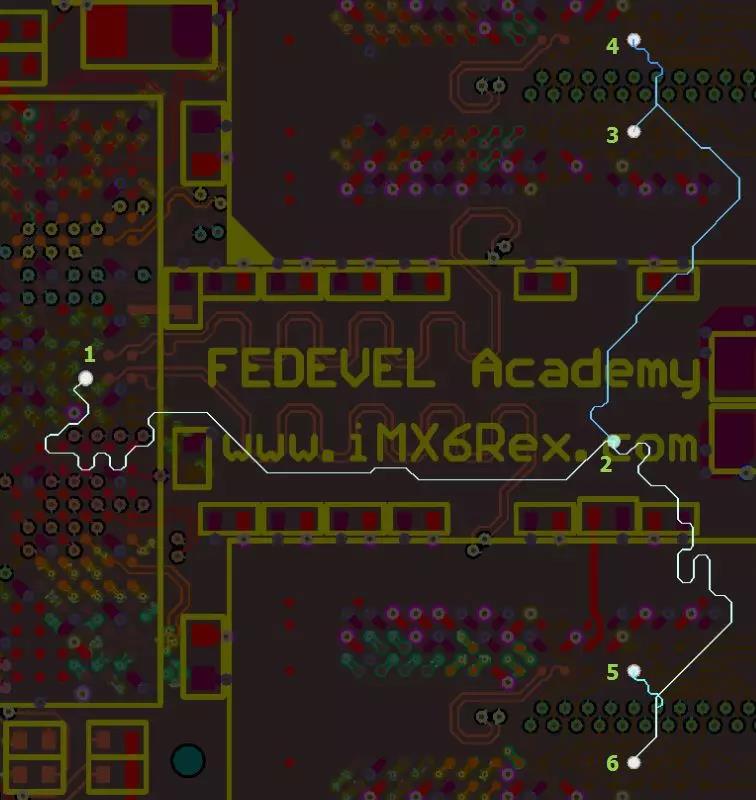

相關的圖層跟著看高速信號走線的相鄰層來確保回流路徑,管控 Layout 質量。亦或對 Layout 訂立一些走線旁該怎么加 StitchingVia 的規范,STItchingVia 的示意如下圖(三

2021-02-05 07:00:00

高速信號問題,并且不依賴昂貴而費時的電路板測試步驟,關鍵是要在電路板設計前進行大量的信號分析。當設計工程師發現這些問題后,就能通過改變布線和電路層分布、定義時鐘線的布線拓撲、選擇特定速度的元器件來保證

2018-09-10 16:37:21

:當數字信號,0不再是簡單的0,1不再是簡單的1,我們必須用模擬電路的分析方法來考慮數字信號的時候,就是高速。 各種定義很多,從心里面,還可以對高速定義為:當一個信號比你以前所設計的都快的時候,這就

2014-10-21 09:41:25

高速PCB設計常見問題問: 高速系統的定義?/ 答: 高速數字信號由信號的邊沿速度決定,一般認為上升時間小于4 倍信號傳輸延遲時可視為高速信號。而平常講的高頻信號是針對信號頻率而言的。設計開發高速

2019-01-11 10:55:05

,而無需關注FLASH處波形;星型拓撲比較菊花鏈等拓撲來講,布線難度較大,尤其大量數據地址信號都采用星型拓撲時。 >>RF布線是選擇過孔還是打彎布線 分析RF電路的回流路徑,與高速

2012-10-17 15:59:48

隨著信號上升沿時間的減小及信號頻率的提高,電子產品的EMI問題越來越受到電子工程師的關注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規則: 高速PCB設計解決EMI問題的九大規則

2016-01-19 22:50:31

和遠端串擾這種方法來研究多線間串擾問題。利用Hyperlynx,主要分析串擾對高速信號傳輸模型的侵害作用并根據仿真結果,獲得了最佳的解決辦法,優化設計目標。【關鍵詞】:信號完整性;;反射;;串擾;;近

2010-05-13 09:10:07

高速電機的命名定義:高速電機,也稱主軸電機,廣義范圍來講,高速電機又可以被稱為電主軸,高速電主軸等等,通常是指轉速超過10000r/min的電機,目前最高轉速可達300000r/min高速電機又分

2021-08-31 09:33:15

憑經驗感受一下`將同軸電纜的外導體開一個槽,會對高速信號傳輸帶來什么樣的影響。所以,在設計高速電路的過程中,要丟掉“地”這個概念,像對待信號路徑一樣對待返回路徑。 圖1 各種傳輸線橫截面 在高速

2018-11-23 16:03:32

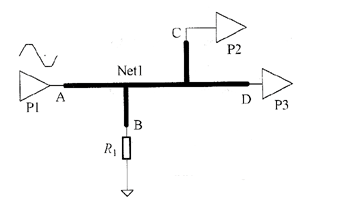

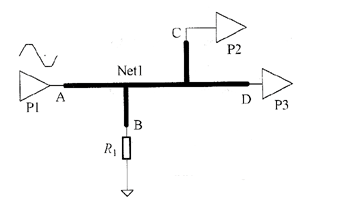

Netl。 但是,對于高速信號,如第3章所講的就完全不是這樣了,一個信號從引腳A輸出,到達D可能完全失真,而且也完全不考慮信號電流是如何返回的,所以需引入傳輸線的概念。傳輸線的原理在第3章已有詳細

2018-11-23 16:05:07

的就是高速信號,實則不然。我們知道任何信號都可以由正弦信號的N次諧波來表示,而信號的最高頻率或者信號帶寬才是衡量信號是否是高速信號的標準。信號最高頻率由信號的上升時間決定,計算公式:F=0.5/Tr

2020-12-21 09:23:34

隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的重視。高速pcb設計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。1

2021-12-31 06:22:08

做數字電路設計的朋友對差分信號的定義應該都不會太陌生,在當前比較流行的高速串行總線上,基本都是使用的差分信號。比如USB,PCIE,SATA等等。大多數的FPGA也都支持差分信號,甚至某些新型

2018-09-03 11:08:41

,是信號快速變化的上升沿與下降沿引發了信號傳輸的非預期結果。因此,通常約定如果走線傳播延時大于20%驅動端的信號上升時間,則認為此類信號是高速信號并可能產生傳輸線效應。 定義了傳輸線效應發生的前提條件

2018-11-27 15:21:01

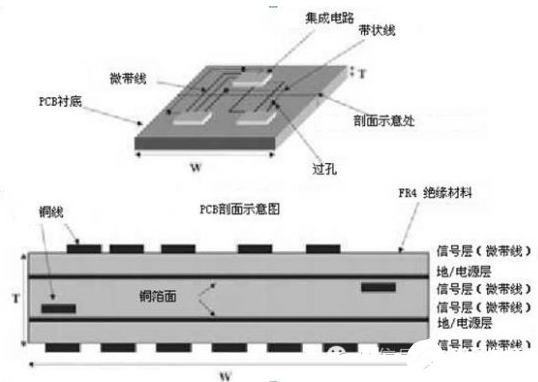

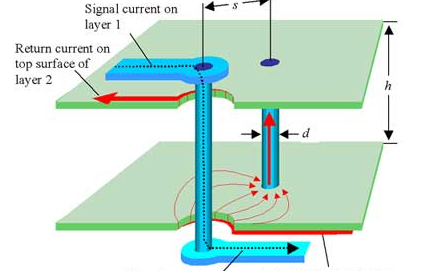

電源和地平面時留下的孔洞就給涂敷層上下表面的電流的流通通過了路徑,因此,這些信號線的回流途徑是很好的,無需采用措施來改善。② 回路電流在不同層上流動的情況包括表層第四層、表層底層、第三層第四層、第三層底層

2021-11-27 07:00:00

UART通路配置參數定義的路徑是怎樣的?

2022-02-14 06:17:15

免或減少衰減和干擾的影響。人們用分集來描述一種為發送或接收射頻(RF)信號選擇最佳路徑的策略,旨在最大限度地增加數據包將被正確接收的可能性。 我們的WiLink? 8模塊能通過使用外部雙極雙投(DPDT

2018-09-05 15:54:15

為什么要用信號的上升(下降)時延長短來判斷是否為高速信號?A:信號越“陡”,需要保持信號完整的頻率分量也就越多(福利葉變換可知;一般數字信號保持5倍頻最多,因為取5倍頻已經考慮到了信號90%的能量

2015-01-21 15:43:08

`隨著信號的沿變化速度越來越快,今天的高速數字電路板設計者所遇到的問題在幾年前看來是不可想象的。為了保證高速器件的正確動作,設計者應該消除這種電壓的波動,保持低阻抗的電源分配路徑。 為此,你需要

2018-09-20 19:46:43

補償的 SPI 主協議。它支持 SPI 時鐘頻率高達 16.7MHz 的 ADS8688 的 32 位通信協議。主要特色帶可調節信號路徑延遲補償的 SPI 主協議(無需借助外部硬件來實現信號路徑延遲

2018-11-12 17:00:36

上下表面的電流的流通通過了路徑,因此,這些信號線的回流途徑是很好的,無需采用措施來改善。 B.回路電流在不同層上流動的情況包括表層第四層、表層底層、第三層第四層、第三層底層。下面以表層底層和第三層

2020-08-01 17:30:00

、還是 GHz 速率級別的信號算高速? 傳統的 SI 理論對于“高速信號”有經典的定義。 SI:Signal Integrity ,即信號完整性。 SI 理論對于 PCB 互連線路的信號傳輸行為理解

2022-04-28 16:21:41

中,采用Cadence軟件的高速仿真工具SPECCTRAQuest,并利用器件的 IBIS模型來分析信號完整性,對阻抗匹配以及拓撲結構進行優化設計,以保證系統正常工作。本文只對信號反射和串擾進行詳細

2015-01-07 11:30:40

不然。我們知道任何信號都可以由正弦信號的N次諧波來表示,而信號的最高頻率或者信號帶寬才是衡量信號是否是高速信號的標準。信號最高頻率由信號的上升時...

2021-11-11 07:59:58

您想在高速信號上進行快速而又比較干凈(精確)的測量嗎?沒時間把探頭尖端焊接到器件上?不確定高速設計的問題來自哪兒?這些都是工程師們經常遇到的問題。隨著時間壓力越來越大,偶發問題阻礙項目竣工,您需要一種快捷、簡便、高性能的方法,來測量高速信號。

2019-08-09 08:21:46

怎樣用Sketch用戶去繪制圖形和路徑?怎樣通過UIButton去自定義路徑動畫?

2021-07-22 08:31:37

有沒有一種方法可以配置一個庫項目來導出#include 路徑、庫搜索路徑和庫名稱,這樣只要將它作為依賴項添加到另一個項目(lib 或可執行文件)就會自動將該路徑和名稱添加到依賴項目中?我問是因為我

2023-04-19 06:36:14

(cadence公司做的定義): (1)頻率大于50MHz的信號,就是高速信號 (2)信號是否高速不單單看頻率,而是信號上升/下降沿小于50ps時就認為是高速信號 (3)當信號沿著傳輸路徑傳輸,發生

2023-04-12 14:22:25

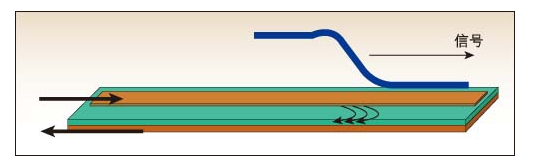

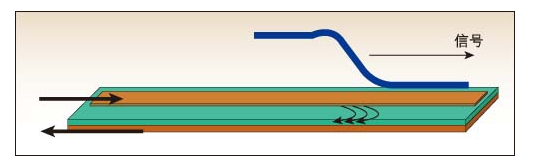

規則八:回流路徑規則 所有的高速信號必須有良好的回流路徑。盡可能地保證時鐘等高速信號的回流路徑最小。否則會極大的增加輻射,并且輻射的大小和信號路徑和回流路徑所包圍的面積成正比。 圖8 回流路徑

2018-09-20 10:38:01

就是想讀取一個高速旋轉的碼盤碼盤大概每分鐘8000轉一個碼盤有64個齒碼盤通過霍爾傳感器 輸出方波信號。我需要開讀取這個高速的方波信號。目前使用io中斷的方式讀取脈沖信號寬度 信號寬度間隔低于150us 就會讀取出錯 概率還挺高。請教各位大佬,還有其他方式來讀取這個信號嗎?

2023-03-13 06:27:53

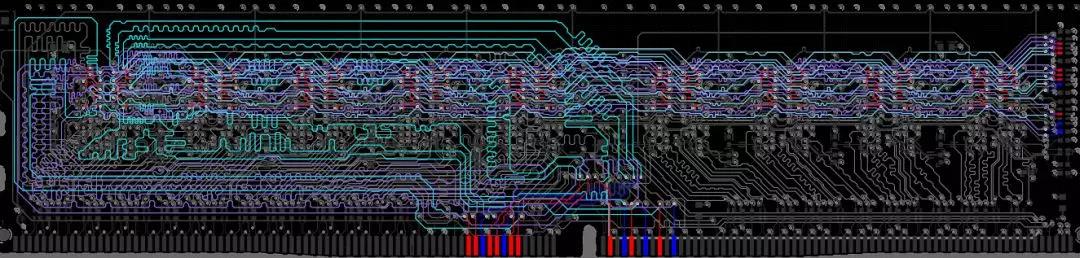

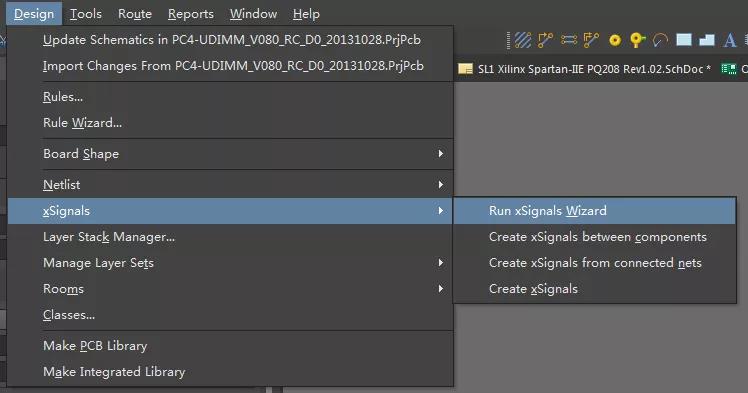

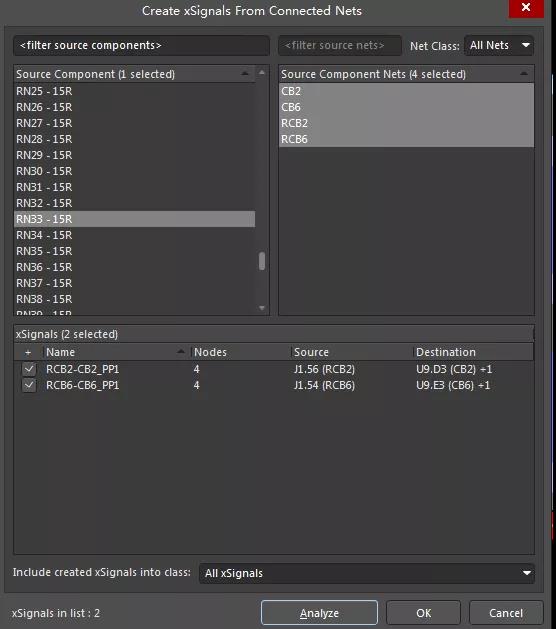

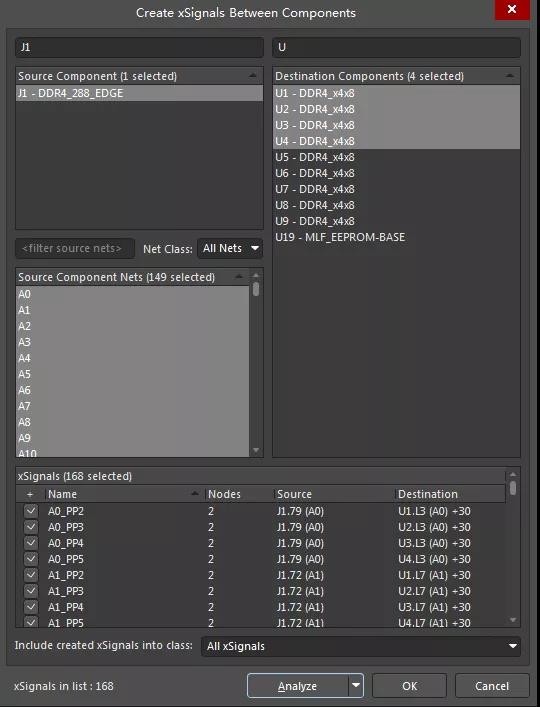

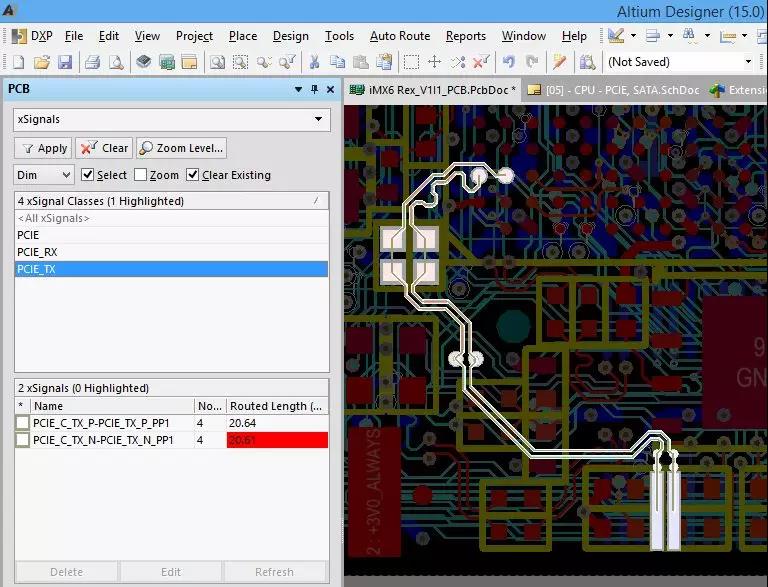

請問下AD中From to Editor與xSignals具體兩個功能有什么區別?

2019-02-25 12:13:14

如何加強信號路徑的性能?

2021-04-22 06:06:19

算高速、還是 GHz 速率級別的信號算高速?傳統的 SI 理論對于“高速信號”有經典的定義。SI:Signal Integrity ,即信號完整性。SI 理論對于 PCB 互連線路的信號傳輸行為理解

2020-11-30 09:51:58

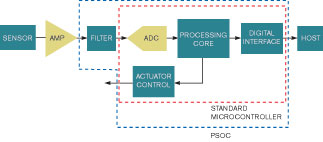

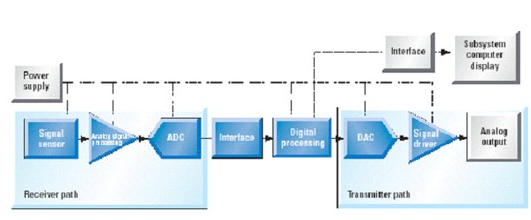

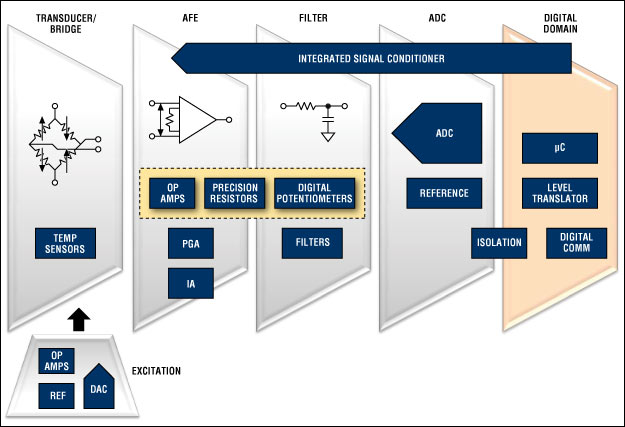

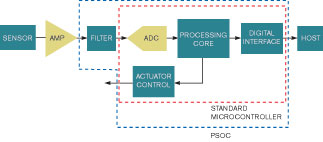

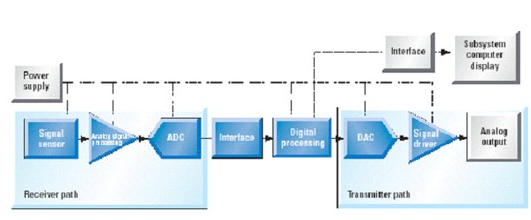

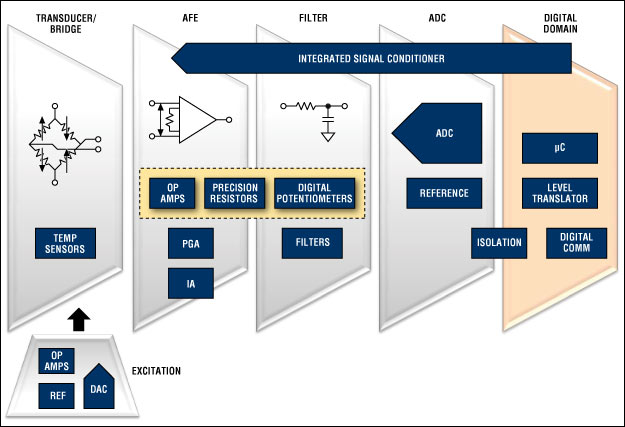

如何加強信號路徑的性能:信號路徑的設計為系統設計工程師提供不少可供他們發揮的機會。以設有仿真/數字轉換器的信號路徑為例來說,工程師進行設計時不但要為傳感器提供緩

2009-09-23 19:29:54 23

23 焊盤對高速信號的影響

焊盤對高速信號有的影響,它的影響類似器件的封裝對器件的影響上。詳細的分析

2009-03-20 13:48:28 1507

1507 多高的頻率才算高速信號?

當信號的上升/下降沿時間< 3~6倍信號傳輸時間時,即認為是高速信

2009-04-15 00:41:34 6451

6451 高速信號走線規則教程

隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的關注。高速PCB設計的成功,對EMI

2009-04-15 08:49:27 2798

2798

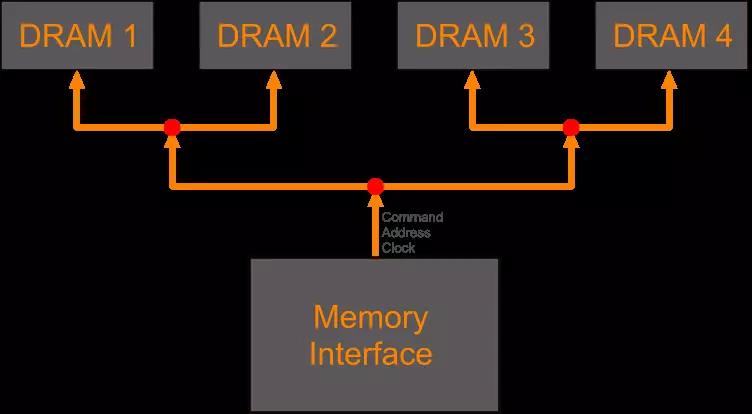

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-04-24 16:05:19 1274

1274

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-05-01 11:14:27 1655

1655

傳感器的信號路徑

理解了一個模擬信號路徑后,數字系統開發者就可以從各種應用中,更精確地捕捉傳感器數據。要點 即使同一家制造商的類似傳感器

2010-01-08 11:50:21 679

679

高速模數轉換器(ADC)的參數定義和描述如表1所示。

表1 動態參數定義

2010-12-21 11:13:07 1535

1535

本文以高速系統的差分信號回流路徑為基本出發點, 著重介紹了差分信號的參考平面的開槽間隙對回流路徑的影響。通過Ansoft-HFSS 對信號回路進行建模與參數分析;提取全波模型,在H

2011-11-09 09:33:14 85

85 回流路徑與傳輸線模型建構及信號完整性分析

2011-12-20 17:37:57 51

51 差模信號干擾和共模信號干擾的定義

2017-04-21 09:54:00 22

22 為解決無線移動自組織網絡存在的資源路徑遞歸困難,控制開銷巨大等實際部署難題。基于動量自優機制,本文提出了一種資源路徑高速遞歸算法。首先通過分布在網絡中的節點動量的監測,綜合計算路徑高速遞歸過程中

2017-11-11 17:32:43 0

0 在設計高速混合信號系統時,一步一步地通過整個鏈對塊級信號強度進行評估是一個很好的工程實踐。信號路徑設計者的首要問題是輸入或接收器路徑的設計。發射機或輸出路徑將在未來的問題中討論。典型的接收機或測量

2018-05-15 15:38:21 4

4 信號路徑為系統設計者提供了許多機會。在模數轉換器(ADC)信號路徑中,在緩沖傳感裝置、對ADC的開關電容輸入充電和最小化噪聲源方面做出良好的設計選擇將使性能最大化。所有這些例子將在信號路徑設計器的這個問題中得到解決。

2018-05-24 17:09:26 1

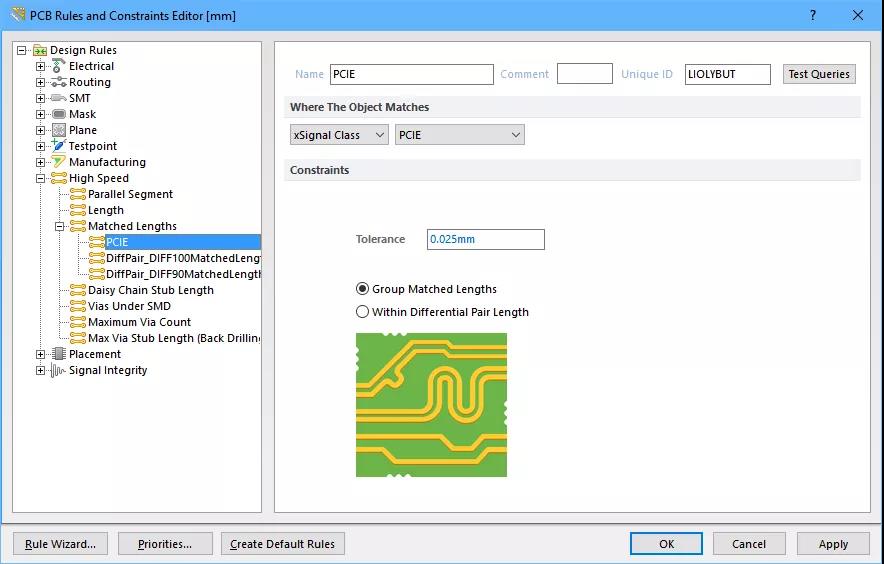

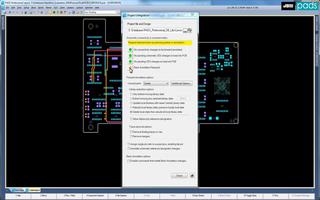

1 用于管理電路板制造標準和高速信號布線,以免 Layout 設計中發生干擾和/或串擾的規則對于最終電路板裝配的成敗至關重要。約束管理針對原理圖輸入和 Layout 提供了通用的集成式約束定義環境,使您可以輕松地將 PCB Layout“實際”布線值與定義的規則集進行比較。

2019-05-17 06:30:00 2315

2315

關注的問題,當時TTL足夠快,路徑變長。這就是我們如何在信號完整性方面定義高速度;當信號路徑相對于上升時間較長時,PCB是高速的,當信號從開放端反射并導致問題時,路徑變長。

2019-07-28 10:08:13 3799

3799 數字電路通常借助于地和電源平面來完成回流。高頻信號和低頻信號的回流通路是不相同的,低頻信號回流選擇阻抗最低路徑,高頻信號回流選擇感抗最低的路徑。

2020-04-13 17:37:15 3709

3709

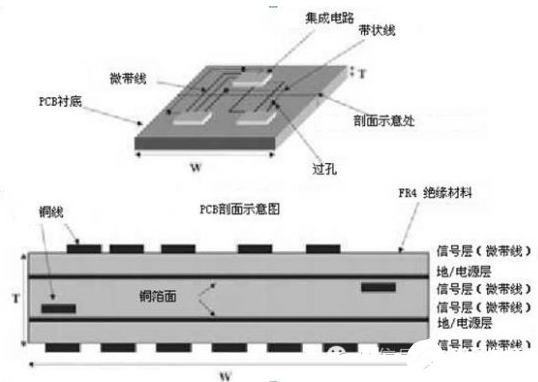

傳輸線的定義是有信號回流的信號線(由兩條一定長度導線組成,一條是信號傳播路徑,另一條是信號返回路徑。),最常見的傳輸線也就是我們PCB板上的走線。

2019-12-17 17:22:08 1943

1943

低速信號中,各個點的電平相差不大,但高速信號中,需要用分布式的思維來考慮問題,在傳輸路徑中,每個點的路徑相差很大,所以高低速信號的劃分還與信號的傳輸路徑有關。

2019-08-20 09:47:19 9288

9288 高速信號不遵循阻力最小的路徑;他們遵循阻抗最小的路徑。本系列文章介紹了下一個項目的PCB設計布局。

2019-09-15 15:58:00 2766

2766

GHz速率級別的信號算高速? 傳統的SI理論對于高速信號有經典的定義。 SI:Signal Integrity ,即信號完整性。 SI理論對于PCB互連線路的信號傳輸行為理解,信號邊沿速率幾乎完全決定了信號中的最大頻率成分,通常當信號邊沿時間小于4~6倍的互連傳輸延時的情況

2019-11-05 11:27:17 10310

10310

信號上升時間并不是信號從低電平上升到高電平所經歷的時間,而是其中的一部分。業界對它的定義尚未統一,最好的辦法就是跟隨上游的芯片廠商的定義,畢竟這些巨頭有話語權。

2019-11-25 15:56:41 2526

2526

當設計高速的混合信號系統時,我們最好先審視信號路徑的每一環節,詳細評估各區塊的信號失真程度。本文將集中討論輸入路徑設計的模擬及混合信號部分。我們必須小心挑選信號路徑的各個區塊,才可取得預期的成效。

2020-07-17 09:50:03 732

732

變得越來越重要。 為了達到通常所說的 SI 的信號完整性,需要明確定義 PCB 路徑。這些明確定義的路徑又使信號可以在正確的時間從驅動器傳遞到接收器。另一方面,如果設計的 SI 較差,則不太可能在正確的時間傳遞信號。還已知不良的 S

2020-09-22 21:19:41 617

617 高速電路設計中的信號衰減是讓人頭疼的一件事,作為電路設計工程師在布線時應該降低信號衰減。本文主要介紹高速電路設計中降低信號衰減方法,希望對你有所幫助。 一、降低電抗路徑 在高速電路設計中,將接地

2021-01-28 11:06:26 2677

2677 來源:羅姆半導體社區 提到“高速信號”,就需要先明確什么是“高速”,MHz速率級別的信號算高速、還是GHz速率級別的信號算高速? 傳統的SI理論對于“高速信號”有經典的定義。SI:Signal

2022-12-12 16:56:35 6009

6009 切換有用信號來傳輸準確的信息。 讓我們嘗試找出如何確定高速信號。從信號完整性專家的角度來看,它與 常規電信號有何不同。 定義高速的一般方法 幫助定義信號是否可以稱為高速的一般經驗法則是檢查其頻率。工程師經常可以將信號在

2020-10-12 20:42:17 2289

2289

高速信號鏈選擇指南

2021-04-24 12:19:08 14

14 作者:Loren Siebert 1

?

您是否注意到了差分信號在高性能信號路徑中正日益占據主導地位?差分信號可提供多種優勢!我一直在考慮這樣一個事實,即每個差分信號路徑都有一個與其相關的寄生

2021-11-23 17:57:59 1122

1122 高速信號不遵循阻力最小的路徑;它們遵循阻抗最小的路徑。本系列文章為您的下一個項目提供有關 PCB設計布局的想法。

2022-05-07 16:12:39 1470

1470

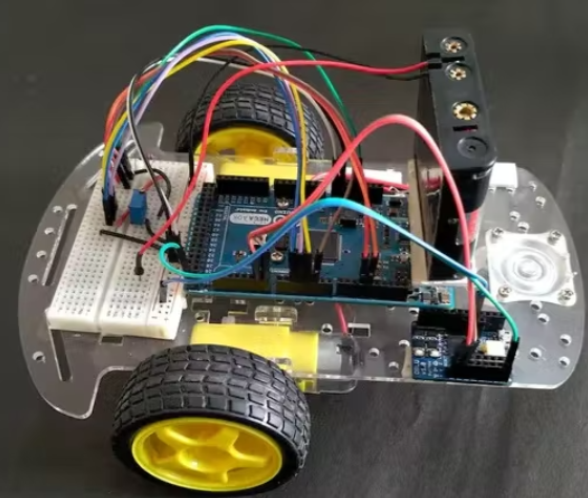

該項目旨在讓機器人在預先定義的路徑上精確移動,無需使用GPS或WiFi或藍牙進行定位,甚至無需地圖或建筑布局規劃。并實時繪制其實際路徑(按比例)。藍牙可以代替有線,用于傳輸實時位置信息。

2022-06-07 11:24:02 2350

2350

然而,高速電路是什么,什么信號才屬于高速信號?這是筆者曾在一次面試中被問到過的一個問題,當時腦袋中迅速閃過圖像數據處理、音頻處理等設計,但是如何定義所謂的“高速”卻一下子想不出來如何定義這個基本概念。

2022-06-24 11:16:50 6006

6006 在工作中經常會遇到有人問什么是高速電路,或者在設計高速電路的時候需要注意什么。每當遇到這種問題就頭腦發懵,其實不同的產品、不同的人對其都有不同的理解。今天簡單總結一下最基本的一些概念包括對高速電路的理解、什么是信號完整性還有信號的帶寬等。

2022-07-13 09:09:32 1147

1147 本文結合實際測試中遇到的時鐘信號回溝問題介紹了高速信號的概念,進一步闡述了高速信號與高頻信號的區別,分析了25MHz時鐘信號沿上的回溝等細節的測試準確度問題,并給出了高速信號測試時合理選擇示波器的一些建議。

2022-09-14 09:20:17 3153

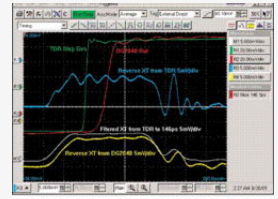

3153 用于測量信號路徑質量的時域反射 (TDR) 技術

2022-11-15 19:49:54 6

6 跨分割,對于低速信號可能沒有什么關系,但是在高速數字信號系統中,高速信號是以參考平面作為返回路徑,就是回流路徑。

2023-02-21 13:44:36 1168

1168 本教程介紹了用于壓力、溫度、電流、光線和接近檢測的最常用傳感器類型的傳感器信號鏈。本文介紹了選擇信號路徑的復雜性。示例電路和框圖可幫助讀者選擇一組最佳零件以滿足其設計需求。

2023-02-27 16:19:21 564

564

對低速信號而言,由于傳輸路徑上各點電平近似相同,采用集總式思維來看待傳輸路徑,即傳輸路徑上各點的狀態相同,在分析時,可被集中成一點; 對高速信號而言,傳輸路徑上各點的電平不同,需采用分布式思維來看待傳輸路徑,即不能將傳輸路徑集中成一點來對待,而應視為多個狀態不同的點。

2023-03-08 13:32:00 1661

1661

? 隨著信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的重視。高速pcb設計的成功,對EMI的貢獻越來越受到重視,幾乎90%的EMI問題可以通過高速PCB來控制

2023-05-22 09:15:58 836

836

ReturnPath(回流路徑)以高頻信號而言,回流(retrunpath)將沿低阻抗路徑走,所以差動信號線參考的是臨近的單一Groundplane如此可以減少差動阻抗的改變及降低EMI

2022-09-20 09:42:55 611

611

但是,對于高速信號,如第3章所講的就完全不是這樣了,一個信號從引腳A輸出,到達D可能完全失真,而且也完全不考慮信號電流是如何返回的,所以需引入傳輸線的概念。傳輸線的原理在第3章已有詳細介紹,在此僅澄清概念上的混淆。

2023-08-28 14:49:03 1406

1406

高速信號不遵循阻力最小的路徑;它們遵循阻抗最小的路徑。本系列文章為您的下一個項目提供有關 PCB 設計布局的想法。

2023-09-01 09:26:46 406

406

今天給大家分享的是:高速信號、14條高速信號布局設計規則。

2023-09-07 09:19:57 454

454

可以很好的決定布線的走向和結構,電源與地之間的分割,以及電磁干擾和噪聲的控制。 不過在理解高速PCB設計前,需要知道什么是高速信號。 一般如果符合以下幾點,那它就可以被認為是高速信號(cadence公司做的定義): (1)頻率大于

2023-11-06 10:04:04 341

341

,對正常的信號傳輸和系統性能產生不良影響。 信號回流路徑是一個普遍存在的問題,尤其在高速電子設備中更為突出。信號的回流可能是因為傳輸線路或布線不良造成的,也可能是由于高頻器件之間存在不良的反射或耦合引起的。它會

2023-11-24 14:44:50 618

618 ,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。 跨分割現象示意圖 跨分割,對于低速信號可能沒有什么關系,但是在高速數字信號系統中,高速信號是以參考平面作為返回路徑,就是回流路徑。當參考平面不完整的時

2023-12-04 10:26:34 288

288

傳輸線的定義是有信號回流的信號線(由兩條一定長度導線組成,一條是信號傳播路徑,另一條是信號返回路徑。),常見的傳輸線也就是我們PCB板上的走線。

2024-01-02 15:36:09 114

114

高速信號眼圖測試的基本原理? 高速信號眼圖測試是一種用于衡量和分析高速數字信號的測試方法。在電子通信領域,高速信號是指傳輸速率較快的數字信號,例如10 Gbps或更高的速率。 高速信號眼圖測試

2024-02-01 16:19:49 142

142

電子發燒友App

電子發燒友App

評論