1概述

當今計算機系統DDR3存儲器技術已得到廣泛應用,數據傳輸率一再被提升,現已高達1866Mbps.在這種高速總線條件下,要保證數據傳輸質量的可靠性和滿足并行總線的時序要求,對設計實現提出了極大的挑戰。

本文主要使用了Cadence公司的時域分析工具對DDR3設計進行量化分析,介紹了影響信號完整性的主要因素對DDR3進行時序分析,通過分析結果進行改進及優化設計,提升信號質量使其可靠性和安全性大大提高。

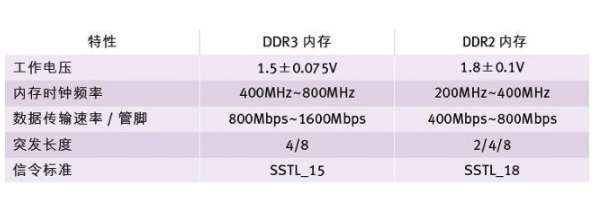

2 DDR3介紹

DDR3內存與DDR2內存相似包含控制器和存儲器2個部分,都采用源同步時序,即選通信號(時鐘)不是獨立的時鐘源發送,而是由驅動芯片發送。它比DR2有更高的數據傳輸率,最高可達1866Mbps;DDR3還采用8位預取技術,明顯提高了存儲帶寬;其工作電壓為1.5V,保證相同頻率下功耗更低。

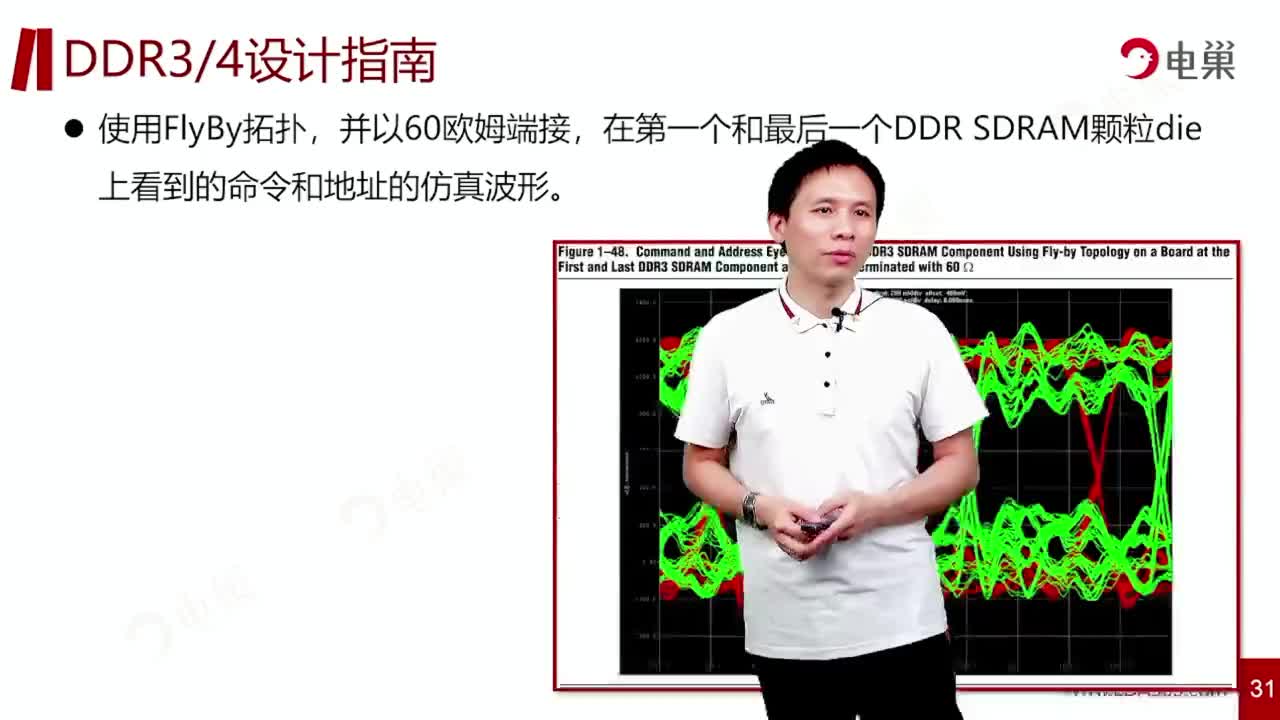

DDR3接口設計實現比較困難,它采取了特有的Fly-by拓撲結構,用“Write leveling”技術來控制器件內部偏移時序等有效措施。雖然在保證設計實現和信號的完整性起到一定作用,但要實現高頻率高帶寬的存儲系統還不全面,需要進行仿真分析才能保證設計實現和信號質量的完整性。

3仿真分析

對DDR3進行仿真分析是以結合項目進行具體說明:選用PowerPC 64位雙核CPU模塊,該模塊采用Micron公司的MT41J256M16HA—125IT為存儲器。Freescale公司P5020為處理器進行分析,模塊配置內存總線數據傳輸率為1333MT/s,仿真頻率為666MHz.

3.1仿真前準備

在分析前需根據DDR3的阻抗與印制板廠商溝通確認其PCB的疊層結構。在高速傳輸中確保傳輸線性能良好的關鍵是特性阻抗連續,確定高速PCB信號線的阻抗控制在一定的范圍內,使印制板成為“可控阻抗板”,這是仿真分析的基礎。DDR3總線單線阻抗為50Ω,差分線阻抗為100Ω。

設置分析網絡終端的電壓值;對分析的器件包括無源器件分配模型;確定器件類屬性;確保器件引腳屬性(輸入\輸出、電源\地等)。

3.2電路前仿真分析

前仿真分析的內容主要是在PCB設計之前對電路設計的優化包括降低信號反射、過沖,確定匹配電阻的大小、走線阻抗等,通過對無源器件的各種配置分析選取出最適合的參數配置。

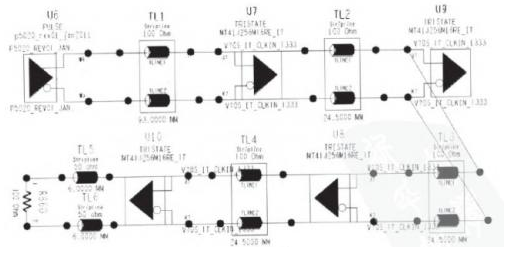

圖1時鐘線的拓撲結構(點擊查看大圖)

(1)DDR3總線的差分時鐘分析

眾所周知,在差分傳輸中,所有信息都是由差模信號來傳送的,而共模信號會輻射能量并能顯著增加EMI,因此保證差分信號的質量十分重要,應使共模信號的產生降到最低。在對差分時鐘分析時不僅要關注其本身的信號質量,由于其它信號都是以差分時鐘的來采樣數據,因此還需關注其單調性、過沖值等。

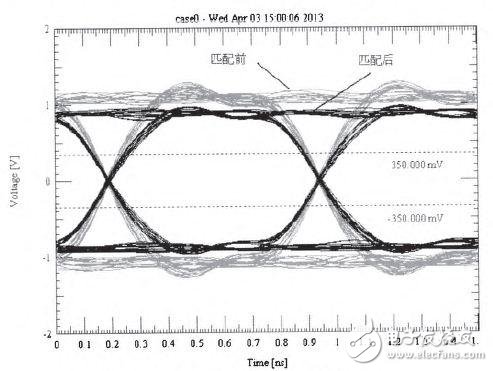

本例中差分時鐘的fly—by拓撲結構與地址總線一樣為串聯方式,如圖l對處理器P5020驅動4個DDR3內存芯片的時鐘拓撲結構,在終端進行簡單的電阻匹配,在PCB板上差分走線后,進行反射分析發現接收端反射波形上下過沖較大。在處理器輸出端選用正確的下拉匹配電阻,雖電壓幅值略有減少,但上下過沖明顯減少消除了反射干擾,即減少了差分線的共模分量。對比分析結果如圖2.

圖2接收端DDR3的反射波形

(2)驗證驅動能力和ODT選項

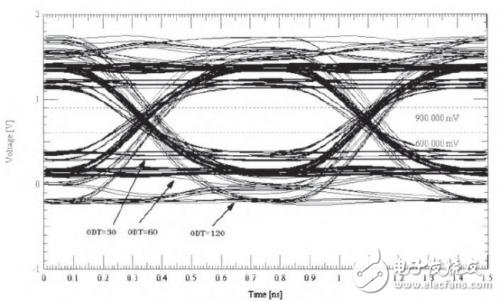

DDR3內存總線數據信號的驅動能力分為FULL和HALF兩種模式,內部終端電阻(ODT)選擇也有0Ω、20Ω、30Ω、40Ω、60Ω、120Ω選項,它們分別對應不同的模型用于控制信號反射的影響。為提高信號質量、降低功耗,可通過分析不同模式選取正確的參數模型。

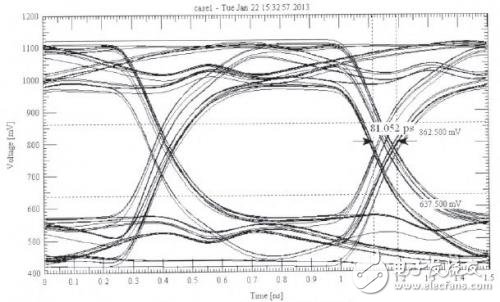

取數據總線對不同的ODT選項進行分析。圖3是在不同ODT設置進行分析數據信號形成的眼圖波形,從圖中可以看出:ODT阻抗越高,在相同驅動激勵和走線等情況下轉換率越高,幅度越大;在選擇ODT=60Ω,其接收波形平緩信號質量最好,無明顯抖動和過沖,抖動最小。

圖3數據信號眼圖波形

通常串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲干擾。它生成前向串擾與后向串擾,其對信號波形主要影響在幅度和邊沿上面。

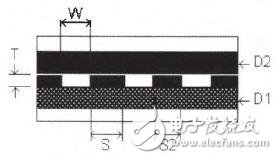

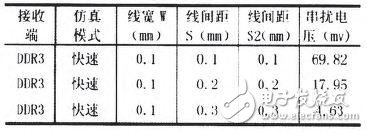

從DDR3數據總線提取3根相鄰線,中間一根為被攻擊網絡,周圍2根為攻擊網絡,采用3線模型進行分析,如下圖4走線排列,其受害線為中間走線保持低電平,兩邊的為攻擊線,采用128位偽隨機碼,根據走線的不同線寬和線間距對其進行串擾分析,看其分析結果如下表1.

圖4走線剖面圖

表1串擾分析結果

從表1可看出間距越大串擾影響越小,這里我們遵循的3W原則即走線邊沿間距S是線寬W的3倍將大大減少串擾的影響。但間距增大將犧牲布線空間,因此需綜合考慮使在有限的空間中布線最優化。

3.3時序分析

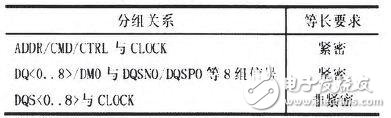

DDR3是并行總線,其時序屬源同步系統,在滿足信號質量的前提下,也必須滿足時序要求。對于源同步時鐘,驅動芯片的數據和時鐘信號由內部電路提供即數據和時鐘并行傳輸。DDR3對不同的時序關系采用分組設計,其時序關系如表2.

表2時序分組關系

源同步時序計算公式:

Tsetup_margin=Tvb—Tsetup—Tskew

Thold_margin=Tva—Thold—Tskew

公式中:Tsetup margin\Thold_margin:建立時間余量\保持時間余量,Tvb\Tva:驅動端的建立時間和保持時間,Tsetup\Thold接收端的建立時間和保持時間,Tskew:指數據、地址信號參考時鐘引起的偏移。其中Tvb\Tva,Tsetup\Th01d參數值都是能從器件手冊中獲取,關鍵是數據與選通信號飛行時間的時序偏移(skew),包含驅動端輸出的偏移和在PCB板上的走線長度的偏移,需通過時序仿真非理想隨機碼進行分析計算得出。

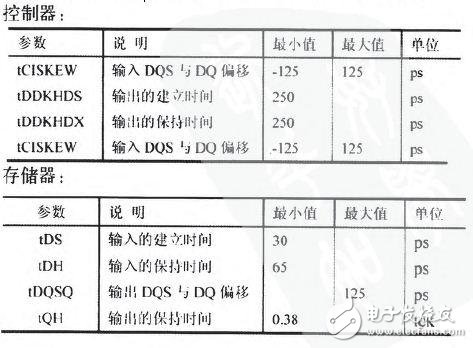

以DDR3數據讀寫操作為例,根據下表芯片資料中的時序參數進行靜態時序裕量的計算,獲得PCB設計的時序控制規則。

表3仿真所需要的時序參數(數據率:1333MHz)控制器:

寫操作:

Tsetup_margin=0.25—0.03=0.22ns

Thold_margin=0.25-0.065=0.185ns

讀操作:

Tsetup_margin = Thold_margin=(0.38*1.5-0.125)/2 - 0.125=97.5ps

上述計算值是理論上的時序余量,其實源同步時序除本身芯片自身固有特性所帶來的延時外還受其他因素的影響,都屬于偏移范圍,主要包括:

(1)高速總線造成的信號完整性問題如串擾、同步開關噪聲、碼間干擾(ISI)等影響,需通過信號仿真分析來估算。

(2)高速總線互連所產生的時序偏斜:主要是信號總線互連鏈路中的布線誤差,整個鏈路含器件封裝內部走線、pcb板上走線和走線過孔等產生的時序偏差,可通過等長布線來控制其時序偏斜。

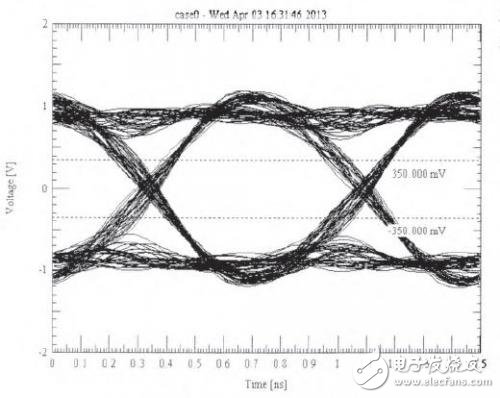

對8位數據總線DQ進行分析,選取一根數據線為受害線,其余數據線為反向偽隨機碼,條件設為最快驅動,在此最壞情況進行綜合仿真,查看其受擾線的波形情況。

比較圖5、圖6后可看出此數據線受到各方面的因素綜合影響,使波形眼圖中的眼高和眼寬都相應減小,導致數據總線時序裕量大大減少。上述時序裕量需減去此值再考慮其他噪聲因素,結合經驗留些時序余量后,就可把時序余量轉換成PCB設計時的布線長度約束(約6in/ns)。

圖5 DO數據總線理想波形

圖6 DQ數據總線最壞情況下的實際波形

4 PCB設計

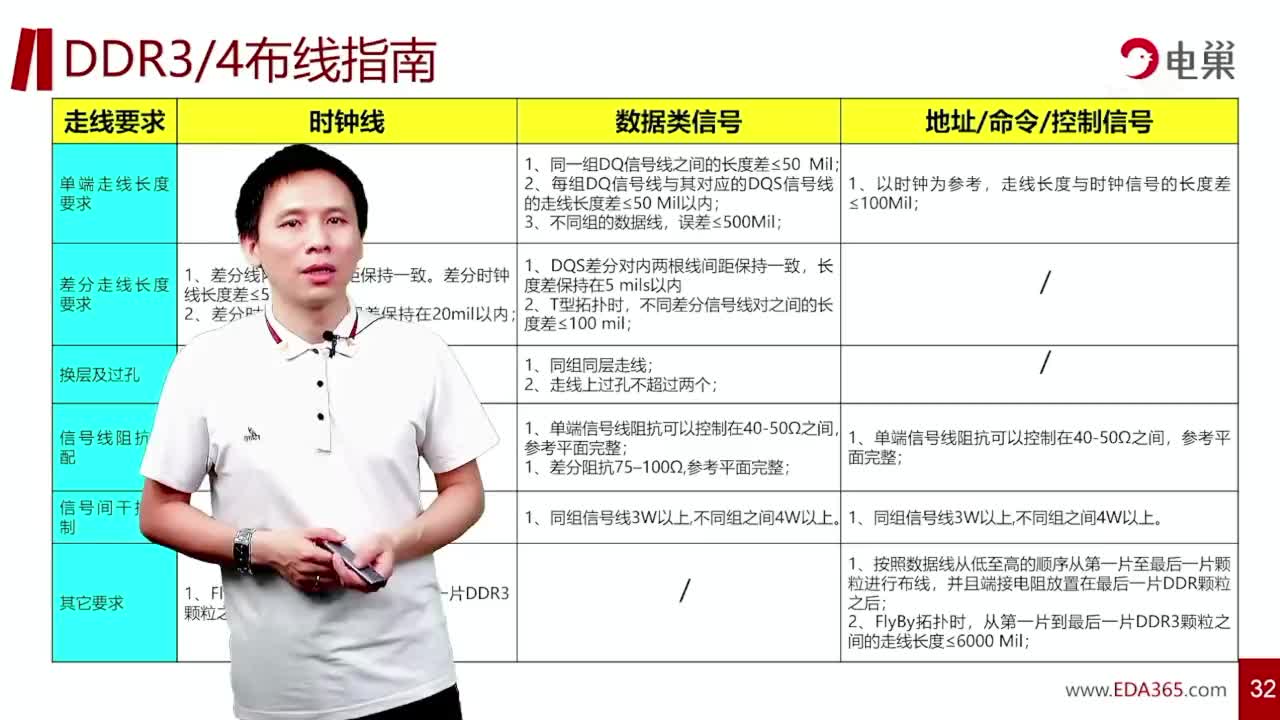

4.1設計規則約束

(1)等長約束

采用分組等長方式,分組如下:

數據線與DQS、DM信號組:64位數據線按8位一組,每組分別對應其各自的DQS和DM信號;由于數據時序余量最小,組內嚴格控制延時,以對應的DQS為基準,等長精度在±10mil.

地址線、控制線、時鐘線組:需等長控制,地址線與控制線各分支的誤差±20mil,它們與時鐘線誤差在±100mil,差分時鐘線之間±5rail.

(2)間距約束

DDR3同組線間的間距保持在2倍線寬;不同組類線的間距保持在3倍線寬;DDR3線與其他jBDDR3線之間的間距應大于50mil,用于串擾控制。

(3)線寬約束

根據傳輸線阻抗要求和印制板疊層結構計算走線線寬,設置走線線寬規則,保證阻抗的一致性。

4.2布線技巧

同組內總線盡量同層走線,時鐘線與地層相鄰;盡量少用過孔,如用需組內過孔數相同,保證其一致性;相鄰信號走線需交叉,避免長距離的重疊走線,如相鄰層間距足夠大,可適當降低要求;

走線避免采用直角應用45.斜線或圓弧角走線;盡量采用3W原則走線;

與電源層相鄰的信號層中的高速走線應避免跨電源\地平面;

電源層比地層內縮20H(H:電源層與地層的介質厚度);不允許有孤立銅的存在。

5 PCB板后仿驗證

DDR3的PCB設計結束后進行后仿分析,用以對前面的仿真分析進行驗證。PCB板后仿主要是對DDR3信號質量和時序關系進行分析。

5.1 DDR3的差分時鐘驗證

DDR3差分時鐘在PCB布線后對其后仿真分析,抽取一對實際時鐘走線對所走鏈路進行分析其波形如下圖7:其單調性和上下過沖都滿足要求。

圖7:差分時鐘PCB走線波形圖8數據總線寫時序

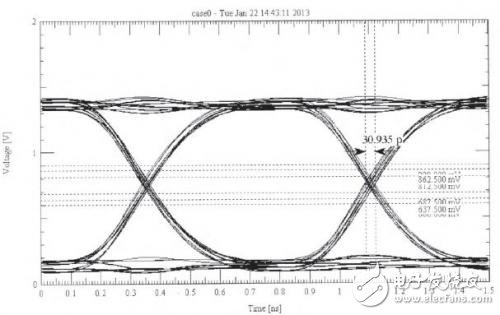

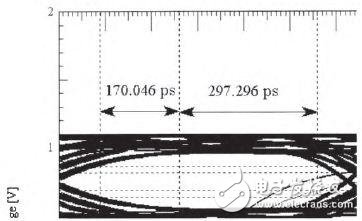

5.2 DDR3的時序驗證

對于布線后的時序驗證也是十分重要的環節。在確定好同步信號組及對應的選通信號后利用Cadence軟件的BUS setup功能進行綜合分析,位數據總線及相應的DQS信號,設定時鐘頻率666MHz,設定相應ibis模型,加入隨機碼流,最終進行分析后可通過測量得到時序參數可計算時序裕量,驗證PCB布線是否滿足相關的時序關系。分析結果見圖8.

圖8數據總線寫時序

從上圖8可測量出數據總線的建立時間和保持時間,根據DDR3數據相應時序進行靜態時序計算,再綜合考慮其余因素對時序的影響來估算包括其PCB走線長度引起的偏移等,滿足其DDR3接收端的建立時間和保持時間的時序正確性,其它時序關系類似可通過此驗證。

6結束語

通過上述Power PC模塊的DDR3內存設計分析,了解高速信號反射、串擾、時序等因素對其設計的影響,其仿真分析成為增強計算機系統設計可靠性和穩定性的必要手段,為設計高速數字電路保駕護航。

來源;電子設計技術

電子發燒友App

電子發燒友App

評論