在制造行業(yè),工藝設(shè)計師通過 EDA 軟件將 PCB 設(shè)計完成之后,是否需要對設(shè)計成果進行檢驗?回答是肯定的,而且檢驗不止一種。 第一種是 DRC 檢驗。 DRC 檢查也叫設(shè)計規(guī)則檢查,是 PCB

2018-03-09 10:12:15 6066

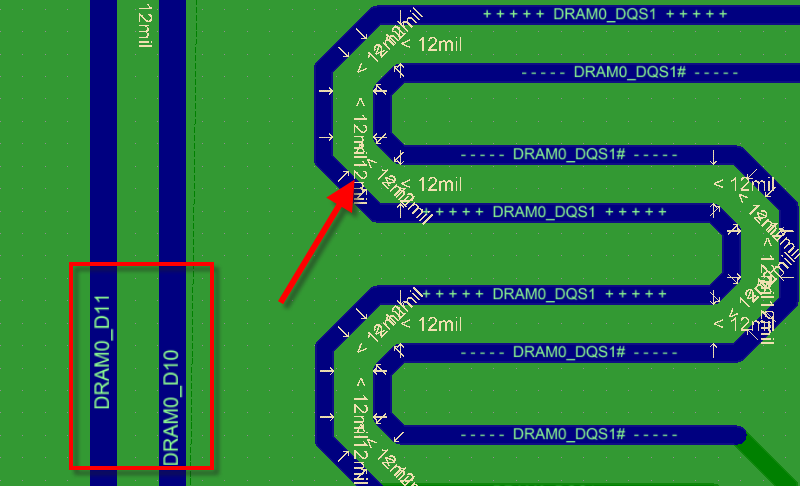

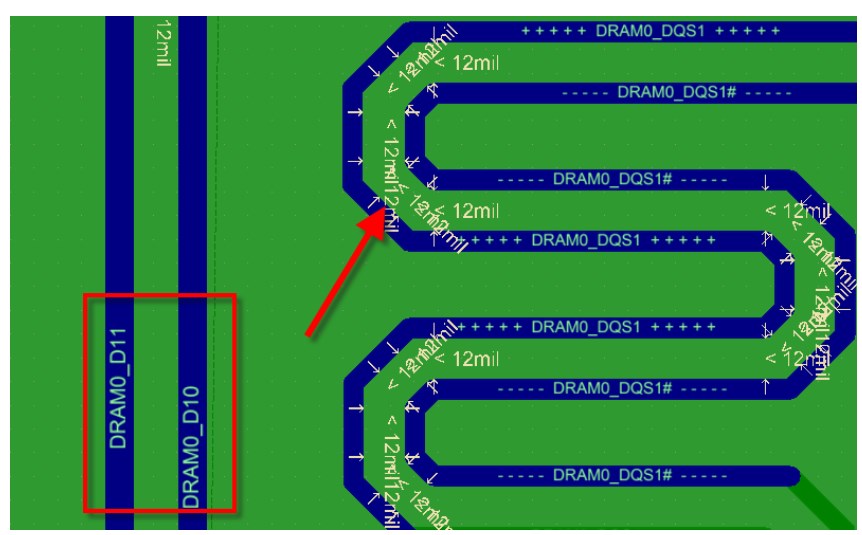

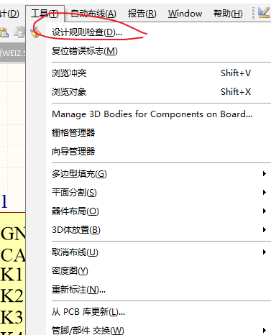

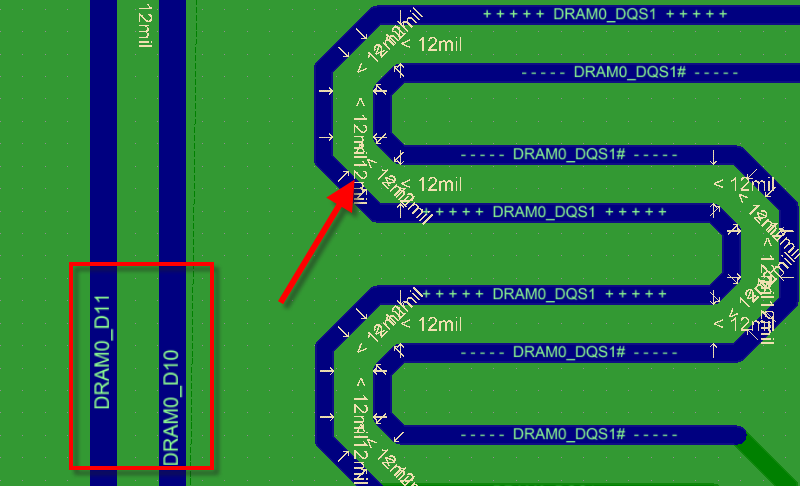

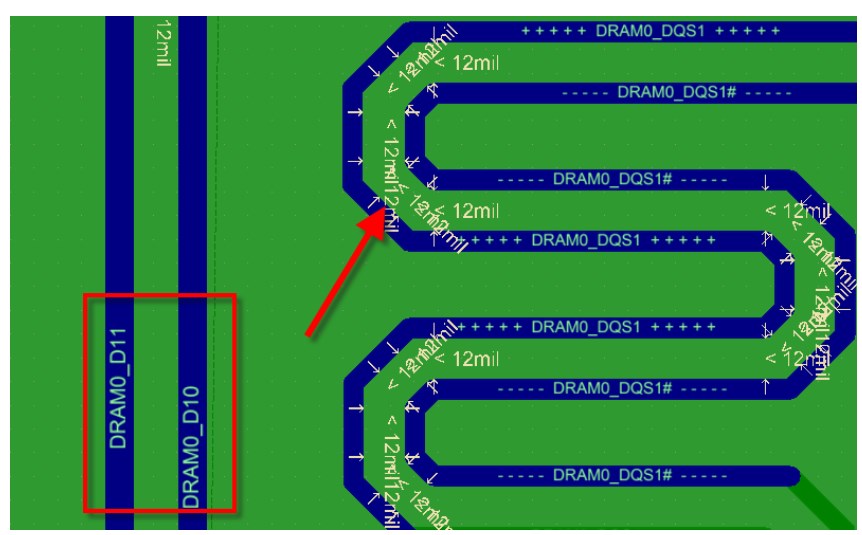

6066 為了盡量減小單板設(shè)計的串擾問題,PCB設(shè)計完成之后一般要對線間距3W規(guī)則進行一次規(guī)則檢查。一般的處理方法是直接設(shè)置線與線的間距規(guī)則,但是這種方法的一個弊端是差分線間距(間距設(shè)置大小不滿足3W規(guī)則

2020-04-22 15:26:26 15165

15165

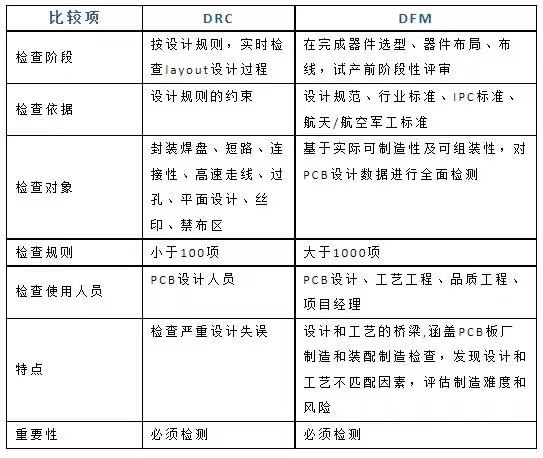

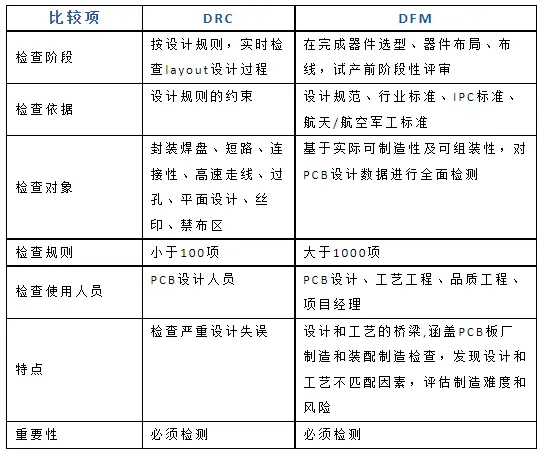

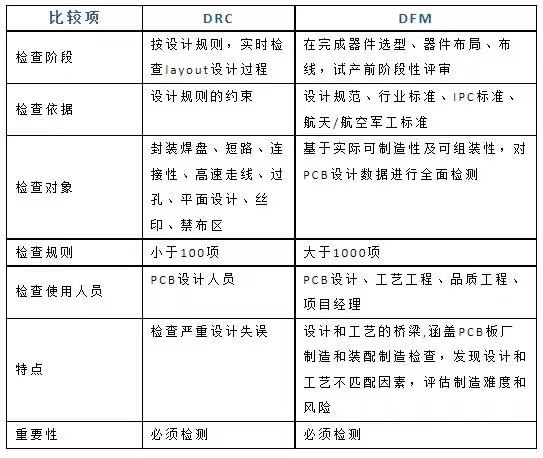

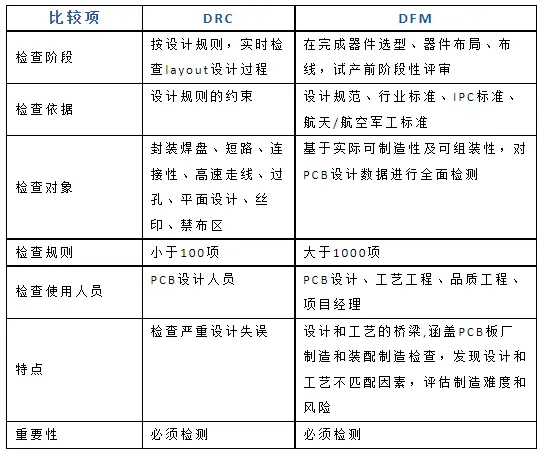

詳細解析DRC和DFM的區(qū)別

2022-09-14 14:56:17 1065

1065

一個完整的硬件產(chǎn)品,從設(shè)計到生產(chǎn),需要歷經(jīng)多個環(huán)節(jié)檢驗,不止在PCB layout中,要用DRC檢查設(shè)計的基本錯誤,還需用DFM檢查PCB生產(chǎn)的工藝隱患,并且在SMT生產(chǎn)時,其實還有很多

2022-11-22 16:00:32 878

878

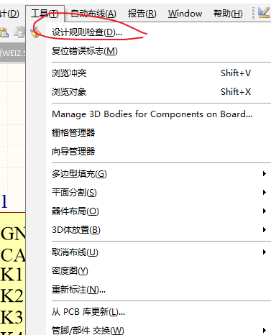

性能之外,還需要考慮可制造性(DFM)和可裝配性(DFA)方面的因素。 一、DRC檢查 許多新進的PCB工程師,一般都會使用DRC檢查。DRC檢查也叫設(shè)計規(guī)則檢查,通過Checklist和Report等檢查手段,重點規(guī)避開路、短路類的重大設(shè)計缺陷,檢查的同時遵循PCB設(shè)計質(zhì)量控制流程與方法。

2022-12-01 16:59:08 2769

2769

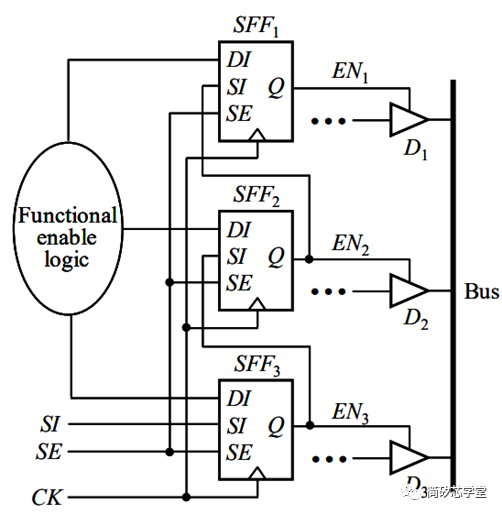

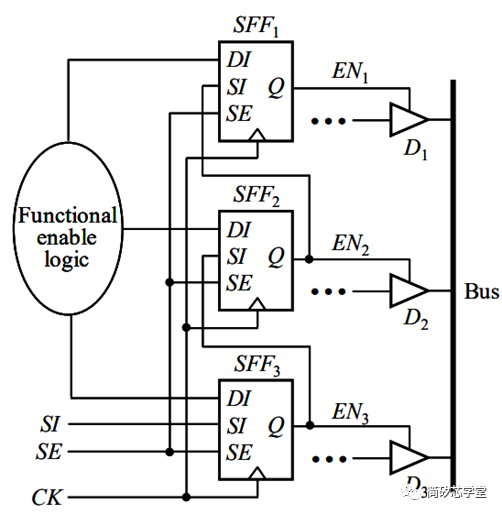

在進行DFT Logic的設(shè)計和插入之前,DFT工程師會先使用EDA工具對原Design執(zhí)行DRC(Design Rule Checking),即設(shè)計規(guī)則檢查。

2023-09-15 14:32:17 934

934

DRC檢查是依據(jù)自行設(shè)置的規(guī)則進行的。例如自己設(shè)置的最小間距是8mil,那么實際PCB中,出現(xiàn)小于6mil的間距就會報錯。并不是DRC有錯誤的板子就不能使用,例如絲印的錯誤不會影響電氣屬性。接下來簡單分析幾種常見的錯誤。

2019-07-04 09:10:19

剛連完線,DRC檢查報錯如下其他的不打算花時間改了,第一項的Net Antennae是什么意思,具體報錯如下PCB部分截圖如下上圖是這次畫圖,報錯,下圖是前一段時間畫的圖DRC此處沒有報錯,沒發(fā)現(xiàn)有什么問題是否有壇友知道如何解決此問題,或此問題是否有什么影響,謝謝~~~~~

2019-04-08 09:35:49

PCB設(shè)置DRC規(guī)則檢查是沒有出現(xiàn)連線錯誤,還有新連線沒有代替舊連線?不想直接推擠方式進行,只想直接忽略

2019-03-22 05:34:19

布線設(shè)計完成后,需認真檢查布線設(shè)計是否符合設(shè)計者所制定的規(guī)則,同時也需確認所制定的規(guī)則是否符合印制板生產(chǎn)工藝的需求,一般檢查有如下幾個方面:線與線,線與元件焊盤,線與貫通孔,元件焊盤與貫通孔,貫通

2016-08-26 12:33:51

在制造行業(yè),工藝設(shè)計師設(shè)計完PCB后,是否需要對設(shè)計成果進行檢驗?回答是肯定的,而且檢驗方式不止一種。第一種是DRC檢驗。DRC檢查也叫設(shè)計規(guī)則檢查,是PCB設(shè)計軟件(EDA)中用于在PCB

2018-03-12 10:09:25

0.1英寸(2.54 mm)或小于0.1英寸的整倍數(shù),如:0.05英寸、0.025英寸、0.02英寸等。6 設(shè)計規(guī)則檢查(DRC) 布線設(shè)計完成后,需認真檢查布線設(shè)計是否符合設(shè)計者所制定的規(guī)則,同時

2018-08-29 16:28:53

PCB板布線設(shè)計完成后,需認真檢查布線設(shè)計是否符合設(shè)計者所制定的規(guī)則,同時也需確認所制定的規(guī)則是否符合PCB板生產(chǎn)工藝的需求,一般檢查有如下幾個方面: (1)線與線,線與元件焊盤,線與貫通孔,元件

2016-11-27 22:04:50

本帖最后由 gk320830 于 2015-3-7 13:19 編輯

PCB設(shè)計規(guī)則檢查器編寫技巧本文簡單闡述一種編寫pcb設(shè)計規(guī)則檢查器(DRC)系統(tǒng)方法。利用電路圖生成工具得到PCB設(shè)計后

2013-10-16 11:36:12

本帖最后由 gk320830 于 2015-3-7 14:14 編輯

PCB設(shè)計規(guī)則檢查器編寫技巧本文簡單闡述一種編寫pcb設(shè)計規(guī)則檢查器(DRC)系統(tǒng)方法。利用電路圖生成工具得到PCB設(shè)計后

2013-10-08 11:24:40

本文簡單闡述一種編寫pcb設(shè)計規(guī)則檢查器(DRC)系統(tǒng)方法。利用電路圖生成工具得到PCB設(shè)計后,即可運行DRC以找到任何違反PCB設(shè)計規(guī)則故障。這些操作必須在后續(xù)處理開始之前完成,而且開發(fā)

2018-09-14 16:27:19

to Soldermask space 4mil 所有添數(shù)字默認,其他選項全部勾選。2. 打開規(guī)則驅(qū)動管理器,同時打開同網(wǎng)絡(luò)的DRC。3.完成上面幾步后,進行Databasecheck

2017-10-26 15:00:09

:icpojie】布線設(shè)計完成后,需認真檢查布線設(shè)計是否符合設(shè)計者所制定的規(guī)則,同時也需確認所制定的規(guī)則是否符合印制板生產(chǎn)工藝的需求,一般檢查有如下幾個方面:(1)線與線,線與元件焊盤,線與貫通孔,元件焊盤

2017-06-03 16:55:26

請教大家一下,我用的AD版本是17.0.6,在PCB布線中走圖中那種直角的丁字線,然后在DRC檢查的時候出現(xiàn)Un-Routed Net Constraint: Pad J107-11

2020-07-03 18:51:53

我剛對PCB進行DRC檢查錯了下面兩個錯誤,請問高手們這是怎么回事?

2013-05-14 16:11:21

我用的AD16,為什么在DRC檢查時,檢查了一次之后顯示沒有錯誤,線全部連上,但是關(guān)掉重啟AD再檢查一次出現(xiàn)有地線沒有接上,這是啥情況?漢化AD是不是會出現(xiàn)一些莫名奇妙的問題

2017-09-28 09:50:44

ALLEGRO畫PCB板在約束線寬,線間距時出現(xiàn)STM32部分引腳DRC(PP)錯誤,關(guān)閉DRC PIN檢查,錯誤消失,求大神指導(dǎo),新人剛剛學(xué)習(xí)!!!

2018-08-14 16:57:36

大家好,ALTIUM DESIGNER09PCB里面進行DRC檢測時,哪幾項規(guī)則需要設(shè)置?

2013-05-23 23:01:13

在用Altium設(shè)計pcb時線段的連接沒有連接到中心,看起來是連上的,實際他并沒有連接上(就連drc檢查都有時檢查不出來),這樣就容易出現(xiàn)虛焊,對自己造成損失。所以,在畫完板后,對PCB進行開斷路

2019-09-02 14:03:14

在設(shè)計PCB的時候,為了滿足各項設(shè)計要求的原因,我們需要設(shè)置很多的約束規(guī)則,然后設(shè)計完成之后,去進行DRC檢查。DRC檢查就是檢查我們的PCB設(shè)計是否滿足所設(shè)置的規(guī)則,常見的DRC檢查有開路,短路

2019-11-29 15:02:45

使用AD進行PCB——DRC檢查時,報告未生成,軟件提示...report_drc.xsl don't exist。出現(xiàn)此種報錯的原因大致的有以下兩種:1. report_drc.xsl文件的缺失

2019-11-12 10:14:34

HyperLynx? DRC 是一款強大、快速的免費電氣設(shè)計規(guī)則檢查工具,既可 讓驗證流程自動進行,又能節(jié)省手動檢查的時間。HyperLynx DRC 提供 多種配置,可以對不易仿真的復(fù)雜設(shè)計規(guī)則進行驗證,例如用于跨越 平面分割的走線和 EMI/EMC 的規(guī)則。

2019-10-08 07:45:43

大神們,我新下載的candence17.4,對原理圖DRC檢查后,就不能進行第二次檢查了,求教?

2022-09-21 10:34:33

各位大神,我新下載的candence17.4,對原理圖DRC檢查后,就不能進行第二次檢查了,求教?

2022-09-21 10:31:18

的Pin numbers; 3:check missing/illegal PCB footprint property——檢查缺失或者不符合規(guī)則的PCB封裝庫定義。沒有此項規(guī)則導(dǎo)入原理圖導(dǎo)入PCB

2020-09-03 17:20:27

AD進行行PCB DRC檢查時,軟件提示...report_drc.xsl不存在有誰懂么,跪求大神解答

2019-09-27 05:36:06

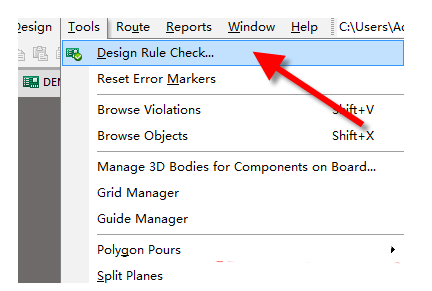

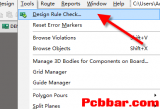

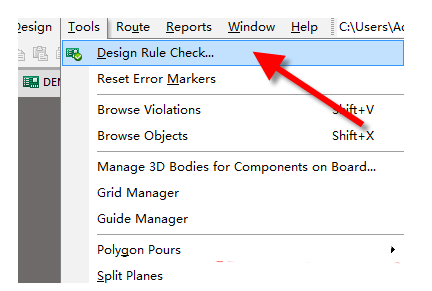

信息中,N16615100 等幾個單根浮空的網(wǎng)絡(luò)信息已經(jīng)自動消失了,說明該部分的警告信息已經(jīng)解決。(9)接下來看看DRC的規(guī)則設(shè)置和檢查方法。點擊圖標或者執(zhí)行PCB Design rulescheck

2020-07-06 15:09:36

一般的圓形的 或者不規(guī)則的PCB如何進行拼版輸出需要郵票空還是有其他的姿勢

2019-09-10 05:36:18

AD中如何在pcb中設(shè)置一個器件或區(qū)域不用DRC規(guī)則檢查?

2019-09-17 00:56:01

請問大神怎樣去編寫屬于自己的PCB設(shè)計規(guī)則檢查器?

2021-04-26 06:32:11

我用的是AD13,BGA封裝器件扇出后無網(wǎng)絡(luò)的焊盤自然也會扇出到一個過孔,可最后進行DRC檢查時這些扇出的無網(wǎng)絡(luò)焊盤就會報短路,請問要怎么解決?這是正常現(xiàn)象還是規(guī)則哪里沒設(shè)置對,最后沒辦法只好在規(guī)則里將短路的規(guī)則中設(shè)置所有no net的網(wǎng)絡(luò)都可以短路,不知道這么做對不,請高手指點

2014-11-12 10:40:14

HyperLynx? DRC PE 是一款強大、快速的電氣設(shè)計規(guī)則檢查工具,既可讓 驗證流程自動進行,又能使您以迭代方式執(zhí)行設(shè)計檢查。HyperLynx DRC PE 可執(zhí)行不易進行仿真的復(fù)雜檢查

2019-10-08 08:18:27

本帖最后由 gk320830 于 2015-3-7 11:59 編輯

編寫PCB設(shè)計規(guī)則檢查器技巧本文闡述了一種編寫pcb設(shè)計規(guī)則檢查器(DRC)系統(tǒng)方法。利用電路圖生成工具得到PCB設(shè)計后

2013-10-29 11:28:30

本文闡述了一種編寫pcb設(shè)計規(guī)則檢查器(DRC)系統(tǒng)方法。利用電路圖生成工具得到PCB設(shè)計后,即可運行DRC以找到任何違反設(shè)計規(guī)則故障。這些操作必須在后續(xù)處理開始之前完成,而且開發(fā)電路圖生成工具

2018-09-10 16:28:09

如題:在線DRC如何打開已經(jīng)設(shè)置了在線DRC,但是不會實時報錯,顯示綠色,在手動運行規(guī)則檢查后沖突的地方會變綠,修改后,還是綠色,只有再次手動運行規(guī)則檢查后綠色才會消失。請問這是哪里設(shè)置有問題?

2019-02-27 11:06:08

PCB如何進行分區(qū)布線? 設(shè)計分區(qū)可以分解為物理分區(qū)和電氣分區(qū)。物理分區(qū)主要涉及元器件布局、朝向和屏蔽等問題;電氣分區(qū)

2009-03-25 11:54:49 2263

2263 編寫PCB設(shè)計規(guī)則檢查器技巧

本文闡述了一種編寫PCB設(shè)計規(guī)則檢查器(DRC)系統(tǒng)方法。利用電路圖生成工具得到PCB設(shè)計后,即可運

2009-11-17 14:03:10 1019

1019 編寫屬于自己的PCB設(shè)計規(guī)則檢查器

編寫屬于自己的PCB設(shè)計規(guī)則檢查器具有很多優(yōu)點,盡管設(shè)計檢查器并不那么簡單,但也并非高不可攀,因為任何熟悉現(xiàn)有編程或腳本

2009-12-27 13:31:01 811

811

AD9上PCB布線規(guī)則檢查合理設(shè)置好,可以幫助我們提高布線效率以及輔助我們檢查相應(yīng)錯誤

2015-10-29 16:22:50 0

0 版圖中DRC設(shè)計規(guī)則檢查,詳細步驟和方法,有圖說明

2016-06-08 16:28:14 7

7 Altium-Designer-6-DRC規(guī)則檢查的英漢對照表,很不錯的資料,感興趣的可以看看。

2016-09-19 16:57:48 0

0 AltiumDesigner的DRC規(guī)則參考,很實用的資料,感興趣的可以看看。

2016-09-19 16:57:48 0

0 Altium-Designer-6-DRC規(guī)則檢查的英漢對照表

2016-11-02 19:07:33 0

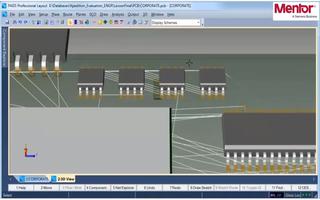

0 Mentor軟件的DRC檢查 接線率 未拿出器件

2016-12-17 10:06:54 0

0 AD規(guī)則檢查一鍵搞定

2017-06-26 16:41:27 0

0 PCB元器件布局檢查規(guī)則

2017-12-22 13:51:50 0

0 Altium有時候總是顯示DRC錯誤,不知道哪里出了問題,下面小編帶大家學(xué)習(xí)一下常見的DRC檢查有哪些?

2018-09-23 12:27:00 32674

32674 PADS? HyperLynx? DRC 提供功能強大的定制 PCB 設(shè)計電氣規(guī)則檢查器。不同于走線間距和線板邊緣邊界等傳統(tǒng) PCB 檢查,PADS HyperLynx DRC 包括一套完整的規(guī)則集,可用來識別出經(jīng)常導(dǎo)致 EMI 或 SI 問題的 Layout 疏漏。

2019-05-21 06:08:00 5935

5935 此點播網(wǎng)絡(luò)研討會將介紹如何使用電氣設(shè)計規(guī)則檢查 (DRC) 發(fā)現(xiàn)潛在的電磁干擾 (EMI) 問題。

2019-05-17 06:32:00 4368

4368

此點播網(wǎng)絡(luò)研討會將介紹如何使用電氣設(shè)計規(guī)則檢查 (DRC) 發(fā)現(xiàn)潛在的電磁干擾 (EMI) 問題。

2019-05-14 06:18:00 3535

3535

前期為了滿足各項設(shè)計的要求,我們會設(shè)置很多約束規(guī)則,當一個PCB單板設(shè)計完成之后,通常要進行DRC檢查。那么DRC檢查到底有哪些具體事項?

2019-05-29 14:43:31 20009

20009

每個人都知道規(guī)則是為了我們的保護。但有時候,無論是偶然還是故意,規(guī)則都會被繞過。電路板設(shè)計也有規(guī)則需要遵循。幸運的是,現(xiàn)代PCB設(shè)計軟??件正在與設(shè)計規(guī)則檢查例程或DRC合作。現(xiàn)在,我們作為設(shè)計師只需要使用它們。

2019-07-25 14:43:52 2669

2669 今天的布局工具繼續(xù)將越來越多的這些規(guī)則添加到他們的檢查程序中。通常,所有這些規(guī)則都在一個設(shè)計規(guī)則菜單中提供,并為了方便起見分為不同的類別。使用PCB布局工具中提供的所有設(shè)計規(guī)則檢查是確保創(chuàng)建無錯

2019-07-26 11:54:15 6839

6839 在用Altium設(shè)計pcb時線段的連接沒有連接到中心,看起來是連上的,實際他并沒有連接上(就連drc檢查都有時檢查不出來),這樣就容易出現(xiàn)虛焊,對自己造成損失。所以,在畫完板后,對PCB進行開斷路的檢查是非常必要的。

2019-07-28 11:58:58 8005

8005 PCB板布線設(shè)計完成后,需認真檢查布線設(shè)計是否符合設(shè)計者所制定的規(guī)則,同時也需確認所制定的規(guī)則是否符合PCB板生產(chǎn)工藝的需求。

2019-08-12 12:35:05 2957

2957 在原理圖工具中捕獲PCB設(shè)計后,必須運行DRC以查找違反設(shè)計規(guī)則的行為。

2019-08-14 18:01:00 2175

2175 layout完成后,需要對PCB進行規(guī)則檢查,選擇Tools--Quick Reports,依次檢查 shape Dynamic state,Unconnect Pins Report,Design ruler Check(DRC) Report。

2019-08-21 08:40:17 10349

10349 定制化設(shè)計工具包含多種內(nèi)建DRC工具,輔助版圖工程師放上多邊形。在這些“工具內(nèi)”DRC檢查程序里最著名的是Cadence的DIVA工具,但所有的定制化工具都具備相似的功能,比如SpringSoft的Laker工具有“基于規(guī)則的設(shè)計”,Synopsys的Custom Designer有Smart DRD.

2019-09-19 14:29:00 1814

1814 剛果民主共和國墊?HyperLynx?提供了一個可定制的和強大的PCB設(shè)計電氣規(guī)則檢查。代替?zhèn)鹘y(tǒng)的PCB檢查如道間間距和trace-to-board邊緣邊界,墊HyperLynx剛果(金)包括一個全面的規(guī)則集,確定布局經(jīng)常引起電磁干擾或SI的疏忽的問題。

2019-11-06 07:08:00 3675

3675 覆蓋默認設(shè)計約束PCB上的特定模型通過定義3 d許可和使用設(shè)計規(guī)則檢查來驗證它們。

2019-10-28 07:10:00 1544

1544 這種按需網(wǎng)絡(luò)研討會將介紹如何使用電氣設(shè)計規(guī)則檢查(DRC)找到潛在的電磁干擾(EMI)問題。

2019-10-28 07:03:00 2918

2918 Create Report File 執(zhí)行完DRC之后,Altium會創(chuàng)建一個關(guān)于規(guī)則檢查的報告,對報錯信息會給出詳細的描述并會給出報錯的位置信息,方便我們設(shè)計者對報錯信息進行解讀。

2020-10-06 17:49:00 7106

7106

上管理數(shù)千個組件和連接時,肯定會發(fā)生錯誤。 幸運的是,您可以在 PCB 設(shè)計過程的早期階段做一些非常簡單的事情,以確保在將設(shè)計發(fā)送到制造廠之前的可制造性:執(zhí)行設(shè)計規(guī)則檢查( DRC )。 接下來是 DRC 的速成課程,以及它如何幫助您提高可接受的制

2020-09-17 22:02:39 3288

3288 在PCB布線設(shè)計完成后,需要檢查PCB布線設(shè)計有沒有符合規(guī)則,并且還有檢查制定的規(guī)則符不符合PCB生產(chǎn)工藝的要求,那么pcb布線后怎么檢查呢,下面一起來看看pcb布線檢查方法。 一般PCB布線后需要

2021-08-17 16:45:00 26850

26850 基于Cadence軟件DRACULA工具的DRC檢查(ups電源技術(shù)維修)-該文檔為基于Cadence軟件DRACULA工具的DRC檢查講解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 15:25:26 27

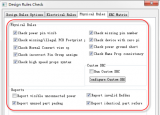

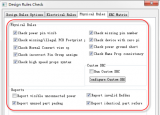

27 orcad的電氣規(guī)則檢查的每一個的含義是什么? 答:orcad進行電氣DRC檢測時,如圖3-64所示,需要對檢查的每一項參數(shù)進行設(shè)置,每個參數(shù)的含義如下所示: 圖3-64 電氣規(guī)則檢查參數(shù)設(shè)置示意圖

2021-10-29 11:07:32 3305

3305

orcad原理圖文件怎么進行DRC的檢測? 答:第一步,選擇原理圖的根目錄,然后執(zhí)行菜單Tools-Design Rules Check,進行設(shè)計規(guī)則的檢查,如圖3-61所示; 圖3-61 進行

2021-11-02 10:40:35 6796

6796

orcad的物理規(guī)則檢查的每一個的含義是什么? 答:orcad進行物理DRC檢測時,如圖3-65所示,需要對檢查的每一項參數(shù)進行設(shè)置,每個參數(shù)的含義如下所示: 圖3-65 物理規(guī)則檢查參數(shù)設(shè)置示意圖

2021-11-09 11:25:31 3277

3277

最近硬件工程師同行提出疑問,在硬件設(shè)計過程中l(wèi)ayout完成后有DRC檢查,已經(jīng)對設(shè)計工藝規(guī)則做了檢查,那么DFM可制造性分析還有必要嗎?今天就為大家用一篇文章說明下DRC與DFM兩者的區(qū)別

2022-11-03 13:28:58 472

472 。 ? DRC和DFM檢查原則比較 ? 01?DRC檢測項 (以Altium Designer為例) DRC檢查 也叫設(shè)計規(guī)則檢查,是PCB設(shè)計軟件(EDA)中用于在PCB Layout過程中實時檢查和發(fā)現(xiàn)

2022-11-17 08:20:06 2745

2745 一個完整的硬件產(chǎn)品,從設(shè)計到生產(chǎn),需要歷經(jīng)多個環(huán)節(jié)檢驗,不止在PCB layout中,要用 DRC檢查 設(shè)計的基本錯誤,還需用 DFM檢查 PCB生產(chǎn)的工藝隱患,并且在SMT生產(chǎn)時,其實還有很多

2022-11-17 08:30:06 416

416 性能之外,還需要考慮可制造性(DFM)和可裝配性(DFA)方面的因素。 ? DRC檢查 許多新進的PCB工程師,一般都會使用 DRC檢查。 DRC檢查也叫設(shè)計規(guī)則檢查,通過Checklist和Report等檢查手段,重點規(guī)避開路、短路類的重大設(shè)計缺陷,檢查的同時遵循PCB設(shè)計質(zhì)量控制流程與方法。

2022-11-24 08:15:03 1451

1451 一個完整的硬件產(chǎn)品,從設(shè)計到生產(chǎn),需要歷經(jīng)多個環(huán)節(jié)檢驗,不止在PCB layout中,要用 DRC檢查 設(shè)計的基本錯誤,還需用 DFM檢查 PCB生產(chǎn)的工藝隱患,并且在SMT生產(chǎn)時,其實還有很多

2022-12-06 08:20:10 529

529 一個完整的硬件產(chǎn)品,從設(shè)計到生產(chǎn),需要歷經(jīng)多個環(huán)節(jié)檢驗,不止在PCB layout中,要用 DRC檢查 設(shè)計的基本錯誤,還需用 DFM檢查 PCB生產(chǎn)的工藝隱患,并且在SMT生產(chǎn)時,其實還有很多

2022-12-13 08:15:07 332

332 前期為了滿足各項設(shè)計的要求,通常會設(shè)置很多約束規(guī)則,當一個PCB設(shè)計完成之后,通常要進行DRC。DRC就是檢查設(shè)計是否滿足所設(shè)置的規(guī)則。一個完整的PCB設(shè)計必須經(jīng)過各項連接性規(guī)則檢查,常見的檢查包括

2023-04-04 07:40:02 1243

1243 為了盡量減小單板設(shè)計的串擾問題,PCB設(shè)計完成之后一般要對線間距3W規(guī)則進行一次規(guī)則檢查。

2023-05-30 09:04:33 2364

2364

一個完整的硬件產(chǎn)品,從設(shè)計到生產(chǎn),需要歷經(jīng)多個環(huán)節(jié)檢驗,不止在PCBlayout中,要用DRC檢查設(shè)計的基本錯誤,還需用DFM檢查PCB生產(chǎn)的工藝隱患,并且在SMT生產(chǎn)時,其實還有很多“坑”,是無法

2022-11-18 10:08:39 363

363

由于DRC必須遍歷 PCB設(shè)計整個電路圖,包括每個符號、每個引腳、每個網(wǎng)路、每種屬性,如有必要還能創(chuàng)建數(shù)目不限“附屬”文件。如4.0節(jié)所述,DRC可以標示出任何違反設(shè)計規(guī)則細微偏差。

2023-10-13 14:58:18 211

211 由于DRC必須遍歷 PCB設(shè)計整個電路圖,包括每個符號、每個引腳、每個網(wǎng)路、每種屬性,如有必要還能創(chuàng)建數(shù)目不限“附屬”文件。如4.0節(jié)所述,DRC可以標示出任何違反PCB設(shè)計規(guī)則細微偏差。例如

2023-10-31 15:06:37 159

159 對于Altium Designer來說,在所有的布局,布線,鋪銅都完成之后,也就完成了初步的設(shè)計工作,接下來就是進行電氣規(guī)則的檢查了。 什么是電氣規(guī)則的檢查呢? 電氣規(guī)則檢查包括很多內(nèi)容,比如說絲印

2023-11-06 15:17:35 912

912

DRC規(guī)則是工程師根據(jù)審生產(chǎn)制造標準設(shè)定的一些約束,PCB設(shè)計工程師都需要遵守這些規(guī)則,這樣可以確保設(shè)計出來的產(chǎn)品功能正常、可靠、并且可以到達量產(chǎn)生產(chǎn)的標準。

2023-11-17 10:05:43 1463

1463

DRC的全稱為design rule check,也就是設(shè)計規(guī)則檢查。廣義上DRC會包含很多分類,只要是設(shè)計規(guī)則廣義上都可以成為DRC。

2023-12-04 13:55:16 682

682

電子發(fā)燒友App

電子發(fā)燒友App

評論