1 引言

二十世紀(jì)后半期,隨著集成電路和計(jì)算機(jī)的不斷發(fā)展,電子技術(shù)面臨著嚴(yán)峻的挑戰(zhàn)。由于電子技術(shù)發(fā)展周期不斷縮短,專用集成電路ASIC的設(shè)計(jì)面臨著難度不斷提高與設(shè)計(jì)周期不斷縮短的矛盾,為了解決這個(gè)問題,要求我們必須采用新的設(shè)計(jì)方法和使用高層次的設(shè)計(jì)工具,在此情況下,EDA(Electronic Design Automation)即電子設(shè)計(jì)自動(dòng)化技術(shù)應(yīng)運(yùn)而生。

隨著電子技術(shù)的發(fā)展及縮短電子系統(tǒng)設(shè)計(jì)周期的要求,EDA技術(shù)得到了迅猛發(fā)展。

EDA技術(shù)是以大規(guī)模可編程邏輯器件為設(shè)計(jì)載體,以硬件描述語言為系統(tǒng)邏輯描述的主要表達(dá)方式,以計(jì)算機(jī)、大規(guī)模可編程邏輯器件的開發(fā)軟件及實(shí)驗(yàn)開發(fā)系統(tǒng)為設(shè)計(jì)工具,通過有關(guān)的開發(fā)軟件,自動(dòng)完成用軟件的方法設(shè)計(jì)電子系統(tǒng)到硬件系統(tǒng)的邏輯編譯、邏輯化簡、邏輯分割、邏輯綜合及優(yōu)化、邏輯布局布線、邏輯仿真,直至對于特定目標(biāo)芯片的適配編譯、邏輯影射、編程下載等工作,最終形成集成電子系統(tǒng)或?qū)S眉尚酒囊婚T新技術(shù)。

EDA技術(shù)伴隨著計(jì)算機(jī)、集成電路、電子系統(tǒng)設(shè)計(jì)的發(fā)展,經(jīng)歷了三個(gè)發(fā)展階段,即:20世紀(jì)70年代發(fā)展起來的CAD技術(shù);20世紀(jì)80年代開始應(yīng)用的CAE技術(shù);20世紀(jì)90年代后期,出現(xiàn)的以硬件描述語言、系統(tǒng)級仿真和綜合技術(shù)為特征的EDA技術(shù),這時(shí)的EDA工具不僅具有電子系統(tǒng)設(shè)計(jì)的能力,而且能提供獨(dú)立于工藝和廠家的系統(tǒng)級設(shè)計(jì)能力,具有高級抽象的設(shè)計(jì)構(gòu)思手段。

EDA技術(shù)涉及面廣,內(nèi)容豐富,從教學(xué)和實(shí)用的角度看,主要有以下四個(gè)方面內(nèi)容:(1)大規(guī)模可編程邏輯器件;(2)硬件描述語言;(3)軟件開發(fā)工具;(4)實(shí)驗(yàn)開發(fā)系統(tǒng)。其中,大規(guī)模可編程邏輯器件是利用EDA技術(shù)進(jìn)行電子系統(tǒng)設(shè)計(jì)的載體;硬件描述語言是利用EDA技術(shù)進(jìn)行電子系統(tǒng)設(shè)計(jì)的主要表達(dá)手段;軟件開發(fā)工具是利用EDA技術(shù)進(jìn)行電子系統(tǒng)設(shè)計(jì)的智能化、自動(dòng)化設(shè)計(jì)工具;實(shí)驗(yàn)開發(fā)系統(tǒng)是利用EDA技術(shù)進(jìn)行電子系統(tǒng)設(shè)計(jì)的下載工具及硬件驗(yàn)證工具。

隨著現(xiàn)代半導(dǎo)體的精密加工技術(shù)發(fā)展到深亞微米(0.18~0.35um)階段,基于大規(guī)模或超大規(guī)模集成電路技術(shù)的定制或半定制ASIC(Application Specific Integrated Circuit專用集成電路)器件大量涌現(xiàn)并獲得廣泛的應(yīng)用,使整個(gè)電子技術(shù)與產(chǎn)品的面貌發(fā)生了深刻的變化極大地推動(dòng)了社會(huì)信息化的發(fā)展進(jìn)程。而支撐這一發(fā)展進(jìn)程的主要基礎(chǔ)之一,就是EDA技術(shù)。

EDA技術(shù)在硬件方面融合了大集成電路制造技術(shù),ic圖設(shè)計(jì)技術(shù)、ASIC測試和封裝技術(shù)、CPLD/FPGA技術(shù)等;在計(jì)算機(jī)輔助工程方面融合了計(jì)算機(jī)輔助設(shè)計(jì)CAD計(jì)算機(jī)輔助制造CAM計(jì)算機(jī)輔助測試CAT技術(shù)及多種計(jì)算機(jī)語言的設(shè)計(jì)概念;而在現(xiàn)代電子學(xué)方面則容納了更多的內(nèi)容,如數(shù)字系統(tǒng)設(shè)計(jì)理論、數(shù)字信號處理技術(shù)、系統(tǒng)建模和優(yōu)化技術(shù)等。

2 可編程邏輯器件(PLD Programmable Logic Device)

可編程邏輯器件是近幾年才發(fā)展起來的一種新型集成電路,是當(dāng)前數(shù)字系統(tǒng)設(shè)計(jì)的主要硬件基礎(chǔ),是硬件編程語言HLD物理實(shí)現(xiàn)工具,可編程邏輯器件對數(shù)字系統(tǒng)設(shè)計(jì)自動(dòng)化起著推波助瀾的作用,可以說,沒有可編程邏輯器件就沒有當(dāng)前的數(shù)字電路自動(dòng)化,目前,由于這種以可編程邏輯器件為原材料,從“制造自主芯片”開始的EDA設(shè)計(jì)模式己成為當(dāng)前數(shù)字系統(tǒng)設(shè)計(jì)的主流,若要追趕世界最先進(jìn)的數(shù)字系統(tǒng)設(shè)計(jì)方法,就要認(rèn)識并使用可編程邏輯器件。

數(shù)字集成電路本身在不斷地進(jìn)行更新?lián)Q代。它由早期的電子管、晶體管、小中規(guī)模集成電路、發(fā)展到超大規(guī)模集成電路(VLSIC幾萬門以上)以及許多具有特定功能的專用集成電路。但是,隨著微電子技術(shù)的發(fā)展,設(shè)計(jì)與制造集成電路的任務(wù)己不完全由半導(dǎo)體廠商來獨(dú)立承擔(dān)。系統(tǒng)設(shè)計(jì)師們更愿意自己設(shè)計(jì)專用集成電路(ASIC)芯片,而且希望ASIC的設(shè)計(jì)周期盡可能短,最好是在實(shí)驗(yàn)室里就能設(shè)計(jì)出合適的ASL芯片,并且立即投入實(shí)際應(yīng)用之中,因而出現(xiàn)了現(xiàn)場可編程邏輯器件(FPLD),其中應(yīng)用最廣泛的當(dāng)屬現(xiàn)場可編程門陣列(FPGA)復(fù)雜可編程邏輯器件(CPLD)。

可編程邏輯器件正處于高速發(fā)展的階段。新型的FPGA/CPLD規(guī)模越來越大,成本越來越低。高性價(jià)比使可編程邏輯器件在硬件設(shè)計(jì)領(lǐng)域扮演著日益重要的角色。

低端CPLD已經(jīng)逐步取代了74系列等傳統(tǒng)的數(shù)字元件,高端的FPGA也在不斷地奪取ASIC的市場份額,特別是目前大規(guī)模FPGA多數(shù)支持可編程片上系統(tǒng)SOPC與CPU或DSP Core的有機(jī)結(jié)合使FPGA已經(jīng)不僅僅是傳統(tǒng)的硬件電路設(shè)計(jì)手段,而逐步升華為系統(tǒng)級實(shí)現(xiàn)工具。

下一代可編程邏輯器件硬件上的四大發(fā)展趨勢可總結(jié)如下:最先進(jìn)的ASL生產(chǎn)工藝將被更廣泛的應(yīng)用于以FPGA為代表的可編程邏輯器件;越來越多的高端FPGA產(chǎn)品將包含DSP或CPU等處理器內(nèi)核,從而FPGA將由傳統(tǒng)的硬件設(shè)計(jì)手段逐步過渡為系統(tǒng)級設(shè)計(jì)平臺:FPGA包含功能越來越豐富的硬核(HardIPCore),與傳統(tǒng)ASIC進(jìn)一步融合,并通過結(jié)構(gòu)化ASIC技術(shù)加快占領(lǐng)部分ASIC市場;低成本FPGA的密度越來越高,價(jià)格越來起合理,將成為FPGA發(fā)展的中堅(jiān)力量。這4個(gè)發(fā)展趨勢可簡稱為先進(jìn)工藝、處理器內(nèi)核、硬核與結(jié)構(gòu)化ASIC低成本器件。

3 硬件描述語言HDL(Hardware Description Language)

HDI是電子系統(tǒng)硬件行為描述、結(jié)構(gòu)描述、數(shù)據(jù)流描述的語言。目前利用硬件描述語言可以進(jìn)行數(shù)字電子系統(tǒng)的設(shè)計(jì)。隨著研究的深入,利用硬件描述語言進(jìn)行模擬電子系統(tǒng)設(shè)計(jì)或混合電子系統(tǒng)設(shè)計(jì),也正在探索中。

硬件描述的語言種類很多,有的從PASCAI發(fā)展而來,也有一些從Cl吾言發(fā)展而來。有些HDL成為IEEE準(zhǔn),但大部分是本企業(yè)標(biāo)準(zhǔn)。HDl發(fā)展的技術(shù)源頭是:在HDl形成發(fā)展之前,已有了許多程序設(shè)計(jì)語言,如匯編、C、PASCAL、FORTRAN、PROLOG等。這些語言運(yùn)行在不同硬件平臺、不同的操作環(huán)境中,它們適合于描述過程和算法,不適合作硬件描述。CAD的出現(xiàn),使人們可以利用計(jì)算機(jī)進(jìn)行建筑、服裝等行業(yè)的輔助設(shè)計(jì),而電子輔助設(shè)計(jì)也同步發(fā)展起來。在利用EDA工具進(jìn)行電子設(shè)計(jì)時(shí),邏輯圖、分立電子元件作為整個(gè)越來越復(fù)雜的電子系統(tǒng)的設(shè)計(jì)己不適應(yīng)。任何一種EDA工具,都需要一種硬件描述語言來作為EDA工具的工作語言。這些眾多的EDA工具軟件開發(fā)者,各自推出了自己的HDL語言。在我國比較有影響的硬件描述語言有:ABEL-HDL語言、Verilog HDL語言、AHDL語言和VHDL語言。

3.1 ABEL-HDL語言

這是一種早期的硬件描述語言。在可編程邏輯器件的設(shè)計(jì)中,可方便準(zhǔn)確的描述所設(shè)計(jì)的電路邏輯功能。他支持邏輯電路的多種表達(dá)形式,其中包括邏輯方程,真值表和狀態(tài)圖。ABEL語言和Verilog語言同屬一種描述級別,但ABEL語言的特性受支持的程度遠(yuǎn)遠(yuǎn)不如Verilog,Verilog是從集成電路設(shè)計(jì)中發(fā)展而來,語言較為成熟,支持的EDA工具很多。而ABEL語言從早期可編程邏輯器件(PLD)的設(shè)計(jì)中發(fā)展而來。ABEL-HDI被廣泛用于各種可編程邏輯器件的邏輯功能設(shè)計(jì),由于其語描述的獨(dú)立性,因而適用于各種不同規(guī)模的可編程器的設(shè)計(jì)。如DOS版的ABEL3.0軟件可對包括GAL期間進(jìn)行全方位的邏輯描述和設(shè)計(jì),而在諸如Lattice的ISPEXPERT,DATAIO的Synario ,Vantis的Design-Direct,XiLinx的FOUNDATION和WEBPACK等EDA軟件中,ABEL-HDL同樣可用于較大規(guī)模的FPGA/CPLD器件功能設(shè)計(jì)。ABEL-HDI還能對所設(shè)計(jì)的邏輯系統(tǒng)進(jìn)行功能仿真。ABEL-HDL拘設(shè)計(jì)也能通過標(biāo)準(zhǔn)格式設(shè)計(jì)轉(zhuǎn)換文件,轉(zhuǎn)換成其他設(shè)計(jì)環(huán)境,如VHDI。Verilog-HDL等。從長遠(yuǎn)來看,VHDL口Verilog-HDL的運(yùn)用會(huì)比ABEL-HDL多的多,ABEL-HDL只會(huì)在較小的范圍內(nèi)繼續(xù)存在。

3.2 Verilog HDL

Verilog HDL就是在應(yīng)用最廣泛的C語言的基礎(chǔ)上發(fā)展起來的一種件描述語言,它是由GDA(Gateway Design Autom action)公司的PhiMooorby,在1983年末首創(chuàng)的,最初只設(shè)計(jì)了一個(gè)仿真與驗(yàn)證工具,之后又陸續(xù)開發(fā)了相關(guān)的故障模擬與時(shí)序分析工具。1985年Moorby,推出它的第三個(gè)商用仿真器Verilog-XL獲得了巨大的成功,從而使得Verilog HDL迅速得到推廣應(yīng)用。1989年CADENCE公司收購了GDA公司,使得Verilog HDL成為了該公司的獨(dú)家專利。1990年CAD斟CE公司公開發(fā)表了Verilog HDL并成立LVI織以促進(jìn)Verilog HDL成為IEEE標(biāo)準(zhǔn),即IEEE Srandard1364-1995。

Verilog HDL最大特點(diǎn)就是易學(xué)易用,如果有C語言的編程經(jīng)驗(yàn),可以在一個(gè)較短的時(shí)間內(nèi)很快的學(xué)習(xí)和掌握,因而可以把Verilog HDL內(nèi)容安排在與ASIC設(shè)計(jì)等相關(guān)課程內(nèi)部進(jìn)行講授,由于HDL語言本身是專門面向硬件與系統(tǒng)設(shè)計(jì)的,這樣的安排可以使學(xué)習(xí)者同時(shí)獲得設(shè)計(jì)實(shí)際電路的經(jīng)驗(yàn)。與之相比VHDL的學(xué)習(xí)要困難一些。但Verilog HDL較自由的語法,也容易造成初學(xué)者犯一些錯(cuò)誤,這一點(diǎn)要特別注意。

3.3 AHDL

Altera硬件描述語言AHDL(Altera Hardware Description Language)是一種模塊化的高級語言,是ALTERA公司發(fā)明的HDL,特點(diǎn)是非常易學(xué)易用,學(xué)過高級語言的人可以在很短的時(shí)間(如幾周)內(nèi)掌握AHDL。

AHDL語言完全集成于MAX+plusII/QuartusII系統(tǒng)之中,特別適于描述復(fù)雜的組合邏輯、組(Group)運(yùn)算、狀態(tài)機(jī)、真值表和參數(shù)化邏輯。設(shè)計(jì)者可以通過MAX+plusII或QuartusII的軟件系統(tǒng)對AHDL源程序進(jìn)行編輯,并通過對源程序的編譯建立仿真、時(shí)域分析和器件編程的輸出文件。

AHDL的語句和元素種類齊全、功能強(qiáng)大,而且易于使用。設(shè)計(jì)者可以使用AHDL直完整層次的工程(Project設(shè)計(jì)文件,或者在一個(gè)層次的設(shè)計(jì)中混合其他類型的設(shè)計(jì)文件,如Verilog HDLVHDL設(shè)計(jì)文件。AHDL文件作為一種文本文件,它既可以用EDA提供的文本文件編輯器來建立文本(TDF AHDL Text Design File)也可以用其它文本編輯器建立文本文件,但是,由于AHDL與MAX+PlusⅡ/QuartusⅡ間的持殊關(guān)系,建議最好使用前者,設(shè)計(jì)者可以方便地應(yīng)用MAX+PlusⅡ/QuartusⅡ?qū)HDL進(jìn)行文本編輯、編譯、調(diào)試等工作,尤其是在消息處理器中對錯(cuò)誤自動(dòng)定位的功能使調(diào)試十分方便。它的缺點(diǎn)是移植性不好,通常只用于ALTERA公司自己的開發(fā)系統(tǒng)。

? ? ? ?3.4 VHDL語言

VHDL語言(Very-High-Speed Integrated Circuit Hardware Description Language)即超高速集成電路硬件描述語言,美國國防部在20世紀(jì)80年代后期開發(fā)了VHDL語言。1981年6月成立的VHDL工作小組,提出了一個(gè)滿足電子設(shè)計(jì)各種要求的能夠作為工業(yè)標(biāo)準(zhǔn)的HDL,1983年第三季度,由JBM公司、TJ公司、Internetrics公司簽約,組成開發(fā)小組,工作任務(wù)是提出語言版本和開發(fā)軟件環(huán)境。1986年IEEE標(biāo)準(zhǔn)化組織開始工作,討論VHDL語言標(biāo)準(zhǔn),歷時(shí)一年有余,1987年12月通過標(biāo)準(zhǔn)審查,并宣布實(shí)施,即IEEE STD 1076-1987[IRM87]。1993年VHDL重新修訂,形成新的標(biāo)準(zhǔn)即IEEE STD 1076-1993[IRM93]。

該語言設(shè)計(jì)技術(shù)齊全、方法靈活、可與制作工藝無關(guān)、編程易于共享,所以成為硬件描述語言的主流,成為標(biāo)準(zhǔn)硬件描述語言。將VHDL程序?qū)懭肟删幊绦酒校龀葾SIC芯片,因其開發(fā)周期短,更方便,所以將在很大范圍內(nèi)取代單片控制電路,成為未來數(shù)字電路設(shè)計(jì)的主旋律。由于半導(dǎo)體編程技術(shù)的快速進(jìn)步,VHDL所能提供的高階電路描述語言方式,使復(fù)雜的電路可以通過VHDL編輯器的電路方式,輕易而且快速地達(dá)到設(shè)計(jì)的規(guī)格。VHDL電路描述語言所能涵蓋的范圍相當(dāng)廣,能適用于各種不同階層的設(shè)計(jì)工程師的需求。從ASIC的設(shè)計(jì)到PCB系統(tǒng)的設(shè)計(jì),VHDL電路描述語言都能派上用場,所以VHDL電路設(shè)計(jì)毫無疑問地成為硬件設(shè)計(jì)工程師的必備工具。目前,VHDL語言也己成為FPGA/CPLD編程最常用的工具。

VHDL作力EDA的重要組成都分,提供了借助計(jì)算機(jī)進(jìn)行數(shù)字系統(tǒng)設(shè)計(jì)的一種很好的手段。用VHDL進(jìn)行設(shè)計(jì)有許多優(yōu)點(diǎn),VHDL的硬件描述能力很強(qiáng),可以用于從門級、電路級直至系統(tǒng)級的描述、仿真、綜合和調(diào)試。利用VHDL豐富的仿真語句和庫函數(shù),對大系統(tǒng)的早期設(shè)計(jì),可在遠(yuǎn)離門級的高層次上進(jìn)行模擬,以利于設(shè)計(jì)者確定整個(gè)設(shè)計(jì)結(jié)構(gòu)和功能的可行性。VHDL強(qiáng)大的行為描述能力和程序結(jié)構(gòu)使其具有支持對大規(guī)模設(shè)計(jì)進(jìn)行分解,以及對已有的設(shè)計(jì)進(jìn)行再利用的功能。運(yùn)用VHDL設(shè)計(jì)系統(tǒng)硬件具有相對獨(dú)立性,設(shè)計(jì)時(shí)沒有嵌入與工藝有關(guān)的信息,對硬件的描述與具體的工藝技術(shù)和硬件結(jié)構(gòu)無關(guān)。當(dāng)門級或門級以上的描述通過仿真檢驗(yàn)以后,再用相應(yīng)的工具將設(shè)計(jì)映射成不同的工藝,這使硬件實(shí)現(xiàn)的目標(biāo)器件有很寬的選擇范圍,并且修改電路與修改工藝或選擇器件相互之間不會(huì)產(chǎn)生不良影響。VHDL標(biāo)準(zhǔn)規(guī)范,語法較為嚴(yán)格,采用VHDL的設(shè)計(jì)便于重復(fù)利用交流,VHDL所具有的類屬描述語句和子程序調(diào)用等功能使設(shè)計(jì)者對完成的設(shè)計(jì),不必改變源程序,只需改變類屬參數(shù)或函數(shù),就可改變設(shè)計(jì)的規(guī)模和結(jié)構(gòu)。1995年我國國家技術(shù)監(jiān)督局制定的《CAD用技術(shù)規(guī)范》推薦將VHDL作為我國電子設(shè)計(jì)自動(dòng)化硬件描述語言的國家標(biāo)準(zhǔn)。VHDL已經(jīng)成為世界上各家EDA工具和集成電路廠商普遍認(rèn)同和共同推廣的標(biāo)準(zhǔn)化硬件描述語言。掌握VHDL,利用VHDL設(shè)計(jì)電子電路,是當(dāng)前進(jìn)行技術(shù)競爭的一項(xiàng)基本技能和強(qiáng)有力工具。

4 EDA軟件

EDA軟件在EDA技術(shù)應(yīng)用中占據(jù)極其重要的地位,EDA的核心是利用計(jì)算機(jī)實(shí)現(xiàn)電路設(shè)計(jì)的自動(dòng)化,因此基于計(jì)算機(jī)環(huán)境下的EDA工具軟件的支持是必不可少的。

EDA軟件品種繁多,目前在我國得到應(yīng)用的有:PSPICE,PCAD,Protel,ViewLogic,Mentor,Graphics,Synopsys,Cadence,Edison,Tina等等。這些軟件功能都很強(qiáng),一般都能應(yīng)用于幾個(gè)方面,大部分軟件都可以進(jìn)行電路設(shè)計(jì)與仿真,F(xiàn)CB自動(dòng)布局布線,可輸出多種網(wǎng)表文件(Netlist)與其他廠商的軟件共享數(shù)據(jù)等等。按它們的主要功能與應(yīng)用領(lǐng)域,可分為電子電路設(shè)計(jì)工具、仿真工具、PCB設(shè)計(jì)軟件、IC設(shè)計(jì)軟件、PID設(shè)計(jì)工具及其它EDA軟件,其中IC設(shè)計(jì)和PID設(shè)計(jì)代表當(dāng)今電子技術(shù)的發(fā)展水平,是該行業(yè)中得到廣泛應(yīng)用的軟件類型。

目前IC設(shè)計(jì)工具發(fā)展迅速,IC領(lǐng)域本身已發(fā)展到ASIC(Application Specific Integrated Circuit)芯片設(shè)計(jì)的階段。著名的IC計(jì)軟件供應(yīng)商有:Cadence,Synopsysl Avanti,Agilenti。

PLD是一種由用戶根據(jù)需要而自行構(gòu)造邏輯功能的數(shù)字集成電路,其設(shè)計(jì)方法是借助于EDA軟件,用原理圖、布爾表達(dá)式、硬件描述語言等方法,生成相應(yīng)的目標(biāo)文件,最后用編程器或下載電纜,由目標(biāo)器件實(shí)現(xiàn)。目前世界上具有代表性的PLD生產(chǎn)廠家有Altera公司、Xilinx公司和Lattice公司。一些小型化、簡單的PLD設(shè)計(jì)工具主要由生產(chǎn)器件的廠家提供,而一些功能強(qiáng)大、大型化的PLD設(shè)計(jì)工具是由軟件公司和生產(chǎn)器件的廠家合作開發(fā)。如Altera公司的Max+PlusⅡ和QuatusⅡ,Lattice公司的Synaric。由于Altera公司實(shí)施的高校合作計(jì)劃,大多數(shù)工程研發(fā)人員在大學(xué)期間最早接觸的使用得最多得也就是Max+PlusⅡ和QuatusⅡ同時(shí)Max+PlusⅡ和QuatusⅡ的開發(fā)工具界面是否友好,操作方便,因此更容易為研發(fā)人員接受。

5 基于EDA技術(shù)的數(shù)字系統(tǒng)層次化

設(shè)計(jì)方法

EDA(Electronic Design Automation)技術(shù)的出現(xiàn)使數(shù)字系統(tǒng)的分析與設(shè)計(jì)方法發(fā)生了根本的變化,采用的基本設(shè)計(jì)萬法主要有三種:直接設(shè)計(jì)、自頂向下(Top-to-Down)設(shè)計(jì)、自底向上(Buttom-to-Up)設(shè)計(jì)。直接設(shè)計(jì)就是將設(shè)計(jì)看成一個(gè)整體,將其設(shè)計(jì)成為一個(gè)單電路模塊,它適合小型簡單的設(shè)計(jì)。而一些功能較復(fù)雜的大型數(shù)字邏輯系統(tǒng)設(shè)計(jì)適合自頂向下或自底向上的設(shè)計(jì)方法。自頂向下的設(shè)計(jì)方法就是從設(shè)計(jì)的總體要求入手,自頂向下地將設(shè)計(jì)劃分為不同的功能子模塊,每個(gè)模塊完成特定的功能,這種設(shè)計(jì)方法首先確定頂層模塊的設(shè)計(jì),再進(jìn)行子模塊的詳細(xì)設(shè)計(jì),而在子模塊的設(shè)計(jì)中可以調(diào)用庫中已有的模塊或設(shè)計(jì)過程中保留下來的實(shí)例。自底向上的設(shè)計(jì)方法與自頂向下的設(shè)計(jì)方法恰恰相反。

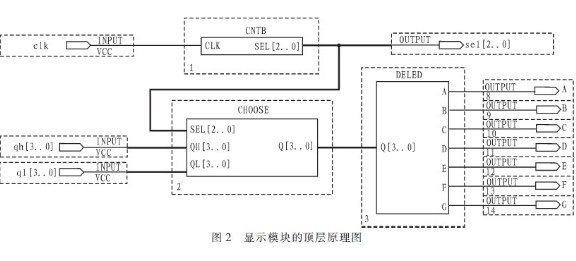

在數(shù)字系統(tǒng)的EDA設(shè)計(jì)中往往采用層次化的計(jì)方法,分模塊、分層次地進(jìn)行設(shè)計(jì)描述。描述系統(tǒng)總功能的設(shè)計(jì)為頂層設(shè)計(jì),描述系統(tǒng)中較小單元的設(shè)計(jì)為底層設(shè)計(jì)。整個(gè)設(shè)計(jì)過程可理解為從硬件的頂層抽象描述向最底層結(jié)構(gòu)描述的一系列轉(zhuǎn)換過程,直到最后得到可實(shí)現(xiàn)的硬件單元描述為止。層次化設(shè)計(jì)方法比較自由,既可采用自頂向下的設(shè)計(jì)也可采用自底向上設(shè)計(jì),可在任何層次使用原理圖輸入和硬件描述語言HDL設(shè)計(jì)。

5.1自底向上的設(shè)計(jì)方法

Buttom-to-Up設(shè)計(jì)方法的中心思想是首先根據(jù)對整個(gè)系統(tǒng)的測試與分析,由各個(gè)功能塊連成一個(gè)完整的系統(tǒng),由邏輯單元組成各個(gè)獨(dú)立的功能模塊,由基本門構(gòu)成各個(gè)組合與時(shí)序邏輯單元。

Buttom-to-Up設(shè)計(jì)方法的特點(diǎn):從底層邏輯庫中直接調(diào)用邏輯門單元;符合硬件工程師傳統(tǒng)的設(shè)計(jì)習(xí)慣;在進(jìn)行底層設(shè)計(jì)時(shí)缺乏對整個(gè)電子系統(tǒng)總體性能的把握;在整個(gè)系統(tǒng)完成后,要進(jìn)行修改較為困難,設(shè)計(jì)周期較長;隨著設(shè)計(jì)規(guī)模與系統(tǒng)復(fù)雜度的提高,這種方法的缺點(diǎn)更突出。

傳統(tǒng)的數(shù)字系統(tǒng)的設(shè)計(jì)方法一般都是自底向上的,即首先確定構(gòu)成系統(tǒng)的最低層的電路模塊或元件的結(jié)構(gòu)和功能,然后根據(jù)主系統(tǒng)的功能要求,將它們組成更大的的功能塊,使它們的結(jié)構(gòu)和功能滿足高層系統(tǒng)的要求,依此類推,直至完成整個(gè)目標(biāo)系統(tǒng)的EDA設(shè)計(jì)。

5.2自頂向下的設(shè)計(jì)方法

Top-to-Down設(shè)計(jì)方法的中心思想是:系統(tǒng)層是一個(gè)包含輸入輸出的頂層模塊,并用系統(tǒng)級、行為描述加以表達(dá),同時(shí)完成整個(gè)系統(tǒng)的模擬和性能分析;整個(gè)系統(tǒng)進(jìn)一步由各個(gè)功能模塊組成,每個(gè)模塊由更細(xì)化的行為描述加以表達(dá);由EDA綜合工具完成到工藝庫的映射。

Top-to-Down設(shè)計(jì)方法的特點(diǎn):結(jié)合模擬手段,可以從開始就掌握實(shí)現(xiàn)目標(biāo)系統(tǒng)的性能狀況;隨著設(shè)計(jì)層次向下進(jìn)行,系統(tǒng)的性能參數(shù)將進(jìn)一步得到細(xì)化與確認(rèn);可以根據(jù)需要及時(shí)調(diào)整相關(guān)的參數(shù),從而保證了設(shè)計(jì)結(jié)果的正確性,縮短了設(shè)計(jì)周期;當(dāng)規(guī)模越大時(shí),這種方法的優(yōu)越性越明顯;須依賴EDA設(shè)計(jì)工具的支持及昂貴的基礎(chǔ)投入;邏輯總合及以后的設(shè)計(jì)過程的實(shí)現(xiàn),均需要精確的工藝庫的支持。

現(xiàn)代數(shù)字系統(tǒng)的設(shè)計(jì)方法一般都自頂向下(Top-to-Down)的層次化設(shè)計(jì)方法,即從整個(gè)系統(tǒng)的整體要求出發(fā),自上而下地逐步將系統(tǒng)設(shè)計(jì)內(nèi)容細(xì)化,即把整個(gè)系統(tǒng)分割為若干功能模塊,最后完成整個(gè)系統(tǒng)的設(shè)計(jì)。

在電子設(shè)計(jì)領(lǐng)域,自頂向下的層次化設(shè)計(jì)方法,只有在EDA技術(shù)得到快速發(fā)展和成熟應(yīng)用的今天才成為可能,自頂向下的層次化設(shè)計(jì)方法的有效應(yīng)用必須基于功能強(qiáng)大的EDA工具,具備集系統(tǒng)描述、行為描述和結(jié)構(gòu)描述功能為一體的硬件描述語言HDL以及先進(jìn)的ASIC制造工藝和CPLD/FPGA開發(fā)技術(shù)。當(dāng)今,自頂向下的層次化設(shè)計(jì)方法已經(jīng)是EDA技術(shù)的首選設(shè)計(jì)方法,是CPLD/FPGA開發(fā)的主要設(shè)計(jì)手段。

6 結(jié)束語

EDA技術(shù)為現(xiàn)代數(shù)字系統(tǒng)理論和設(shè)計(jì)的表達(dá)與應(yīng)用提供了可能性,它已不是某一學(xué)科的分支,而是一門綜合性學(xué)科。EDA技術(shù)打破了計(jì)算機(jī)軟件與硬件間的壁壘,是計(jì)算機(jī)的軟件技術(shù)與硬件實(shí)現(xiàn)、設(shè)計(jì)效率和產(chǎn)品性能合二為一,它代表了數(shù)字電子設(shè)計(jì)技術(shù)和應(yīng)用技術(shù)的發(fā)展方向。

EDA技術(shù)可廣泛應(yīng)用于科研、教學(xué)工作及新型電子產(chǎn)品的開發(fā)中。EDA技術(shù)是電子設(shè)計(jì)與計(jì)算機(jī)相結(jié)合的產(chǎn)物,而它的產(chǎn)生又極大地推動(dòng)了前者的發(fā)展。目前正是EDA技術(shù)的高速發(fā)展階段。在EDA技術(shù)開發(fā)方面,主要集中在美國等西方發(fā)達(dá)國家,新的EDA工具層出不窮。日本、韓國等亞洲國家也十分重視EDA技術(shù)的開發(fā)。我國EDA技術(shù),無論開發(fā)還是應(yīng)用都遠(yuǎn)遠(yuǎn)落后于發(fā)達(dá)國家,這也是我國信息技術(shù)集成電路產(chǎn)業(yè)的整體現(xiàn)狀EDA技術(shù)也是信息產(chǎn)業(yè)部軟件與集成電路促進(jìn)中心的“國家信息技術(shù)緊缺人才培養(yǎng)工程”重點(diǎn)培訓(xùn)內(nèi)容,為實(shí)現(xiàn)將中國從世界制造大國發(fā)展為世界技術(shù)強(qiáng)國,廣大電子工程人員應(yīng)加快學(xué)習(xí)和應(yīng)用,提高自身的競爭能力,適應(yīng)EDA技術(shù)的迅猛發(fā)展。

? ? ? ?責(zé)任編輯:tzh

電子發(fā)燒友App

電子發(fā)燒友App

評論