在 NXP,我們團隊開發(fā)了一種新方法學(xué)來驗證汽車雷達集成電路 (IC) 的設(shè)計。該左移(或稱“流程前置”)方法學(xué)將規(guī)格書級別指標的早期驗證與虛擬現(xiàn)場試驗相結(jié)合。

2022-03-15 17:28:34 9536

9536 門級仿真(gate levelsimulation)也稱之為后仿真,是數(shù)字IC設(shè)計流程中的一個重要步驟。

2023-06-07 09:55:42 1207

1207

的反應(yīng)是否與特性列表和設(shè)計規(guī)格說明書中的一致,如中斷是否置起。DUT是否足夠穩(wěn)健,能夠從異常狀態(tài)中恢復(fù)到正常的工作模式。關(guān)于《IC驗證》就介紹到這里!!!更多ic設(shè)計內(nèi)容請關(guān)注后續(xù)更新............

2020-12-01 14:39:13

不太對,查了一下資料,那里是不太對啊,簡直是一點都不對,暴寒啊,也許是自己真是好久沒做IC方面的東西了。一般的IC設(shè)計流程可以分為兩大類:全定制和半定制,這里我換一種方式來說明。 1.1 從RTL到

2012-01-11 13:49:27

驗證范疇,它主要是在時序上對電路進行驗證,檢查電路是否存在建立時間(setup time)和保持時間(hold time)的違例(violation)。這個是數(shù)字電路基礎(chǔ)知識,一個寄存器出現(xiàn)這兩個時序

2018-08-13 17:05:29

1.1 從RTL到GDSⅡ的設(shè)計流程: 這個可以理解成半定制的設(shè)計流程,一般用來設(shè)計數(shù)字電路。整個流程如下(左側(cè)為流程,右側(cè)為用到的相應(yīng)EDA工具): 一個完整的半定制設(shè)計流程應(yīng)該是:RTL代碼

2018-08-16 09:14:32

關(guān)于IC設(shè)計的流程是怎樣的?有關(guān)IC設(shè)計的方法有哪些?

2021-06-21 07:51:54

IC設(shè)計流程和設(shè)計方法

2012-08-20 22:15:19

今天更新一篇數(shù)字IC低功耗設(shè)計方法總結(jié),內(nèi)容參考的是郭煒老師的書:《SoC設(shè)計方法與實現(xiàn)(第3版)》,希望能給大家?guī)韼椭鷡

2021-07-29 06:38:58

。不同階段的需要不同的驗證方法,比如:在算法級,可以使用c,c++或者是matlab對算法進行建模,驗證算法的可行性,再比如:對rtl進行功能驗證來檢查rtl是否滿足我們的要求等。我們現(xiàn)在將要學(xué)習

2021-01-21 15:59:03

數(shù)字IC就是傳遞、加工、處理數(shù)字信號的IC,是近年來應(yīng)用最廣、發(fā)展最快的IC品種,可分為通用數(shù)字IC和專用數(shù)字IC。數(shù)字前端以設(shè)計架構(gòu)為起點,以生成可以布局布線的網(wǎng)表為終點;是用設(shè)計的電路實現(xiàn)想法

2021-07-28 08:27:47

后端設(shè)計流程、版圖布局布線、版圖編輯、版圖物理驗證、聯(lián)絡(luò)代工廠并提交生產(chǎn)數(shù)據(jù)。 數(shù)字后端設(shè)計流程如下圖: 數(shù)字IC設(shè)計后端流程如上圖所示,主要是以下步驟: 1.邏輯綜合是將RTL代碼映射為與工藝

2020-12-29 11:53:01

數(shù)字IC是什么意思?數(shù)字IC前端設(shè)計流程有哪些?數(shù)字IC后端設(shè)計流程有哪些?

2021-10-20 06:24:49

數(shù)字IC設(shè)計之DC篇:DC流程介紹綜合概念綜合是使用軟件的方法來設(shè)計硬件, 然后將門級電路實現(xiàn)與優(yōu)化的工作留給綜合工具的 一種設(shè)計方法。它是根據(jù)一個系統(tǒng)邏輯功能與性能的要求,在一個包含眾多結(jié)構(gòu)、功能

2021-11-17 07:08:49

到非常高的位置。 那么哪里可以學(xué)習數(shù)字ic設(shè)計呢,可以參考了解(IC修真院),我學(xué)習過這個課程,包含數(shù)字前端設(shè)計、驗證、后端設(shè)計等,從基礎(chǔ)知識,理論知識,技術(shù)原理,架構(gòu)設(shè)計,分析問題能力,從應(yīng)用到知識點,應(yīng)有全有,實戰(zhàn)部分完全還原真實企業(yè)項目,是真正能提高實戰(zhàn)應(yīng)用能力的。

2020-12-04 14:31:30

數(shù)字IC設(shè)計之“數(shù)字SOC全流程漫談從0到1”講師背景:閻如斌老師畢業(yè)于慕尼黑工業(yè)大學(xué)的碩士研究生,具有非常豐富的IC研發(fā)經(jīng)驗。在集成電路的從業(yè)10多年之久,同時也是叩持電子和IC修真院的創(chuàng)始人,并

2020-12-07 17:39:10

數(shù)字IC設(shè)計工程師-上海職位要求: 1、電子類相關(guān)專業(yè),本科或本科以上學(xué)歷 2、熟悉數(shù)字IC設(shè)計流程,熟練掌握verilogHDL coding,DC/PT/FT等工具 3、有FPGA設(shè)計經(jīng)驗者優(yōu)先

2015-06-15 10:06:11

設(shè)計4. 完成芯片設(shè)計流程,包括RTL代碼編寫、驗證,綜合、時序檢查、布局布線。職位需求:1. 具有3年以上IC設(shè)計經(jīng)驗,電子或計算機博士/碩士學(xué)位。2. 能夠獨立設(shè)計芯片頂層或主要模塊。3. 有SOC

2013-04-23 10:17:25

數(shù)字電路和與模擬電路的本質(zhì)區(qū)別是什么?數(shù)字IC設(shè)計流程有哪些?

2021-10-26 06:51:04

數(shù)字IC設(shè)計之“數(shù)字SOC全流程漫談從0到1”講師背景:閻如斌老師畢業(yè)于慕尼黑工業(yè)大學(xué)的碩士研究生,具有非常豐富的IC研發(fā)經(jīng)驗。在集成電路的從業(yè)10多年之久,同時也是叩持電子和IC修真院的創(chuàng)始人,并

2021-11-11 06:21:02

數(shù)字芯片設(shè)計流程前端設(shè)計的主要流程:規(guī)格制定芯片規(guī)格: 芯片需要達到的具體功能和性能方面的要求詳細設(shè)計就是根據(jù)規(guī)格要求,實施具體架構(gòu),劃分模塊功能。HDL編碼使用硬件描述語言(vhdlVerilog

2020-02-12 16:09:48

數(shù)字芯片設(shè)計流程:功能驗證之前與工藝庫沒多大聯(lián)系,驗證芯片設(shè)計的功能是否正確,針對抽象的代碼進行功能驗證理想值。一致性驗證確保生成的網(wǎng)表和代碼設(shè)計功能一致;DFT之后是數(shù)字后端。靜態(tài)時序分析,從邏輯

2021-11-10 06:14:28

在支持高階自動化上的生產(chǎn)力優(yōu)勢。本文接著提出模擬設(shè)計及驗證技術(shù)演進的概觀,并且拿來跟數(shù)字的自動化能力做對比。 最后,本文討論了模擬工具必須予以強化以支持更高階自動化的方法;同時也闡述了現(xiàn)代化IC設(shè)計環(huán)境必須強化的方法,以具備足以支持真正的、統(tǒng)一的、全芯片混合信號設(shè)計、驗證、及實現(xiàn)的能力。

2019-06-27 07:24:51

& IP Core Verification)”卷。 本章介紹了 IC 和 IP 核設(shè)計過程驗證中涉及的一些關(guān)鍵 Python 方法、工具、包和庫,包括以下章節(jié): 純 Python

2022-11-03 13:07:24

數(shù)字IC設(shè)計-廣東職責: 數(shù)字電路設(shè)計和驗證;任務(wù): 1、系統(tǒng)架構(gòu)設(shè)計和SOC系統(tǒng)整合;2、Interface電路設(shè)計和驗證。任職資格: 1、計算機和微電子相關(guān)專業(yè),碩士以上學(xué)歷;2、熟悉數(shù)字

2013-12-13 17:49:21

SystemVerilog 的VMM 驗證方法學(xué)教程教材包含大量經(jīng)典的VMM源代碼,可以實際操作練習的例子,更是ic從業(yè)人員的絕佳學(xué)習資料。SystemVerilog 的VMM 驗證方法學(xué)教程教材[hide][/hide]

2012-01-11 11:21:38

海思成研無線部門高薪招聘數(shù)字IC設(shè)計/驗證高級工程師,在這里您可以近距離接觸業(yè)界最前沿的技術(shù)、最先進的工藝、最牛的設(shè)計和驗證水平;在這里您跟FELLOW一起共事,享受濃厚的技術(shù)氛圍;在這里您可感受到

2020-02-29 11:06:28

`IC芯片就像是用樂高積木蓋房子一樣,藉由一層又一層的堆棧,創(chuàng)造自己所期望的造型。然而,蓋房子有相當多的步驟,IC制造也是一樣,制造IC究竟有哪些步驟?小編在此介紹下IC芯片制造的流程。層層堆棧

2018-06-14 14:32:27

要求: 1.兩年以上數(shù)字后端工作經(jīng)驗,熟練使用ICC或Encounter,熟悉IC后端流程。 2.具有大規(guī)模芯片流片經(jīng)驗,有mixed signal layout經(jīng)驗者優(yōu)先。 3.理解時序/分析和優(yōu)化

2017-03-03 14:53:07

非常清楚的, 下面就數(shù)字電路聊聊芯片設(shè)計的一些事情,就是芯片設(shè)計有哪些活做, 這并不是全面完整的系統(tǒng)介紹,只是個人的了解和總結(jié), 希望拋磚引玉,也許不全面, 不正確, 歡迎同學(xué)們指正和補充 說到數(shù)字芯片

2013-01-04 17:07:12

我大三即將轉(zhuǎn)方向了.我想去IC班,進行數(shù)字IC的研究,請問下數(shù)字IC需要學(xué)單片機作為入門嗎(其實我不太想學(xué)).而且數(shù)字IC的paper好寫嗎

2015-11-08 07:35:54

`我大三即將轉(zhuǎn)方向了.我想去IC班,進行數(shù)字IC的研究,請問下數(shù)字IC需要學(xué)單片機作為入門嗎(其實我不太想學(xué)).而且數(shù)字IC的paper好寫嗎?求助謝謝`

2015-11-08 18:00:34

(back-annotated)時序再次驗證。 此基本流程讓Fusion使用者可以利用經(jīng)證實的方法,在設(shè)計過程中的任何階段驗證混合信號PSC的系統(tǒng)層級行為,就宛如全數(shù)字芯片般簡單。此流程依據(jù)客戶設(shè)計中整合其余數(shù)字系統(tǒng)的某個模擬輸入組合執(zhí)行仿真系統(tǒng)層級行為必要的工作。

2011-10-16 22:55:10

1 簡介隨著設(shè)計的復(fù)雜程度不斷增加,要求把更多的資源放到驗證上,不但要求驗證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應(yīng)異常的處理狀態(tài),這在傳統(tǒng)測試方法下往往是難以實現(xiàn)的。此外

2019-07-03 07:40:26

數(shù)字芯片內(nèi)部的架構(gòu)是由哪些部分組成的?數(shù)字IC設(shè)計的流程主要分為哪幾大步?每個流程使用的EDA工具有哪些?

2021-06-18 08:29:52

實例狀態(tài)機的設(shè)計方法介紹;數(shù)據(jù)選擇器狀態(tài)機實現(xiàn)方法與仿真驗證獨立按鍵消抖的狀態(tài)機實現(xiàn)方法、仿真驗證與板級驗證紅外遙控解碼的狀態(tài)機實現(xiàn)方法、仿真驗證與班級驗證 線性序列機設(shè)計方法介紹;數(shù)字波形序列發(fā)生器的線性

2015-06-15 22:01:45

數(shù)字設(shè)計及驗證技術(shù)演進的概觀現(xiàn)代化IC設(shè)計環(huán)境必須強化的方法

2021-04-09 06:17:44

成都-急招數(shù)字驗證/Leader:崗位一(學(xué)習平臺大):需要無線通信類驗證崗位,團隊芯片驗證大牛多(大企業(yè)10-20多年經(jīng)驗),學(xué)習和進步空間大,薪資范圍40-50W;崗位二(晉升平臺大):需要數(shù)字

2018-09-29 10:56:10

《ic設(shè)計流程與使用工具介紹》我認為IC設(shè)計流程按照功能和應(yīng)用場合不同大致可以劃分為三個部分進行介紹,分別是數(shù)字IC、模擬IC和FPGA。這三者之間既有相同點又有相異點。在進行設(shè)計時,所使用的軟件

2013-01-07 17:10:35

數(shù)字IC后端設(shè)計-深圳 s上海 杭州崗位要求:1、對數(shù)字設(shè)計從netlist到gds流程的基本原理和概念有深刻的認識;2、能獨立承擔百萬instance規(guī)模的數(shù)字自動布局布線工作;3、熟練

2018-08-02 16:18:53

關(guān)于時序邏輯等效性的RTL設(shè)計和驗證流程介紹。

2021-04-28 06:13:14

溝通和合作;3、熟練使用設(shè)計工具進行模擬IC線路設(shè)計,熟悉版圖設(shè)計流程并具備相關(guān)設(shè)計能力;4、有高壓功率驅(qū)動電路開發(fā)經(jīng)驗優(yōu)先5、碩士及以上學(xué)歷,電子專業(yè)相關(guān)數(shù)字IC設(shè)計工作職責:1、 依照產(chǎn)品定義完成

2016-11-16 15:50:13

AMSVERIFICATION)。我們服務(wù)的對象主要是美國和日本的大型芯片設(shè)計公司。這些公司之前應(yīng)用的是模擬部分和數(shù)字部分分開驗證的傳統(tǒng)方法,但是經(jīng)常會出現(xiàn)模數(shù)之間連接和時序等問題。在應(yīng)用了芯片級模數(shù)混合驗證

2011-03-23 19:36:31

硬件驗證方法簡明介紹本書“硬件驗證方法簡明介紹”是“半導(dǎo)體 IP 核——不僅僅是設(shè)計”系列叢書中“驗證 IP 和 IP 核驗證”的一部分。本書調(diào)查、處理和介紹了 IC 驗證中涉及的一些關(guān)鍵方法、工具

2022-11-26 20:43:20

。數(shù)字IC設(shè)計工程師-西安1.負責SOC芯片設(shè)計,協(xié)助芯片驗證,測試等工作;2.開發(fā)部分數(shù)字模塊,并進行驗證,測試等工作,編寫相應(yīng)的設(shè)計文檔。職位要求:1.通訊工程、電子信息工程等相關(guān)專業(yè);2.具有

2017-07-13 17:42:23

群主好,我想請教數(shù)字電路的系統(tǒng)級設(shè)計驗證工具及流程?即系統(tǒng)工程師常用的硬件描述語言,系統(tǒng)驗證工具以及設(shè)計驗證的基本流程,多謝!

2012-09-05 15:11:23

請問遠程執(zhí)行IC驗證是怎么實現(xiàn)的?

2021-06-17 10:27:33

資深數(shù)字IC設(shè)計-合肥 西安 上海 珠海職位描述:IC前端設(shè)計及SOC系統(tǒng)工作,包括rtl coding,design綜合,靜態(tài)時序分析及收斂,芯片整合及驗證相關(guān)工作1、使用Synopsys

2015-11-18 16:46:53

資深數(shù)字IC設(shè)計-合肥 西安 上海 珠海職位描述:IC前端設(shè)計及SOC系統(tǒng)工作,包括rtl coding,design綜合,靜態(tài)時序分析及收斂,芯片整合及驗證相關(guān)工作1、使用Synopsys

2015-12-04 17:58:37

資深數(shù)字IC設(shè)計工程師-珠海 上海職責: 數(shù)字電路設(shè)計和驗證;任務(wù): 系統(tǒng)架構(gòu)設(shè)計和SOC系統(tǒng)整合 Interface電路設(shè)計和驗證 任職資格: 1.計算機和微電子相關(guān)專業(yè),碩士以上學(xué)歷; 2.熟悉數(shù)字

2015-06-12 15:29:09

verilog設(shè)計語言,數(shù)字IC設(shè)計流程 (simulation ,synthesis ,STA , etc)及相關(guān)EDA軟件;7. 有FPGA驗證經(jīng)驗者優(yōu)先;8. 有WIFI,Bluetooth,RFID

2017-08-09 17:08:24

本帖最后由 eehome 于 2013-1-5 09:47 編輯

前記:在很多電子網(wǎng)站上看到很多介紹IC或者FPGA設(shè)計工具系統(tǒng)的資料,但是感覺都不是很綜合。所以這里嘗試做一個2012

2012-12-28 17:00:22

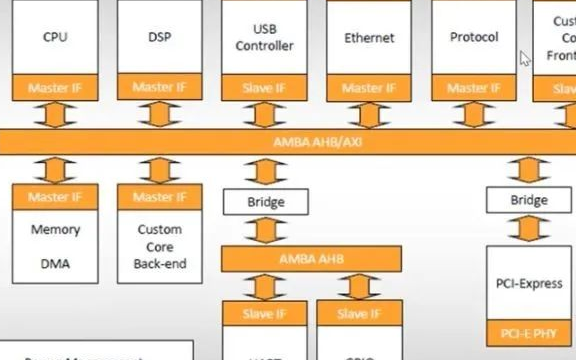

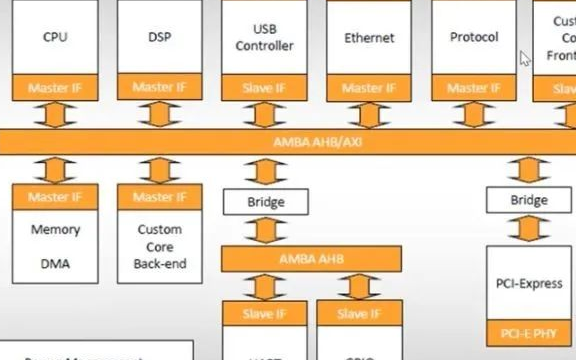

在介紹嵌入式 SoC IC 概念的基礎(chǔ)上,介紹基于重用(re-use)的 SoC IC 設(shè)計方法和流程, 涉及滿足時序要求、版圖設(shè)計流程和測試設(shè)計的問題, 并給出設(shè)計計劃考慮項目。

2009-05-13 16:09:42 28

28 一種全新的深亞微米IC設(shè)計方法

本文分析了傳統(tǒng)IC設(shè)計流程存在的一些缺陷,并且提出了一種基于Logical Effort理論的全新IC設(shè)計方法。

眾所周知,傳統(tǒng)的IC設(shè)計流

2009-12-27 13:28:50 615

615

IC設(shè)計流程圖

?

2010-02-06 16:22:26 5013

5013

集成電路設(shè)計流程 集成電路設(shè)計方法 數(shù)字集成電路設(shè)計流程 模擬集成電路設(shè)計流程 混合信號集成電路設(shè)計流程 SoC芯片設(shè)計流程

2011-03-31 17:09:12 380

380 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語言,采用驗證方法學(xué)以及驗證庫開發(fā)出先進驗證環(huán)境。文章分為四部分,第一部分概述了用SystemVerilog語言驗證復(fù)雜S

2011-05-09 15:22:02 52

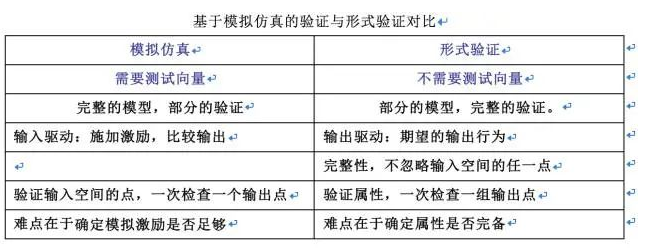

52 介紹了基于深亞微米 CMOS 工藝A S IC 電路設(shè)計流程中的靜態(tài)驗證方法。將這種驗證方法與以往的動態(tài)驗證方法進行了比較, 結(jié)果表明, 前者比后者更加高效和準確。由此可以說明, 靜態(tài)驗證

2011-06-21 15:05:00 0

0 IC制造流程簡介

2016-12-21 16:48:07 668

668 IC設(shè)計流程和方法復(fù)旦講義

2017-10-18 10:13:55 22

22 一般的IC設(shè)計流程可以分為兩大類:全定制和半定制,這里我換一種方式來說明。 1.1 從RTL到GDSⅡ的設(shè)計流程: 這個可以理解成半定制的設(shè)計流程,一般用來設(shè)計數(shù)字電路。 整個流程如下(左側(cè)為流程

2017-10-20 11:38:20 25

25 IC就是半導(dǎo)體元件產(chǎn)品的統(tǒng)稱,IC按功能可分為:數(shù)字IC、模擬IC、微波IC及其他IC。數(shù)字IC就是傳遞、加工、處理數(shù)字信號的IC,是近年來應(yīng)用最廣、發(fā)展最快的IC品種,可分為通用數(shù)字IC和專用數(shù)字IC。

2018-03-23 16:56:09 33583

33583 本文首先介紹了ic設(shè)計的方法,其次介紹了IC設(shè)計前段設(shè)計的主要流程及工具,最后介紹了IC設(shè)計后端設(shè)計的主要流程及工具。

2018-04-19 18:04:45 11661

11661 來自中國北京的電子設(shè)計自動化(EDA)解決方案供應(yīng)商華大九天日前宣布,其模擬/混合信號全流程IC設(shè)計解決方案已正式進入TowerJazz公司參考流程,并已通過工藝設(shè)計工具包(iPDK)的質(zhì)量驗證。

2018-08-30 17:12:31 1891

1891 本文將介紹基于正式方法的數(shù)字IP驗證的不同方法,通過定義屬性詳盡地驗證功能。正式方法具有避免開發(fā)測試臺的優(yōu)點。這一新流程已在數(shù)字IP設(shè)計過程中使用,并已證明可顯著縮短驗證時間。

2019-08-08 17:13:07 3545

3545

? ? 數(shù)字IC設(shè)計流程是每個IC從業(yè)者的第一課,無論你是做前端,后端,還是驗證,都需要對芯片的整個設(shè)計流程有個基本的了解。 本文章主要介紹以下三點內(nèi)容: 一. 數(shù)字IC設(shè)計的流程及每個流程需要

2020-12-09 10:12:11 6448

6448

5G單站驗證流程課件下載

2021-03-19 09:17:48 0

0 數(shù)字IC設(shè)計之“數(shù)字SOC全流程漫談從0到1”講師背景:閻如斌老師畢業(yè)于慕尼黑工業(yè)大學(xué)的碩士研究生,具有非常豐富的IC研發(fā)經(jīng)驗。在集成電路的從業(yè)10多年之久,同時也是叩持電子和IC修真院的創(chuàng)始人

2021-11-05 20:51:02 15

15 數(shù)字IC就是傳遞、加工、處理數(shù)字信號的IC,是近年來應(yīng)用最廣、發(fā)展最快的IC品種,可分為通用數(shù)字IC和專用數(shù)字IC。數(shù)字前端以設(shè)計架構(gòu)為起點,以生成可以布局布線的網(wǎng)表為終點;是用設(shè)計的電路實現(xiàn)想法

2021-11-06 16:51:05 26

26 數(shù)字IC設(shè)計之DC篇:DC流程介紹綜合概念綜合是使用軟件的方法來設(shè)計硬件, 然后將門級電路實現(xiàn)與優(yōu)化的工作留給綜合工具的 一種設(shè)計方法。它是根據(jù)一個系統(tǒng)邏輯功能與性能的要求,在一個包含眾多結(jié)構(gòu)、功能

2021-11-09 20:06:00 13

13 芯片驗證就是采用相應(yīng)的驗證語言,驗證工具,驗證方法,在芯片生產(chǎn)之前驗證芯片設(shè)計是否符合芯片定義的需求規(guī)格,是否已經(jīng)完全釋放了風險,發(fā)現(xiàn)并更正了所有的缺陷,站在全流程的角度,它是一種防范于未然的措施。

2022-07-25 11:48:49 5263

5263 隨著芯片規(guī)模不斷加大,在IC設(shè)計過程中驗證的復(fù)雜度也進一步加到,需要的用到的崗位人數(shù)也越來越多;很多大公司,數(shù)字前端設(shè)計工程師與驗證工程師的比例已經(jīng)達到1:3。

2022-10-25 15:13:04 1017

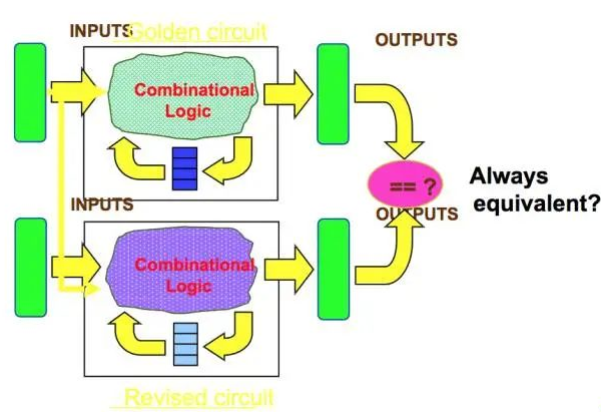

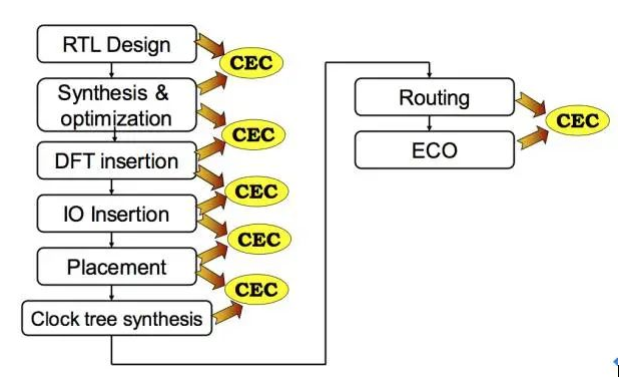

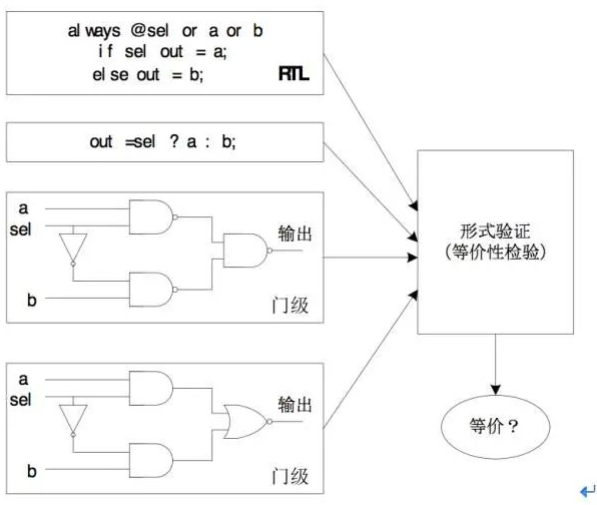

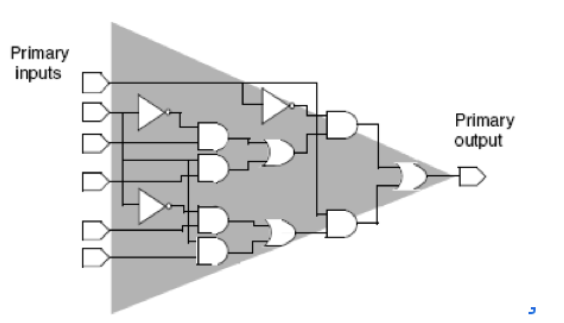

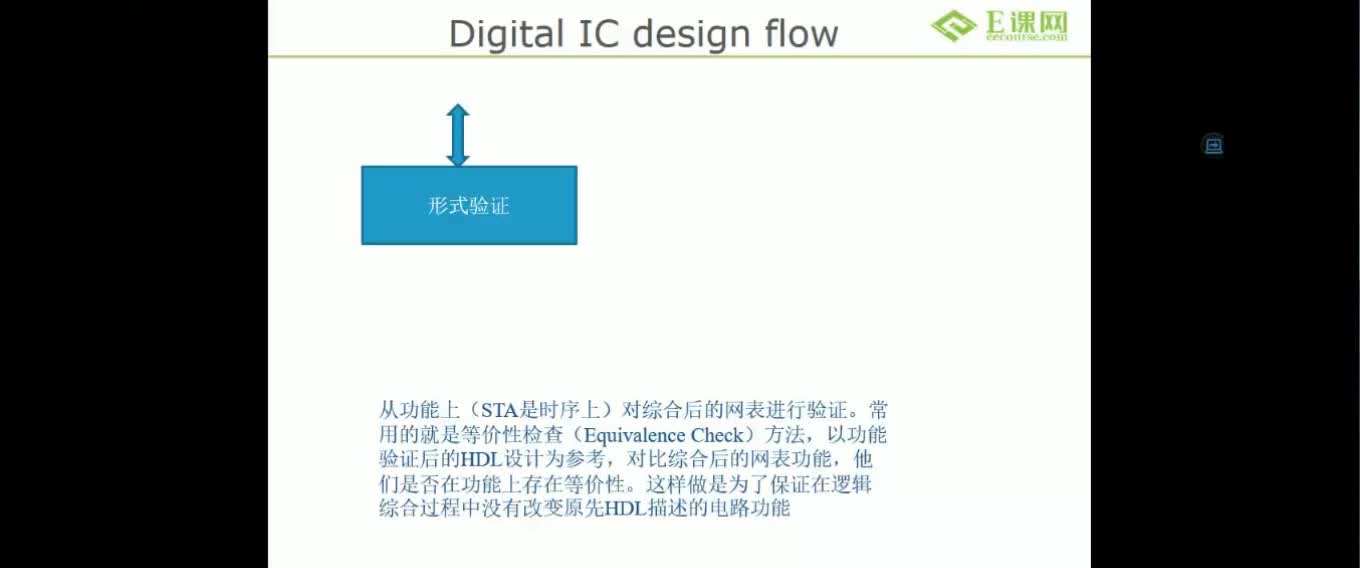

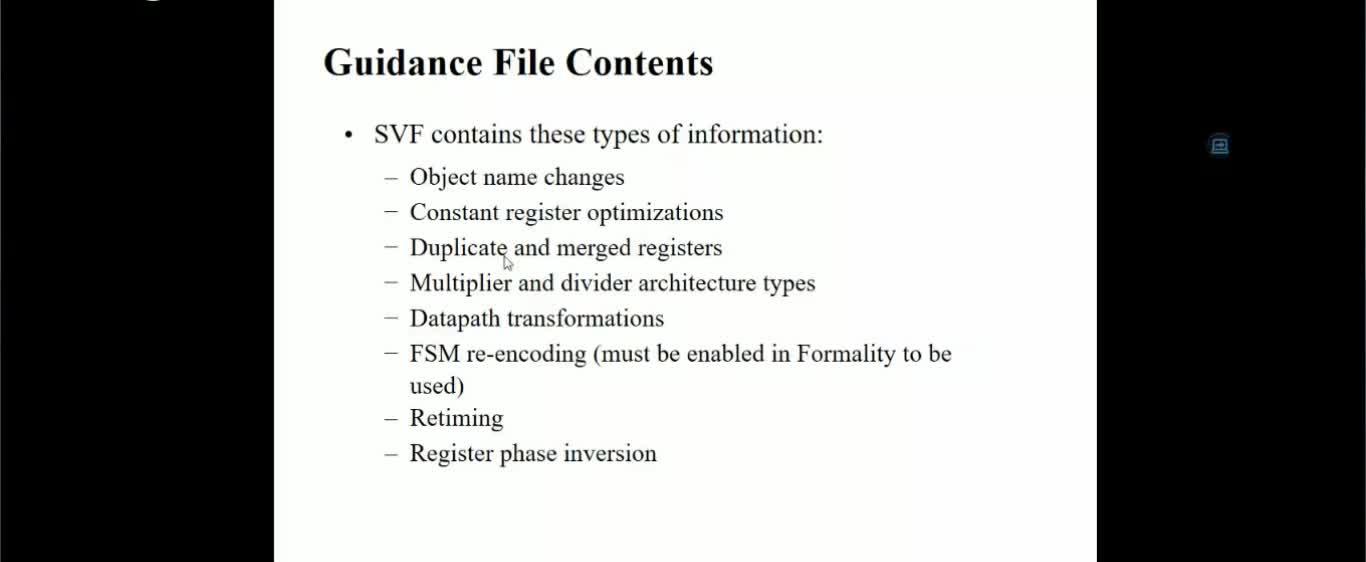

1017 和靜態(tài)時序分析工具一起來完成對電路完備的驗證。本文就以Synopsys公司的formality工具為例,來介紹形式驗證的流程和基本概念,后續(xù)會詳細介紹使用formality做RTL2Gate流程中每一步驟的操作。

2022-12-27 15:18:11 1177

1177 IC設(shè)計和IC驗證都是非常重要的環(huán)節(jié),一個好的IC產(chǎn)品需要二者的配合。IC設(shè)計是在滿足產(chǎn)品規(guī)格書的前提下,實現(xiàn)電路性能、功耗、面積等方面的優(yōu)化,從而滿足設(shè)計需求的過程。而IC驗證是在設(shè)計完成后,必須對所設(shè)計的芯片進行正確性、可靠性、功耗等方面的驗證。

2023-04-12 14:01:33 2603

2603 IC設(shè)計和IC驗證都是非常重要的環(huán)節(jié),一個好的IC產(chǎn)品需要二者的配合。IC設(shè)計是在滿足產(chǎn)品規(guī)格書的前提下,實現(xiàn)電路性能、功耗、面積等方面的優(yōu)化,從而滿足設(shè)計需求的過程。而IC驗證是在設(shè)計完成后,必須對所設(shè)計的芯片進行正確性、可靠性、功耗等方面的驗證。

2023-04-13 17:50:50 4535

4535 驗證其實是一個“證偽”的過程,從流程到工具,驗證工程師的終極目的都只有一個。

2023-05-31 10:34:49 1069

1069 IC設(shè)計流程從設(shè)計到驗證是一個復(fù)雜而精細的過程,需要多個設(shè)計工具和驗證手段的支持。不同的設(shè)計流程可能會有所差異,具體的設(shè)計流程也會根據(jù)項目需求和技術(shù)發(fā)展的變化而有所調(diào)整。

2023-06-27 17:07:20 264

264 IC設(shè)計是一門非常復(fù)雜的科學(xué),在IC生產(chǎn)流程中,IC芯片主要由專業(yè)IC設(shè)計公司進行規(guī)劃、設(shè)計,如聯(lián)發(fā)科、高通、Intel等國際知名大廠,都自行設(shè)計各自專精的IC芯片,提供不同規(guī)格、效能的芯片給下游客戶選擇。

2023-07-19 08:58:59 981

981

IC驗證,即集成電路驗證(Integrated Circuit Verification),是指針對硬件設(shè)計中的集成電路(IC)進行的一系列功能驗證、性能驗證和正確性驗證的過程。它是電子設(shè)計自動化(EDA)領(lǐng)域中非常重要的環(huán)節(jié),用于確保設(shè)計的集成電路在實際生產(chǎn)中能夠正常運行。

2023-07-24 15:45:18 2094

2094 ic驗證是封裝與測試么?? IC驗證是現(xiàn)代電子制造過程中非常重要的環(huán)節(jié)之一,它主要涉及到芯片產(chǎn)品的驗證、測試、批量生產(chǎn)以及質(zhì)量保證等方面。 IC驗證包含兩個重要的環(huán)節(jié),即芯片設(shè)計驗證和芯片生產(chǎn)驗證

2023-08-24 10:42:13 464

464 首屆IDAS設(shè)計自動化產(chǎn)業(yè)峰會將于9月18日在武漢中國光谷科技會展中心舉行。作為國內(nèi)領(lǐng)先的系統(tǒng)級驗證EDA解決方案提供商,芯華章受邀參展,將帶來完整的數(shù)字驗證全流程工具及客制化解決方案,與全球行業(yè)

2023-08-29 09:10:02 554

554

在IC設(shè)計中,設(shè)計師使用電路設(shè)計工具(如EDA軟件)來設(shè)計和模擬各種電路,例如邏輯電路、模擬電路、數(shù)字信號處理電路等。然后,根據(jù)設(shè)計電路的規(guī)格要求,進行布局設(shè)計和布線,確定各個電路元件的位置和連線方式。最后,進行物理設(shè)計,考慮電磁兼容性、功耗優(yōu)化、時序等問題,并生成芯片制造所需的掩膜信息。

2023-08-30 17:07:54 1622

1622 芯片設(shè)計的邏輯仿真和數(shù)字驗證是芯片設(shè)計流程中非常重要的一環(huán),它主要用于驗證芯片的功能和時序等方面的正確性。下面是邏輯仿真和數(shù)字驗證的一般流程: 設(shè)計規(guī)格和功能驗證:在開始邏輯仿真之前,首先需要明確

2023-09-14 17:11:23 720

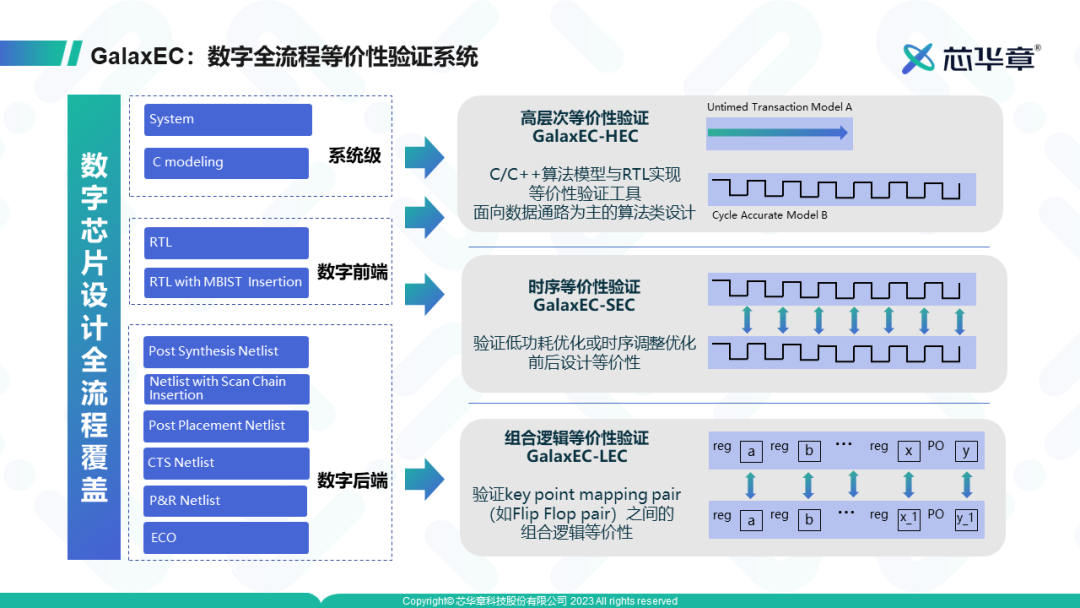

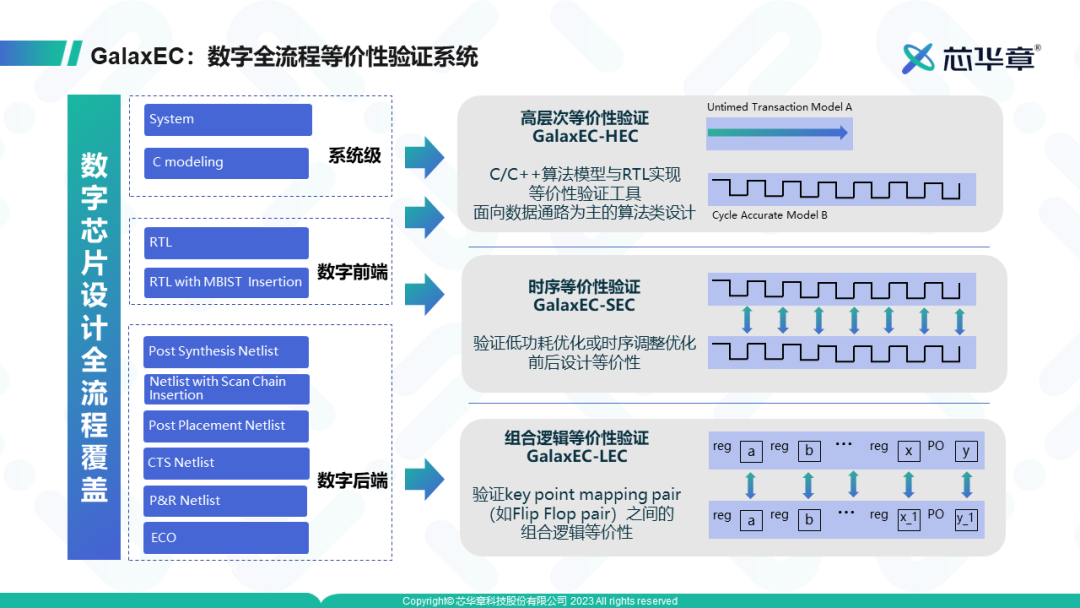

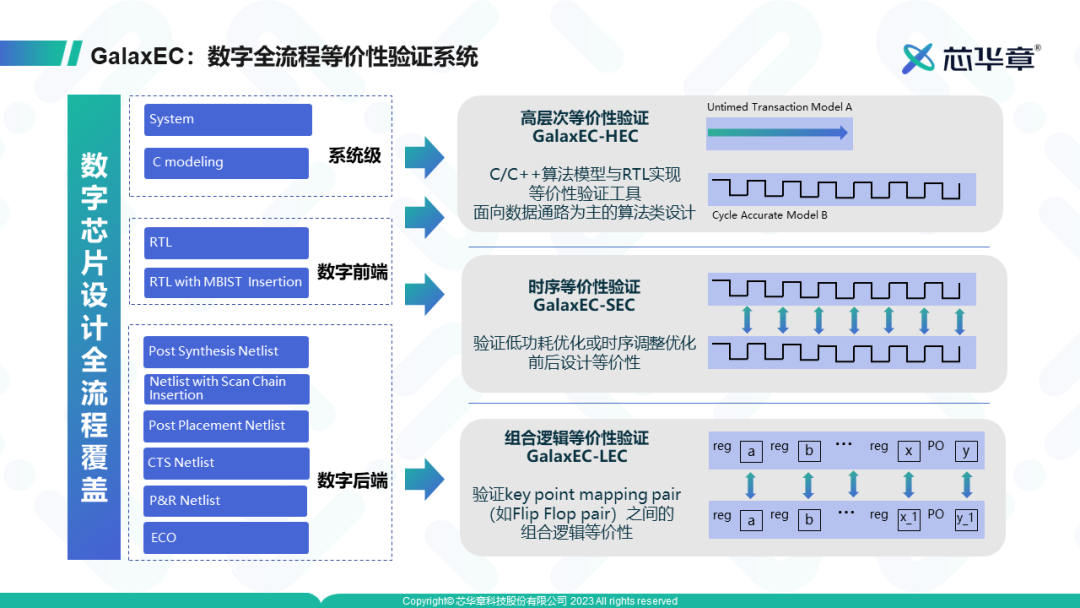

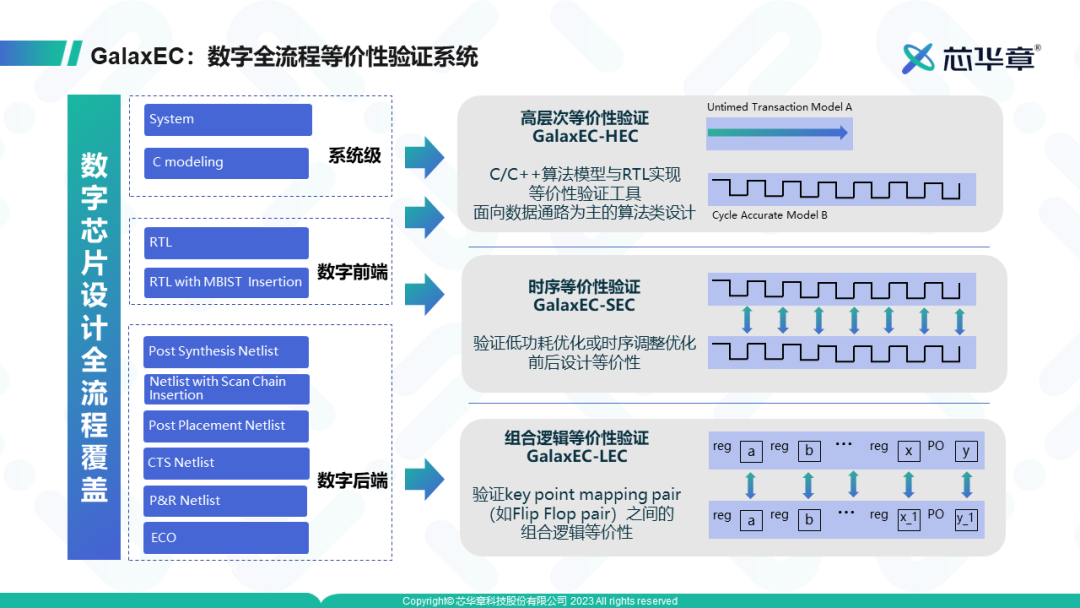

720 的系統(tǒng)級驗證EDA解決方案提供商芯華章,隆重發(fā)布 首款自主研發(fā)的數(shù)字全流程等價性驗證系統(tǒng)穹鵬GalaxEC 。 隨著GalaxEC的發(fā)布, 芯華章自主EDA工具完成了對數(shù)字驗證全流程的完整覆蓋 ,進一步

2023-09-19 09:18:05 225

225

及相關(guān)專業(yè)人士,業(yè)內(nèi)領(lǐng)先的系統(tǒng)級驗證EDA解決方案提供商芯華章,隆重發(fā)布 首款自主研發(fā)的數(shù)字全流程等價性驗證系統(tǒng)穹鵬GalaxEC 。 隨著GalaxEC的發(fā)布, 芯華章自主EDA工具完成了對數(shù)字驗證

2023-09-19 11:05:04 227

227

設(shè)計的要求運行。 本文將詳細介紹數(shù)字電路設(shè)計的仿真驗證流程,以及每個步驟的重要性和方法。 仿真驗證的目標: 在設(shè)計階段,仿真驗證的目標是驗證電路的功能正確性、時序正確性和性能指標是否滿足設(shè)計要求。通過仿真驗證,

2024-01-02 17:00:43 256

256 FPGA原型驗證流程是確保FPGA(現(xiàn)場可編程門陣列)設(shè)計正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計實現(xiàn)到功能驗證的整個過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 97

97

電子發(fā)燒友App

電子發(fā)燒友App

評論