Verilog規(guī)范對于一個(gè)好的IC設(shè)計(jì)至關(guān)重要。

本文包含以下幾方面內(nèi)容,程序設(shè)計(jì),模塊例化、運(yùn)算符,模塊設(shè)計(jì)模板

目標(biāo):用最簡單,最簡潔的方式,設(shè)計(jì)最易讀,最高效的代碼

1、程序設(shè)計(jì)

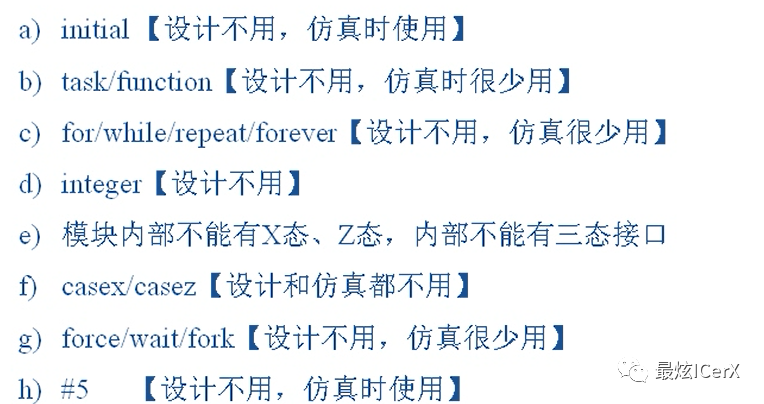

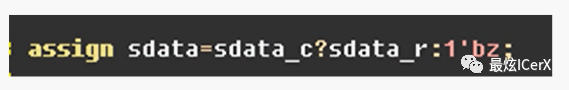

1)設(shè)計(jì)時(shí)不用的語法

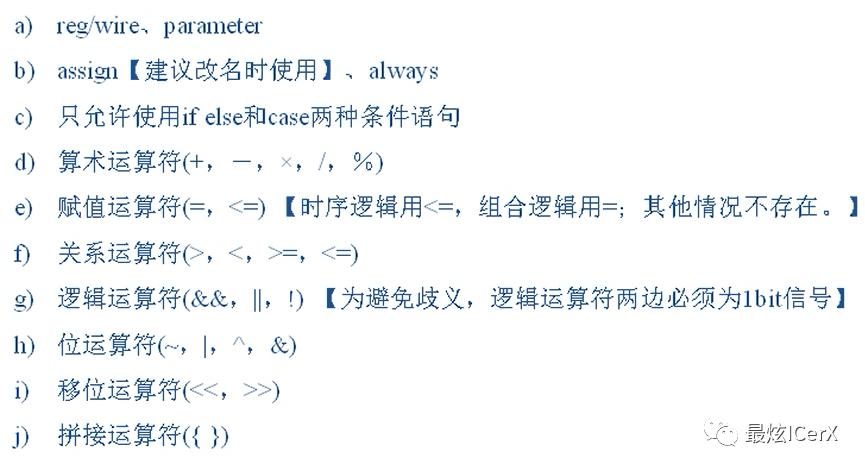

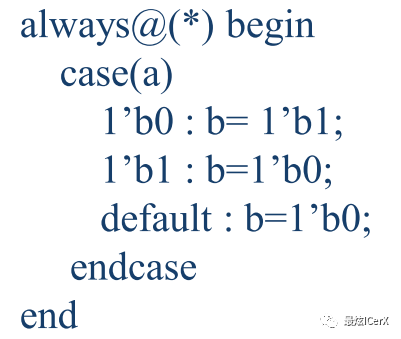

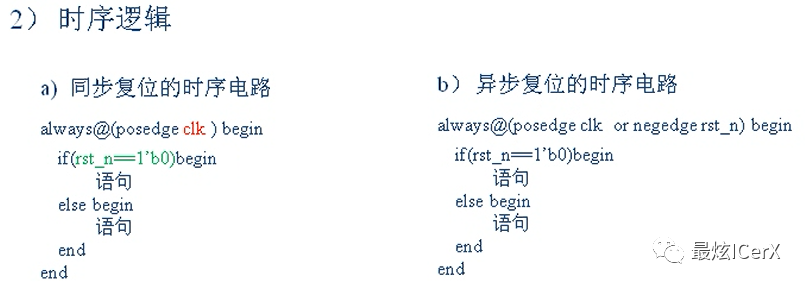

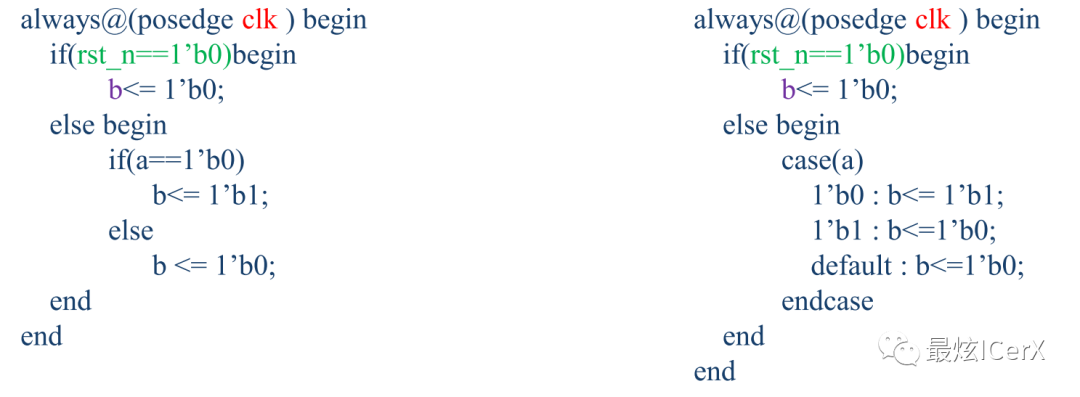

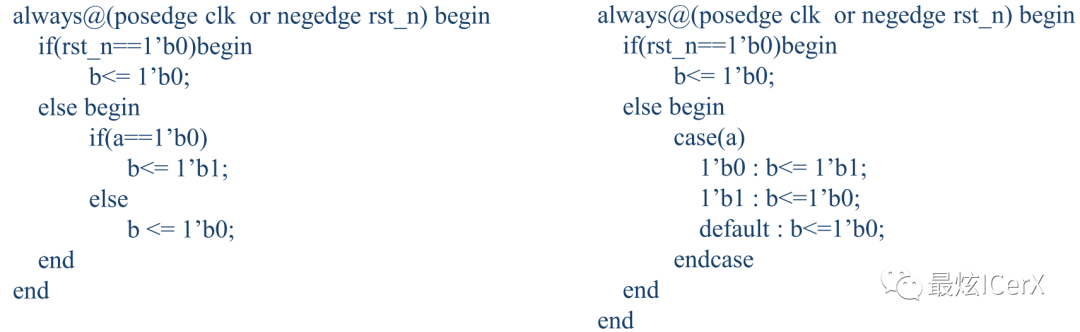

2)設(shè)計(jì)時(shí)使用的語法,主要為下述a,b,c三類

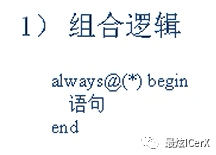

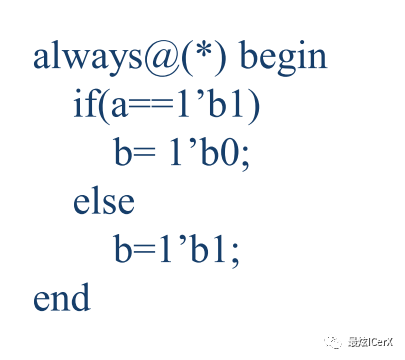

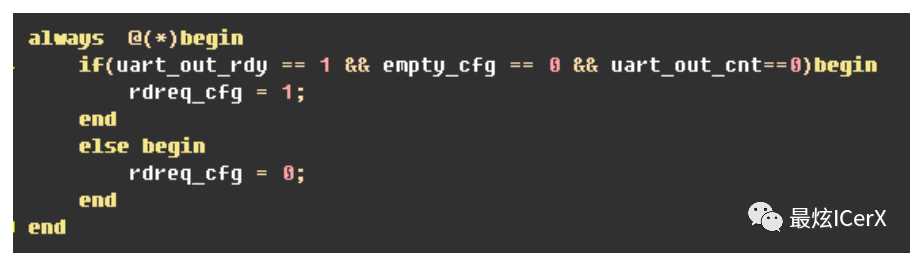

3)電路設(shè)計(jì)結(jié)構(gòu),主要有以下三種

??

4)電路設(shè)計(jì)要點(diǎn)

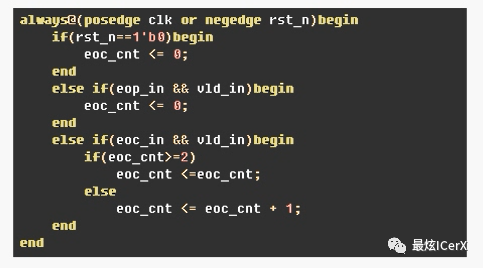

[1]?一個(gè)always只產(chǎn)生一個(gè)信號(hào)

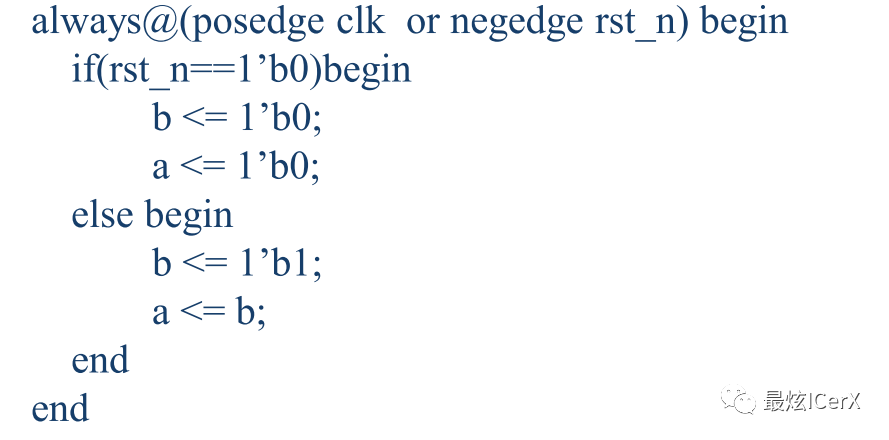

下述不合適

改為下述,只考慮一個(gè)信號(hào),調(diào)試,分析,代碼修改很方便,不需要考慮很多

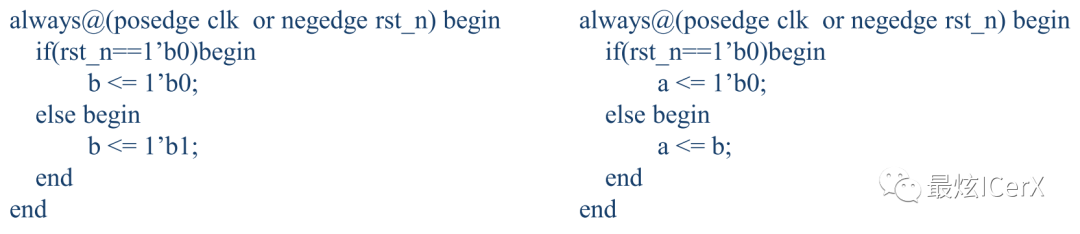

[2]?一個(gè)信號(hào)只在一個(gè)always中產(chǎn)生

下述不符合要求,在多個(gè)always中產(chǎn)生

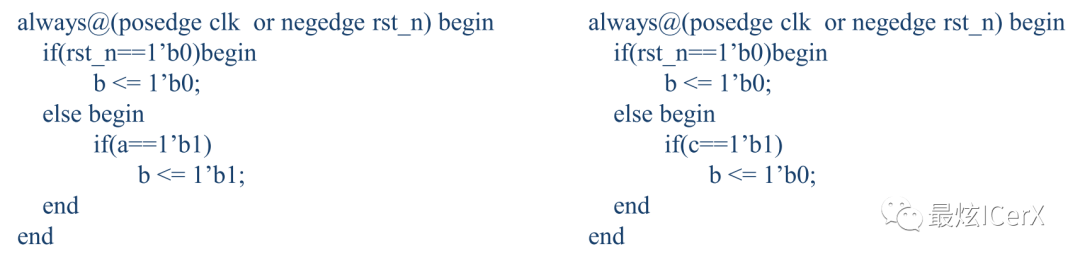

[3]?always是描述一個(gè)信號(hào)產(chǎn)生的方法,即在什么情況下,信號(hào)值為多少,其它情況下,值又為多少,情況要全部考慮

[4] 條件判斷只允許使用if else和case,其它的不使用(包括casex);

[5] 含有posedge或negedge的,一定是D觸發(fā)器,是時(shí)序電路

[6] 想立即有結(jié)果用組合邏輯,延遲一拍有結(jié)果用時(shí)序邏輯

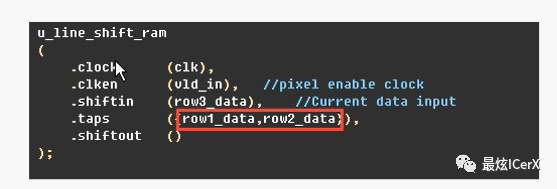

2、模塊例化

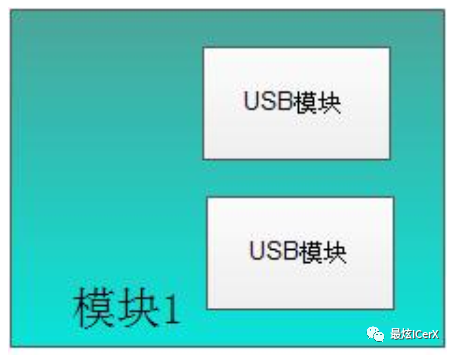

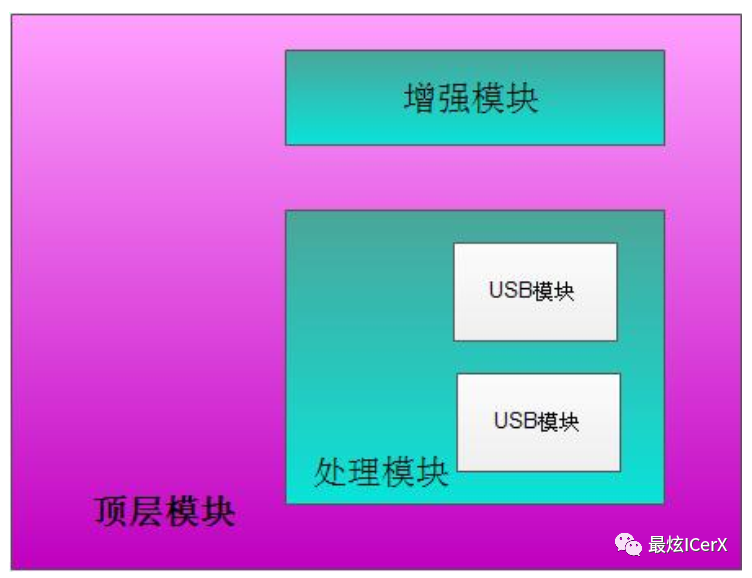

1)什么是例化,簡單到復(fù)雜

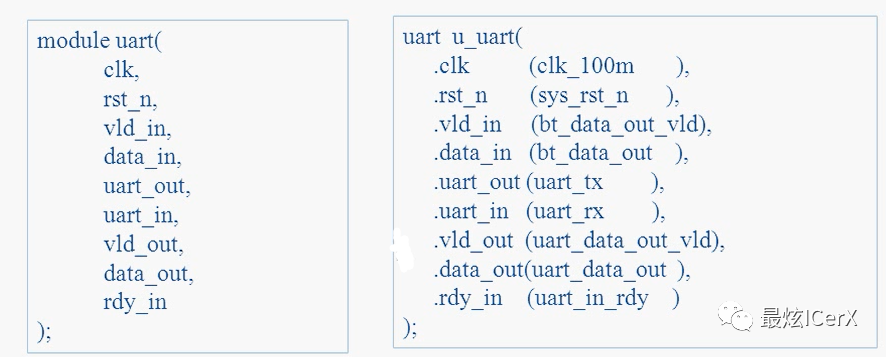

2)例化方法

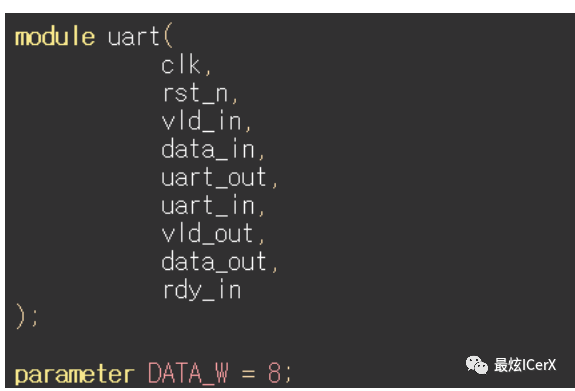

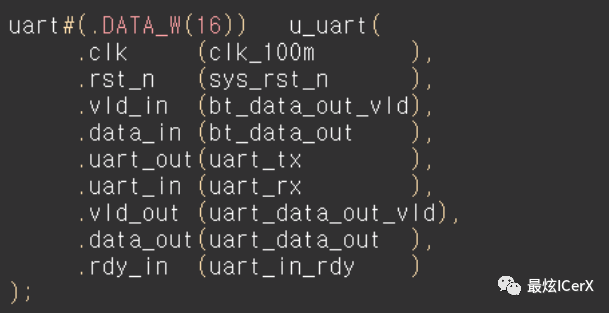

3)參數(shù)例化

? ??

3、運(yùn)算符

1)信號(hào)類型reg/wire

(1)設(shè)計(jì)代碼僅用reg,wire兩種類型

(2)設(shè)計(jì)代碼中,由本模塊且是always產(chǎn)生的信號(hào),為reg類型?

(3)測試代碼中,用initial產(chǎn)生的對測試模塊的輸入信號(hào),用reg類型

(4)其它情況都用wire

(5)reg類型的信號(hào),不一定產(chǎn)生寄存器

2)參數(shù)parameter

(1)將整個(gè)模塊中的CNT_C_W替換成12

(2)參數(shù)名用大寫

3)算術(shù)運(yùn)算符(+,-,*,/,%)

(1)+,-,*用的多,/,%少用,消耗資源多,用的少

4)賦值運(yùn)算符(=,<=),注:時(shí)序邏輯用<=,組合邏輯用=,其它情況不存在

(1)時(shí)序邏輯用<=

(2)組合邏輯用=

5)關(guān)系運(yùn)算符(>,<,>=,<=)

6)邏輯運(yùn)算符(&&,||,!)

(1)一般兩邊都是1bit信號(hào),多Bit也可以

(2)一般用于條件判斷

7)位運(yùn)算符(~,|,^,&)

(1)一般用于賦值

8)移位運(yùn)算符(<<,>>)

(1)一般用于乘除運(yùn)算

(2)右移1位表示除2,左移1位表示乘2

9)拼接運(yùn)算符({ })

(1){a[0],b[3:2]}

(2){{3{a[0]}},b[2],a[1]}

4、模塊設(shè)計(jì)模板

1)解析電路功能

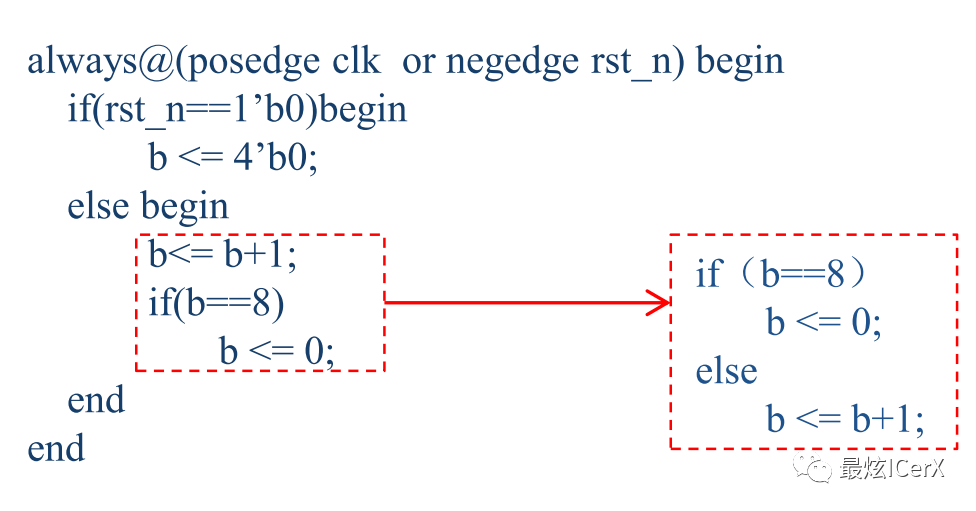

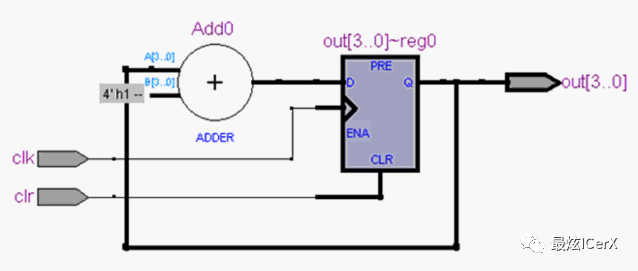

下圖為自加1的電路圖,左邊為組合邏輯,右邊為時(shí)序邏輯

2)修改電路設(shè)計(jì)模塊

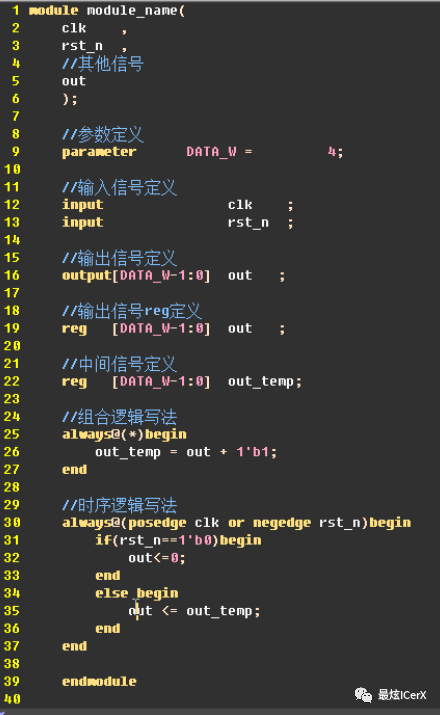

verilog模板

規(guī)則:輸出信號(hào)必須打一拍送出去,所以會(huì)在always中賦值,所以輸出信號(hào)定義為reg類型

先定義,位寬參數(shù),輸入,輸出,中間信號(hào),編寫組合邏輯,時(shí)序邏輯代碼,下述為上圖加法器代碼

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論