幾十年來,一種結構層次結構一直是處理芯片設計復雜性的主要手段。它并不總是完美的,也沒有理想的方法來分而治之,因為這需要專注于正在執行的分析。事實上,大多數系統都可以從各種不同的層次結構中查看,同樣正確,并共同形成一個異層次結構。

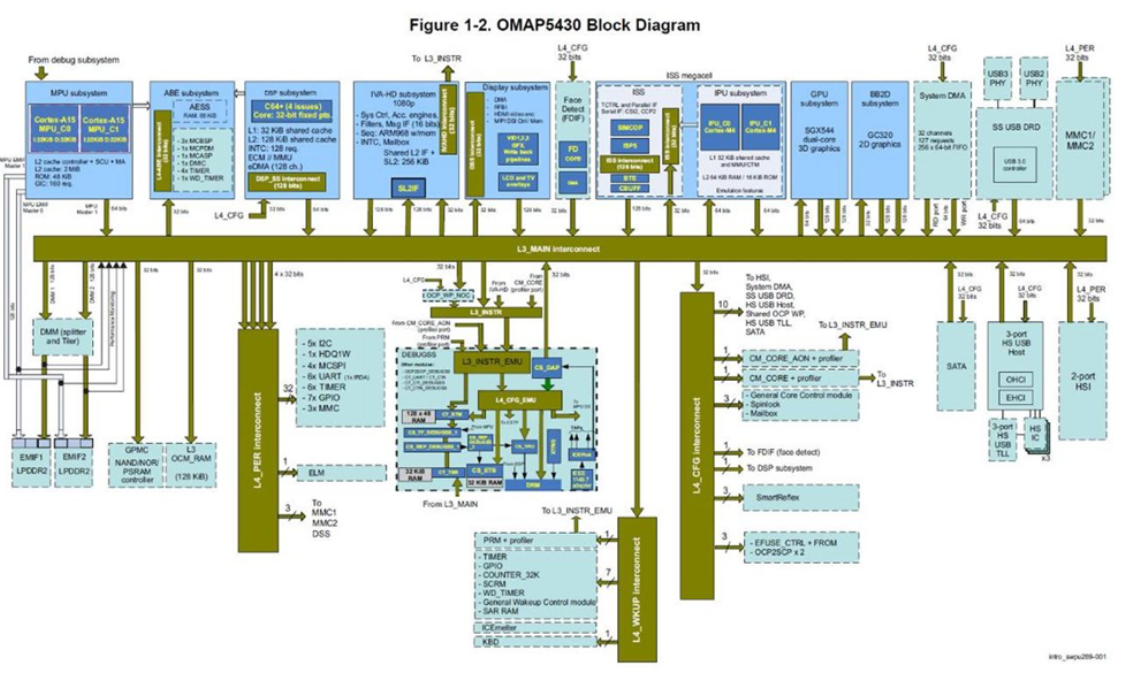

考慮當今使用的層次結構形式的最簡單方法是要求工程師從概念上設計一個系統。他們可能會開始繪制一個包含大塊的框圖,其中包含 CPU、編碼器、顯示子系統等標簽。這不是一個功能層次結構,盡管許多劃分的塊被認為是提供功能的。這也不是純粹的結構分解,因為在芯片中,一切都變成了晶體管的無定形海洋。

該圖大致遵循為印刷電路板設計開發的層次結構,即引腳層次結構。在最低級別,您可能使用了邏輯庫,例如德州儀器 (TI) 7400 系列。這些設備有引腳映射。層次結構的下一個級別是電路板級別,以及連接到背板的引腳。兩者之間幾乎沒有任何層次結構,原理圖只是分布在多個“圖紙”上。后來,當系統變得更加復雜時,也支持結構層次結構。

圖1:2013年左右復雜芯片的典型框圖。來源:德州儀器

這種形式的層次結構提供了一種封裝,允許每個塊的開發在某種程度上變得孤立,并將相互依賴性最小化。頂層成為這些塊相互連接的方式。然后,每個分割的塊都可以經歷類似的分解。

使用層次結構的原因有很多。“容量是其中之一,”Ansys產品營銷總監Marc Swinnen說。“問題變得太大了,你必須把它分解成碎片。另一個是并行工程。你有多個團隊想要同時進行設計,所以你把它分解并分別處理零件。三是重用。您希望重用其他人設計的塊。其中一種微妙的形式是標準單元庫,它本身就是一種層次結構形式。第四個原因是數據量的可管理性。第五個原因是重復的結構,比如內存、多核,你只是自然地重用。第六個原因是混合域,例如模擬/數字,每個塊中都有不同的設計風格。你將使用不同的工具,所以你把它們分層分解。

容量

隨著設計規模越來越大,許多算法需要越來越多的時間才能運行。分解它們可以縮短執行時間并減少所需的資源。Synopsys數字實現小組高級產品經理Jim Schultz表示:“對于大型設計,當您進入物理實現階段時,這些非常大的設計可能需要數天甚至數周的時間才能完成。“如果你把事情搞砸了,成本可能會很高。等級制度是一種分而治之的方式。它讓我們知道我們可以一次關閉設計的一個部分。隨著我們不斷增加功能,芯片越來越大,這不僅與運行時有關,還與資源耗盡有關——放置所有這些可重用實例所需的內存量超過了容量。

為了能夠進行分層分析,必須確保為每個塊正確設置了邊界條件。然后,您需要在頂層跨邊界進行分析。

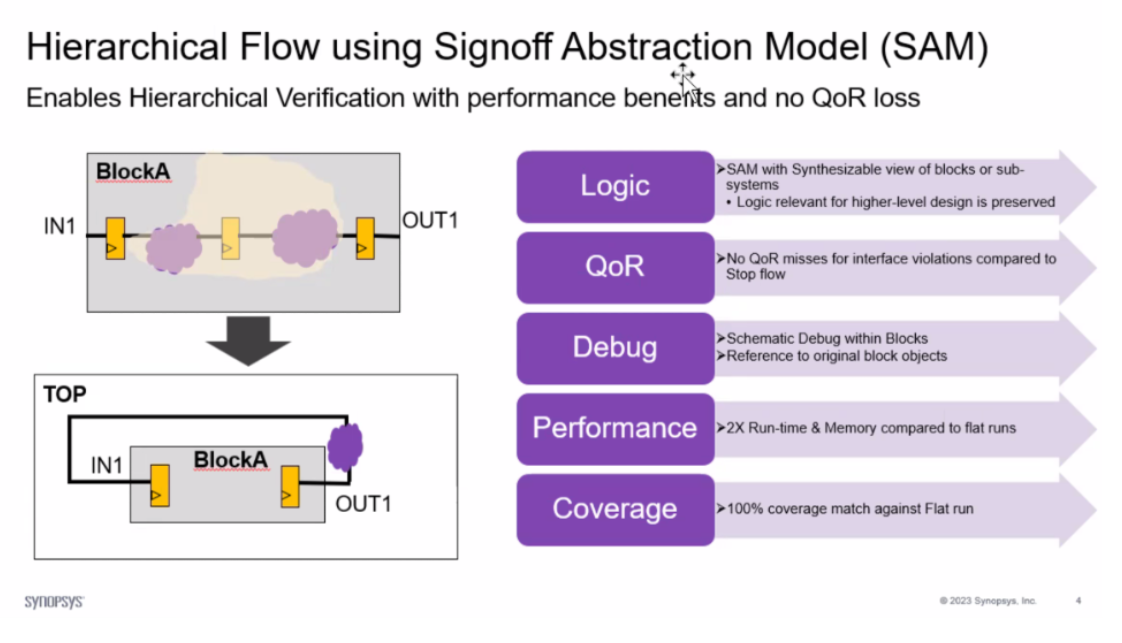

“平面分析需要花費大量時間,但可以提供完全的準確性,”Synopsys 產品經理 Rimpy Chugh 說。“在層次結構中采用黑盒方法可以提高速度,但會失去準確性。這需要一種專門的解決方案(見圖2),其中可以保留模塊的接口邏輯,從而同時獲得速度和準確性的好處。可以在 IP 級別生成抽象模型,然后在 SoC 級別使用它。

圖 2:使用抽象模型的分層流程。來源:Synopsys

并行工程

設計團隊不再局限于一棟建筑。“許多設計正在被劃分,以便一個團隊在一個層次結構上工作,另一個團隊在另一個層次結構上工作,它們可能在同一棟建筑中,也可能分布在世界各地,”是德科技 EDA 數據和 IP 管理產品管理總監 Simon Rance 說。“這可能會帶來挑戰,因為團隊現在的工作速度不同。擁有穩定的層次結構變得很重要,因為以后很難進行更改。這通常只是作為最后的手段發生,但相反,我們看到團隊粘合或捏造以使其發揮作用。它可能很丑陋,但我們在小芯片上看到了更多的挑戰。

重用

層次結構需要以自上而下和自下而上的方式發揮作用。“在人體中,專門的細胞組織成系統和器官,這些系統和器官構成了構成人的基石,”Cadence 高級產品營銷經理 Brian LaBorde 說。“同樣,晶體管組形成電路或邏輯門,這些電路或邏輯門構成組裝成系統的宏。在過去的幾十年里,我們看到越來越大的IC,有許多不同的專用電路,都集成在一個芯片上。這些布局的分區是虛擬的,由布局數據庫中的層次結構表示。

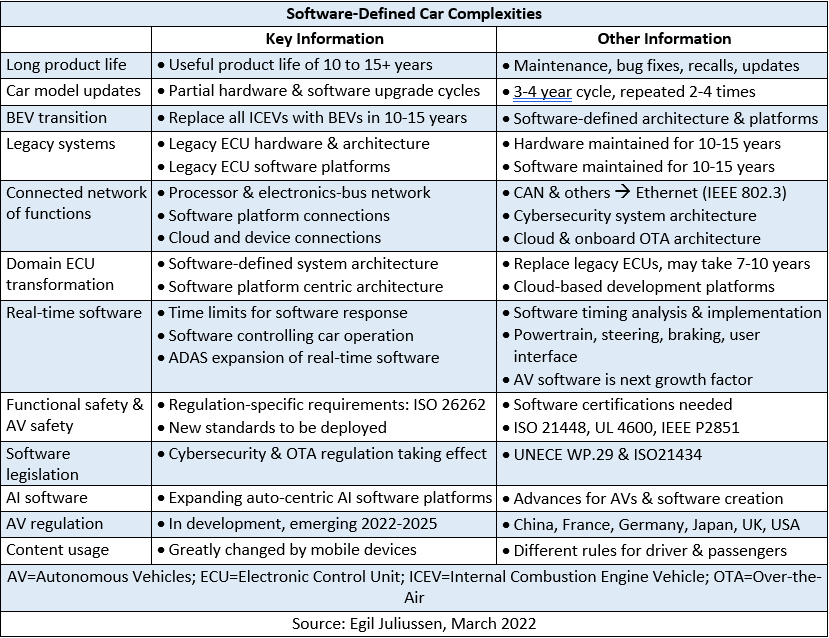

數據管理 所有設計都會產生大量數據,并且必須對其進行管理

。是德科技的 Rance 表示:“無論是針對汽車的 ISO 26262 標準,還是針對軍用航空航天的 MIL882 標準,工程生命周期管理都需要滿足功能安全標準,因此您擁有許多資產,從文檔到驗證、測試標準、驗證測試計劃和結果。“所有這些都需要保留在層次結構中,以便具有完全的可追溯性。無論如何,跟蹤層次結構中的所有內容是很困難的,但您也獲得了設計之外的所有內容,例如驗證和測試計劃。當某些東西在測試中失敗,甚至在現場更糟時,你回去做發現,找出可能失敗的東西。如果你沒有將所有這些數據和元數據附加到層次結構中,你就永遠找不到它。

重復結構 許多設計都包含重復結構

,無論是存儲單元、小型處理器陣列還是接口。但這些陣列中隱藏著危險。“假設你有16個CPU內核排列在一個4X4網格中,”Ansys的Swinnen說。“原則上,這些都是相同的,但實際上它們具有不同的邊界條件。每個邊緣周圍的環境都不同。如果要進行優化,則需要對每個進行單調,因為它們在邊界處都有獨特的寄生效應。總是有這種權衡。你如何保持可重用性,同時找到那些獨特的?當你看到像熱這樣的事情時,情況會變得更糟。

多域 雖然模擬和數字有很大不同,但開發流程的其他方面也利用了工具的分離。“EDA的整個想法是把這個復雜的問題,簡化成一個結構性問題,把它切開,讓問題變得非常簡單,”Siemens Digital Industries Software的技術支持總監Ron Press說。“這就是掃描對DFT的作用。過去,即使他們有單獨的內核,他們也試圖在一個大的平面圖像中完成所有事情。然后你必須等到設計的后期,你就會遇到一個更大的問題。現在,隨著分布式設計團隊和內核的重用,人們需要盡可能多的即插即用。他們將完成DFT的設計,為該內核制作圖案,然后將其插入頂層。只要它有某種類型的隔離,例如包裝鏈,他們就可以單獨處理該部分,完成 DFT 設計,并完成他們的圖案。這使得這些團隊變得獨立,并使整個過程變得更加容易。

結構層次結構的問題

沒有一個系統是完美的,這種形式的層次結構確實會產生一些問題。“在這些邊界處設計約束肯定會產生開銷,”Synopsys 的 Schultz 說。“你必須分解約束并正確定義它們,并將它們向下推到塊邊界。確保正確定義這些邊界是一個大問題。另一個反對它的因素是,在設計上,當你把一些東西分解成碎片,你說這些是我的分區,當我去物理實現它時,我不會跨這個邊界進行優化。你無法優化——這個邊界現在是固定的。如果需要在該層次結構中進行優化,則無法進行。你自己是有限的。

這可能會影響多個工具和流程。“如果他們使用分層DFT進行頂層計劃,他們可能會計劃將如此多的引腳連接到內核,”西門子出版社說,“然后事實證明,內核不需要太多的模式,而他們為其分配了類似數量的引腳的另一個內核需要更多的模式。如果他們很早就從頂層開始凍結了他們的設計,那么他們的模式交付就不會那么有效。

建立錯誤的層次結構可能會以多種方式限制您。Schultz補充道:“其中一個大問題,尤其是對于大型SoC而言,網絡和通信會造成擁塞。“我們看到整個芯片出現擁塞,尤其是當設計分區不佳時。我看到塊通過其他塊進行通信,您必須創建饋通。這可能會導致設計出現大量擁塞。此外,當你做這樣的事情時,要滿足你的時序要求要困難得多,因為你無法輕松優化完整的路徑。你必須單獨優化每個區塊,并希望路徑都成功。

邊界處可能會發生微妙的變化。“當你毗鄰兩個街區時,它們之間有一種邏輯上的聯系,但那里沒有物理上的東西,”Swinnen說。“針腳只是相互接觸,但沒有電線。但是在你的網表中,你有一根應該在那里的電線。它應該有一個電阻,一個電容。您有邏輯線路,但沒有物理線路。然后是饋通,電線進入塊的一側,穿過塊,然后從另一端出來。有引腳,有物理線,但沒有邏輯線。從邏輯上講,它不存在。你不會在原理圖上畫出來。

有些工具可以處理糟糕的層次結構,但修復它們會產生其他問題。Schultz 說:“當你開發 RTL 并綜合它時,你有一個邏輯層次結構。“當你進行物理設計時,這些邏輯層次結構必須一對一地映射到物理分區。最終發生的事情是,在我的邏輯層次結構中,我可能有一個孩子在與該邏輯層次結構下的孩子交談,而這個邏輯層次結構實際上正在與另一個父母之下的東西交談很多,而這兩個父母成為他們自己的物理分區。這兩個父母可以物理地放置在芯片的兩側。邏輯層次結構不利于物理實現。處理這個問題的方式是通過 RTL 重組。現在我們開始移動東西并修復邏輯,但這不是純粹的 RTL 或邏輯設計者會知道的事情。只有當您考慮到物理層次結構時,才會出現該信息。兩者之間需要有溝通,才能真正優化物理層次結構。

這發生在流中的其他位置。“NoC 位于最高駕駛艙層,您可以在其中擁有完整層次結構的集成方面,”Arteris 解決方案和業務開發副總裁 Frank Schirrmeister 說。“當需要對層次結構進行更改時,可能是因為電源域之間存在兩種不同的非功能性屬性,重構 RTL 可能很簡單。對層次結構進行更高級別的集成有助于您相應地重構和重構 RTL,而您真的不想通過手動更改所有模塊來做到這一點。

跟蹤這一點可能是一場噩夢。“想想對屬于層次結構的文檔或文件的修訂控制,”Rance 說。“然后,你可能會有該層次結構的多個版本或修訂版,這取決于你在做什么。您可能有一個進行 PPA 分析的驗證團隊,并發現如果他們稍微調整一下并創建此層次結構的另一個版本,它的性能會更好。你需要跟蹤這一點。

盡管等級制度有助于我們分而治之,但有些事情卻無視任何簡化這些嘗試。“像熱分析這樣的事情需要在整個芯片范圍內完成,”Arteris 的 Schirrmeister 說。“但你需要能夠將其與芯片中發生的事情在功能上聯系起來,與通過它運行的數據相關聯。您希望能夠拍攝芯片照片,從生命周期的角度來看,您可以查看熱點以及每個功能的位置,并且受到的影響最大。將其與數據相關聯絕非易事。

其他層次結構

其他層次結構確實存在,例如功能層次結構。我們今天最接近這一點的是一個需求跟蹤系統,它從系統應該做什么的高級定義開始。這些任務被分解為越來越簡單的任務,直到最終確定實際提供它的邏輯或其他電路,以及驗證是否滿足適當要求的測試平臺。

一些層次結構在設計過程中來來去去。“你可能有一個時鐘樹的層次結構,”Schirrmeister說。“配電系統有層次結構。然后,系統分析工具可以看到一個層次結構,用于它們如何將所有東西連接在一起,以獲得完整的芯片視角。我們對ESL(電子系統級)的思考,是描述整個事情的可執行功能規范的概念。這是尚未出現的東西。不知何故,我們似乎僥幸逃脫了,這令人驚訝。

物理布局提供了另一個層次結構。最高層次是樓層規劃,它利用結構層次結構作為起點。放置這些塊,并在它們之間布線互連。每個模塊都使用物理綜合進行布局,這再次處理本地互連。3D-IC將為此增加一個新的維度,現在可能在Z方向上存在布線。

Cadence 的 LaBorde 表示:“隨著我們開始看到基于小芯片的 2.5D 和 3D 系統取代片上系統 (SoC) 設計,層次結構將不再像物理現實的表示那樣具有戰略意義。“原理圖中的宏可能代表系統中的芯片,每個芯片都有自己獨特的工藝。它們之間的連接將是焊點,而不是布局上的象征性引腳。

結論

雖然并不完美,但今天使用的非正式結構分解已被證明是一種熟練的層次結構。流程的某些方面因此而受到影響,但大多數方面都能夠有效地使用它,并且工具可以彌補其不足。雖然有一定程度的優化潛力因此而喪失,但這可能是以生產力的名義做出的小犧牲之一。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論