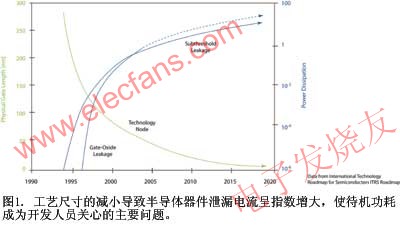

半導(dǎo)體工業(yè)的最主要特征是工藝不斷進步,平均每隔幾年就要升級一次,帶動功耗和成本不斷下降,性能不斷提升。從180nm到130nm,再到90nm、65nm和45nm,這些略顯枯燥的數(shù)字使我們的生活正在加速進入充斥各種電子器件的數(shù)字時代。

在新的工藝節(jié)點上,當(dāng)可編程邏輯,邏輯器件,也就是CPLD和FPGA廠商一次又一次在不久的將來65nm領(lǐng)域把電子設(shè)計行業(yè)專家和電子社群共同推出的榮譽帶回他們的總部的時候,我們不得不再次思索65nm究竟給這個行業(yè)帶來的是什么樣的變化,可編程邏輯解決方案為什么從以前的配角不斷地成為行業(yè)的熱點。

眾所周知,通信、儀器、工業(yè)、軍工、航天等許多市場具有小批量、多品種的特點,如果投入大量資源開發(fā)一顆專用的芯片,經(jīng)濟上是非常不劃算的。另外,越來越多的企業(yè)意識到差異化的快速靈活生產(chǎn)才是生存和發(fā)展之道,但卻是高昂的芯片設(shè)計和制造成本卻阻礙了技術(shù)的創(chuàng)新。還好有FPGA,工程師可以用FPGA實現(xiàn)所需的功能和算法,這樣他們就不必受限于某種產(chǎn)品或某家廠商,而僅僅受限于他們的創(chuàng)造性思維。

FPGA要與其它類型的器件競爭,必須滿足低成本、低功耗、高性能的要求,采用先進工藝是最直接有效的辦法了。同時,由于FPGA芯片是一次研發(fā)投入,就可以用軟件編程的方式反復(fù)利用,讓眾多的客戶來分擔(dān)研發(fā)成本。因而FPGA廠商在采用先進工藝上可謂不遺余力。從130nm、90nm到65nm,每一次新的工藝制程的推進,都離不開他們的身影。

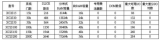

比如賽靈思的65nmVirtex-5,作為可編程領(lǐng)域最早推出且是目前唯一量產(chǎn)的65nm器件,就很具有相當(dāng)?shù)拇硇浴?宣稱“Innovation in the Heart”的賽靈思在新的65nmVirtex-5上, 采用了先進的3層不同厚度的氧化層技術(shù)降低漏電和靜電,通過1.0V的內(nèi)核電壓和應(yīng)變硅技術(shù)實現(xiàn)了更低的動態(tài)功耗并提升性能,用12層銅技術(shù)降低電容電壓以及鎳硅化物自動對準(zhǔn)技術(shù)提升性能等。此外,Virtex-5還采用ASMBL架構(gòu)和Express Fabric,并內(nèi)置了溫度與電壓傳感器等技術(shù),與前代90nm FPGA相比,速度平均提高30%,容量增加65%,動態(tài)功耗降低35%,靜態(tài)功耗不變,芯片面積減小了45%。Virtex-5具有6個獨立輸入的查找表(LUT)和新型對角互連結(jié)構(gòu),減少了邏輯層次,改進了構(gòu)造塊之間的信號互連,使邏輯性能比上一代Virtex-4平均提高30%。賽靈思亞太區(qū)Virtex解決方案高級市場經(jīng)理鄒志雄透露,65nm Virtex的價格有望比90nm器件下降20%~30%。

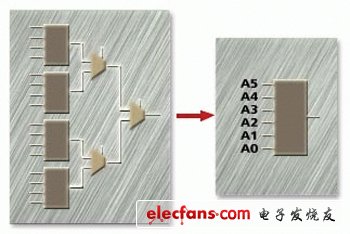

利用ExpressFabric架構(gòu)的6輸入查找表,實現(xiàn)64位分布式RAM時,只需用一個邏輯單元,而以往的4輸入查找表則需要4個邏輯單元。

系統(tǒng)設(shè)計師當(dāng)然喜歡高性能,可絕對討厭高功耗,如何在降低功耗的同時不犧牲速度和性能也是很大的挑戰(zhàn)。廠商為降低功耗,通常會采用較低的內(nèi)核電壓,但內(nèi)核電壓下降會犧牲速度,如內(nèi)核電壓從1.1V下降到0.9V,速度將會降低17%。鄒志雄解釋道,Virtex-5通過擴大硅分子間距,在采用1.0V電壓時并沒有增加漏電流,也沒有犧牲速度與性能,在性能和功耗之間取得了很好的平衡。

高速信號處理與串行傳輸

手機是數(shù)字式的,家電是智能的,高清電視可以掛墻上了,我們身邊可以找到的純模擬信號的產(chǎn)品日漸稀少,所有的產(chǎn)品一定要粘上數(shù)字兩個字才夠時髦。數(shù)字世界的核心要義是實現(xiàn)數(shù)字信號的處理,包括變換、濾波、編解碼等操作,可以用MCU、DSP、FPGA、硬連線邏輯等多種方式來實現(xiàn)。硬連線邏輯的處理效率最好,但靈活性最差,開發(fā)十分復(fù)雜,只能適應(yīng)一種媒體格式和固定的操作,無法滿足支持多種媒體格式的要求,基本上已被淘汰。MCU的強項是控制,對數(shù)字信號處理的能力有限,對數(shù)據(jù)量有限的應(yīng)用還可以應(yīng)付。從名字上就可以知道,DSP最適合數(shù)字信號處理,如語音、視頻、圖像,而且DSP的架構(gòu)相對精簡,易于提高時鐘頻率。DSP的性能受很多固定硬件架構(gòu)的限制,如總線性能瓶頸、固定數(shù)量的乘法累加(MAC)模塊、固定存儲器、固定硬件加速模塊和固定數(shù)據(jù)帶寬等。因此DSP的這種固定硬件架構(gòu)對于許多要求定制DSP功能實現(xiàn)的應(yīng)用來說并不適用。FPGA最大的優(yōu)勢是并行處理,在同一時間能處理大量不同的任務(wù),因而在涉及到復(fù)雜計算時可把DSP的一些任務(wù)卸載到FPGA中處理。

隨著電信網(wǎng)、廣播電視網(wǎng)和計算機通信網(wǎng)的相互滲透、互相兼容,并逐步整合成為統(tǒng)一的信息通信網(wǎng)絡(luò),對計算處理能力的要求越來越高,這時僅靠DSP又難以承擔(dān),常采用DSP+FPGA的方式實現(xiàn)系統(tǒng)邏輯復(fù)用及合并、實現(xiàn)新外設(shè)或總線接口以及信號處理鏈中的性能加速。

FPGA本身的處理性能在不斷提高,在很多應(yīng)用中大有取代DSP之勢,尤其是在一些標(biāo)準(zhǔn)不斷演進的通信系統(tǒng)中。FPGA可配置DSP片段來實現(xiàn)復(fù)用器、計數(shù)器、乘法累加器、加法器和很多其它功能,這些都不需要占用邏輯結(jié)構(gòu)資源。FPGA還具有高的片上存儲器帶寬、大量I/O帶寬以及高度的靈活性,可以在更低的功耗下提供高性能的可編程DSP功能,同時還能降低系統(tǒng)成本和減小電路板面積。系統(tǒng)設(shè)計師可以用一片或幾片F(xiàn)PGA開發(fā)出一塊原本要數(shù)十塊DSP和可能多塊電路板才能實現(xiàn)的電路板。因為FPGA支持在相同封裝內(nèi)的縱向移植,因此只需要更換不同規(guī)格的器件,就可以在同一個電路板設(shè)計上實現(xiàn)從低端到高端的功能。特別是對那些處理高速數(shù)據(jù)的多通道應(yīng)用,F(xiàn)PGA可實現(xiàn)每時鐘周期數(shù)百浮點乘法,這比最快的DSP快數(shù)倍。

以Virtex-5 SXT FPGA為例,該器件增強的DSP邏輯片(DSP48E)包括一個25x18位乘法器、一個48位第二級累加和算法運算單元以及一個可擴展到96位的48位輸出。更寬的數(shù)據(jù)路徑和輸出可支持更廣泛的動態(tài)范圍和更高的精度,同時還優(yōu)化了對單精度浮點運算的支持,而所消耗的資源只有90nm FPGA的一半。DSP48E邏輯片還包括了集成的層級路由,支持550MHz全速下的并行處理,利用640個DSP48E塊可提供352GMAC的處理能力。其它功能還包括一個獨立的C寄存器和一個擴展的第二級,這個第二級支持SIMD運算和模式檢測,能夠更高效地完成DSP實現(xiàn)。Virtex-5的DSP48E邏輯片可實現(xiàn)各種加速算法,可實現(xiàn)DSP功能的更高程度的集成,比以前Virtex器件的功耗更低。

FPGA還具有MCU和DSP所不具有的特性,那就是高速的硬件加密功能。由于FPGA是并行架構(gòu),可以同時對許多位數(shù)據(jù)進行加密。Virtex-5支持AES加密,基于軟件的比特流加密和片上比特流解密邏輯使用了專用存儲器來存儲256位加密鑰。

ML506入門級DSP開發(fā)板

目前電子行業(yè)的一個熱門話題是串行通信,主要是由于串行通信能夠避免并行通信中的信號間串?dāng)_問題,可以實現(xiàn)非常高的通信速率,如SATA 2的傳輸速率高達300MB/s,PCI Express 2.0的速度可達到500MB/s。

65nm的先進工藝使晶體管的開關(guān)速度更快,從而支持更高的傳輸速率。Virtex-5系列中的SXT平臺有16個低功耗3.2Gbps RocketIO串行收發(fā)器,該串行收發(fā)器支持CPRI/OBSAI、HD/SDI、Serial RapidIO、PCI Express以及千兆位以太網(wǎng)等標(biāo)準(zhǔn)協(xié)議。內(nèi)建的協(xié)議模塊和接口直接提供對PCI Express和千兆位以太網(wǎng)的支持。

Virtex-5 LXT FPGA整合了串行收發(fā)器、內(nèi)置式PCI Express端點模塊和以太網(wǎng)媒體訪問控制器模塊,PCI Express端口已通過了PCI SIG V1.1版測試。Virtex-5的收發(fā)器具有先進的發(fā)射和接收均衡性能,還有預(yù)加重、自適應(yīng)抖動等功能,能實現(xiàn)出色的信號完整性,使眼圖的張開度最大化。用戶還可以利用開發(fā)和調(diào)試工具、設(shè)計套件、IP、特性報告等快速構(gòu)建標(biāo)準(zhǔn)兼容型串行接口。

商業(yè)和技術(shù)開發(fā)模式的轉(zhuǎn)變

在2005年90nm工藝大規(guī)模應(yīng)用的時候,有眾多的公司宣布采用90nm工藝量產(chǎn)其產(chǎn)品,這些公司包括Intel、AMD、TI、NXP、Freescale、IBM、ATI、NEC、三星和賽靈思,而現(xiàn)在,僅有Intel、AMD、IBM、三星、Nvidia和賽靈思等幾家公司宣布采用65nm工藝進行量產(chǎn)了。

盡管人們熱衷于談?wù)摴に嚦叽绲膯栴},但實際投產(chǎn)的65nm芯片設(shè)計的數(shù)量遠比想像得少,原因很簡單,不劃算。雖然工藝每升級一次,就能使晶圓的制造成本降低一半,卻會使芯片的開發(fā)成本上升2倍、3倍甚至更多,而且是呈指數(shù)上升的。如65nm芯片的開模費高達400萬美元,而45nm芯片的開模費更會達到900萬美元。相比于開模費,更先進工藝的研發(fā)費用更會高得讓人咋舌,設(shè)計一款45nm的芯片可能要燒掉2~5億美元。別說是ASIC廠商,就是ASSP廠商可能都無力負擔(dān)這筆巨額開支,這也是半導(dǎo)體業(yè)界的聯(lián)合設(shè)計、聯(lián)合研發(fā)日漸增多的緣由。只有那些能在眾多客戶和設(shè)計間分?jǐn)偝杀镜男酒髽I(yè)才能承擔(dān)越來越昂貴的芯片制造和設(shè)計費用。可以預(yù)見的是,未來采用45nm、32nm甚至22nm的廠商名單只會越來越短,最先進工藝的IC設(shè)計只能是少數(shù)大佬們的對手戲了。

而這對FPGA廠商來說則是一種優(yōu)勢。鄒志雄解釋道,可編程器件,由于其工藝特點和商業(yè)模式,實際上是讓眾多的客戶和FPGA廠商一起來承擔(dān)這些巨額的研發(fā)費用。例如賽靈思有2萬多客戶,大家共同分?jǐn)?5nm的2億美元成本,這樣實際上每個公司僅需承擔(dān)1萬美元,無疑就分擔(dān)了風(fēng)險。無晶圓代工模式就是由賽靈思率先發(fā)起的,這種分擔(dān)技術(shù)風(fēng)險的商業(yè)模式使FPGA的發(fā)展前景極為廣闊。

在一些出貨量極大的市場上,65nm的FPGA在成本上與90nm、130nm的ASIC/ASSP芯片并沒有優(yōu)勢。如果FPGA的工藝能進入到32nm以下,老工藝的ASIC/ASSP芯片在成本上就會落得下風(fēng)。再考慮到芯片開發(fā)的風(fēng)險和成本,以及未來市場的不確定性,ASIC/ASSP的設(shè)計會逐漸減少,系統(tǒng)廠商必須求助于FPGA來完成設(shè)計,一些傳統(tǒng)的IC設(shè)計業(yè)也可能讓位基于FPGA的系統(tǒng)設(shè)計。

目前,可編程解決方案供應(yīng)商在積極與代工伙伴一起在研發(fā)45nm的FPGA,32nm和22nm的FPGA也在計劃當(dāng)中。未來的FPGA還可以將閃存、嵌入式處理器等其他器件整合進來,實現(xiàn)混合工藝與混合電壓,讓FPGA變成一塊“虛擬母板”,工程師可以直接進行混合信號的設(shè)計。換句話說,系統(tǒng)廠商不必再等IC供應(yīng)商設(shè)計出所需的芯片,它們完全可以在FPGA上實現(xiàn)完整的系統(tǒng)功能。傳統(tǒng)的電子系統(tǒng)開發(fā)模式在工藝不斷進步的FPGA的力推下可能遭到徹底顛覆。

量產(chǎn)是信心的符號

自2006年5月15日推出65nm Virtex-5 FPGA平臺以來,賽靈思公司已向市場發(fā)售了基于三款平臺(LX、LXT和SXT)的13種器件。其中兩款LX50和LX50T目前可量產(chǎn)供貨,其它型號很快就可進入量產(chǎn)。

在從推出樣片到量產(chǎn)的一年里,賽靈思在高低溫測試、ESD保護以及開發(fā)工具、參考設(shè)計等方面做了大量工作。鄒志雄特別強調(diào):“量產(chǎn)的FPGA意味著客戶現(xiàn)在可以放心地大量采用65nm FPGA進行整機產(chǎn)品制造。嚴(yán)格的內(nèi)部工藝流程控制以及與代工廠合作伙伴的密切協(xié)作,使65nm工藝的良率達到了令人滿意的程度。”為了讓應(yīng)用設(shè)計工程師更方便、快捷地開發(fā)基于Virtex-5的設(shè)計,賽靈思對軟件和整體解決方案進行了多優(yōu)化,提供免費的設(shè)計工具、針對應(yīng)用而優(yōu)化過的協(xié)議開發(fā)套件、通用開發(fā)板以及參考設(shè)計。

此外,賽靈思采用雙代工廠策略以確保供應(yīng)穩(wěn)定性。UMC和東芝均通過了嚴(yán)格的認定流程和NPI(新產(chǎn)品引入)評估。NPI評估包括工藝評估(缺陷密度、線產(chǎn)量、周期以及量產(chǎn)關(guān)鍵要素等)、驗證和特性評估、量產(chǎn)合作認定評估(內(nèi)容部量產(chǎn)合格認定結(jié)果和量產(chǎn)計劃)、封裝/組裝評估、最終測量產(chǎn)量和故障覆蓋評估以及物流和產(chǎn)品計劃評估等,從而為順利量產(chǎn)打下了良好的基礎(chǔ)。雙代工廠的策略也有助于實現(xiàn)產(chǎn)能擴張,在一家代工廠出現(xiàn)產(chǎn)能瓶頸的時候,可以利用另一家代工廠的富裕產(chǎn)能滿足市場的需求。雙代工廠的潛在風(fēng)險是兩家代工廠的工藝不會完全一致,不過這可以通過嚴(yán)格的測試和驗證來解決,保證客戶拿到的最終產(chǎn)品的性能參數(shù)在容差范圍內(nèi)。

“時機即是商機。”在量產(chǎn)時間上已經(jīng)足足領(lǐng)先最接近競爭對手一年半時間的賽靈思公司,正以“獨一無二”的氣勢吸引著致力于差異化和行業(yè)領(lǐng)先地位的高端擁護。 而與此同時,對于采用65nm解決方案的客戶來說,也意味著客戶能有更多的利潤和更大的成功機會。要知道,提前一年搶占市場也許就會使后來者徹底出局。

?

電子發(fā)燒友App

電子發(fā)燒友App

評論