16日,三星電子宣布在基于EUV的高級節點方面取得了重大進展,包括7nm批量生產和6nm客戶流片,以及成功完成5nm FinFET工藝的開發。 三星電子宣布其5納米(nm)FinFET工藝技術的開發

2019-04-18 15:48:47 6010

6010 基于Mentor的PCB工具采用拓樸布線技術

印刷電路板設計解決方案供貨商明導國際(Mentor Graphics),宣布推出一種突破性

2010-04-28 17:49:25 1014

1014 新思科技公司(Synopsys)在過去五年多與行業領導者合作共同開發了對FinFET技術的支持,通過提供經生產驗證的設計工具與IP來推進對FinFET技術的采用。

2013-02-19 10:42:54 823

823 Cadence設計系統公司(Cadence Design Systems, Inc.)(納斯達克代碼:CDNS)今日宣布與TSMC簽訂了一項長期合作協議,共同開發16納米FinFET技術,以其適用于

2013-04-09 11:00:05 798

798 在近期內,從先進的芯片工藝路線圖中看已經相當清楚。芯片會基于今天的FinFET工藝技術或者另一種FD SOI工藝的平面技術,有望可縮小到10nm節點。但是到7nm及以下時,目前的CMOS工藝路線圖已經不十分清晰。大量的金錢和精力都花在探索FinFET工藝,它會持續多久和為什么要替代他們?

2014-02-25 10:16:56 5279

5279 在國際電子電路研討會大會(ISSCC)上,三星展示了采用10納米FinFET工藝技術制造的300mm晶圓,這表明三星10納米FinFET工藝技術最終基本定型。

2015-05-28 10:25:27 1715

1715 在我們大多數人“非黑即白”、“非此即彼”的觀念里,半導體廠商應該不是選擇FinFET就是FD-SOI工藝技術。

2015-07-07 09:52:22 3744

3744 TSMC在FinFET工藝量產上落后于Intel、三星,不過他們在10nm及之后的工藝上很自信,2020年就會量產5nm工藝,還會用上EUV光刻工藝。

2016-07-18 10:47:09 989

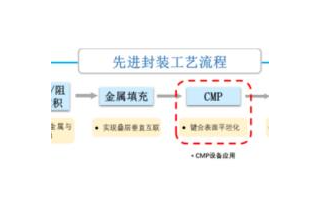

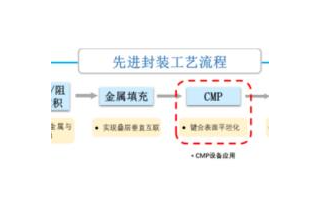

989 在芯片制造制程和工藝演進到一定程度、摩爾定律因沒有合適的拋光工藝無法繼續推進之時,CMP技術應運而生,是集成電路制造過程中實現晶圓表面平坦化的關鍵工藝。傳統的機械拋光和化學拋光去除速率均低至無法滿足

2023-02-03 10:27:05 3660

3660

3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術研討會期間發布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是

2023-05-19 16:25:12 784

784

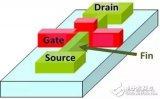

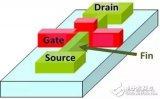

Finfet技術(3D晶體管)詳解

2012-08-19 10:46:17

Mentor面向智能家居的IoT方案

2020-04-20 11:38:20

想問一下,TSMC350nm的工藝庫是不是不太適合做LC-VCO啊,庫里就一個電容能選的,也沒有電感可以選。(因為課程提供的工藝庫就只有這個350nm的,想做LC-VCO感覺又不太適合,好像只能做ring-VCO了)請問350nm有RF工藝嘛,或者您有什么其他的工藝推薦?

2021-06-24 08:06:46

工藝庫TSMC0.18um和TSMC0.18umrf有什么區別呢?求大神解答

2021-06-23 07:33:12

,MediaTek 和德州儀器(TI)創建異構系統體系結構(HSA)基金會并成為創始成員ARM和TSMC合作開發FinFET器件工藝技術,將應用于下一代64位ARM處理器ARM創建首個創建技術藍圖“

2021-07-02 07:58:02

COMS工藝制程技術主要包括了:1.典型工藝技術:①雙極型工藝技術② PMOS工藝技術③NMOS工藝技術④ CMOS工藝技術2.特殊工藝技術。BiCOMS工藝技術,BCD工藝技術,HV-CMOSI藝

2019-03-15 18:09:22

EMC設計、工藝技術基本要點和問題處理流程推薦給大家參考。。

2015-08-25 12:05:04

<br/>? 九. 檢驗工藝<br/>? 十. SMT生產中的靜電防護技術<br/><

2008-09-12 12:43:03

Sic mesfet工藝技術研究與器件研究針對SiC 襯底缺陷密度相對較高的問題,研究了消除或減弱其影響的工藝技術并進行了器件研制。通過優化刻蝕條件獲得了粗糙度為2?07 nm的刻蝕表面;犧牲氧化

2009-10-06 09:48:48

;nbsp; &nbsp;<br/>薛競成----無鉛工藝技術應用和可靠性&nbsp;<br/>主辦單位&

2009-07-27 09:02:35

PCB部件使用PI膜作為柔性芯板,并覆蓋聚酰亞胺或丙烯酸膜。粘合劑使用低流動性預浸料,最后將這些基材層壓在一起以制成剛撓性PCB。剛柔性PCB制造工藝技術的發展趨勢:未來,剛柔結合PCB將朝著超薄,高密度

2019-08-20 16:25:23

業界對哪種半導體工藝最適合某一給定應用存在著廣泛的爭論。雖然某種特殊工藝技術能更好地服務一些應用,但其它工藝技術也有很大的應用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-07-05 08:13:58

業界對哪種半導體工藝最適合某一給定應用存在著廣泛的爭論。雖然某種特殊工藝技術能更好地服務一些應用,但其它工藝技術也有很大的應用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-08-20 08:01:20

工藝技術的演進遵循摩爾定律,這是這些產品得以上市的主要促成因素。對整個行業來說,從基于大體積平面晶體管向FinFET三維晶體管的過渡是一個重要里程碑。這一過渡促使工藝技術經過了幾代的持續演進,并且減小

2019-07-17 06:21:02

如何提高多層板層壓品質在工藝技術

2021-04-25 09:08:11

的工藝技術可用于晶圓凸起,每種技術有各自的優缺點。其中金線柱焊接凸點和電解或化學鍍金焊接凸點主要用于引腳數較少的封裝應用領域包括玻璃覆晶封裝、軟膜覆晶封裝和RF模塊。由于這類技術材料成本高、工序

2011-12-01 14:33:02

求TSMC90nm的工藝庫,請問可以分享一下嗎?

2021-06-22 06:21:52

請詳細敘述腐蝕工藝工段的工藝流程以及整個前道的工藝技術

2011-04-13 18:34:13

再流焊工藝技術研究(SMT工藝):隨著表面貼裝技術的發展,再流焊越來越受到人們的重視。本文介紹了再流焊接的一般技術要求,并給出了典型溫度曲線以及溫度曲線上主要控制點

2009-03-25 14:44:33 30

30 和艦科技自主創新研發的0.16 微米硅片制造工藝技術在原有比較成熟的0.18 微米工藝技術基礎上,將半導體器件及相關繞線尺寸進行10%微縮(實際尺寸為0.162 微米),大大降低了芯

2009-12-14 11:23:36 25

25 Mentor Graphics 公司線纜線束設計解決方案CHS明導(上海)電子科技有限公司供稿CHS(Capital Harness System)是國際著名EDA 廠商Mentor Graphics 公司專為航空、航天、車輛等領域開發

2009-12-21 10:12:24 0

0 常用PCB工藝技術參數.

2010-07-15 16:03:17 66

66 無鉛波峰焊接工藝技術與設備1.無鉛焊接技術的發展趨勢

2006-04-16 21:37:53 669

669 IC工藝技術問題 集成電路芯片偏置和驅動的電源電壓Vcc是選擇IC時要注意的重要問題。從IC電源管腳吸納的電流主要取決于該電壓值以及該IC芯片輸出級

2009-08-27 23:13:38 780

780 高通攜手TSMC,繼續28納米工藝上合作

高通公司(Qualcomm Incorporated)與其專業集成電路制造服務伙伴-TSMC前不久日共同宣布,雙方正在28納米工藝技術進行密切合作。此

2010-01-13 08:59:23 910

910 什么是CPU的生產工藝技術/向下兼容?

CPU的生產工藝技術 我們常可以在CPU性能列表上看到“工藝技術”一項,其中有“

2010-02-04 10:41:53 742

742 超細線蝕刻工藝技術介紹

目前,集成度呈越來越高的趨勢,許多公司紛紛開始SOC技術,但SOC并不能解決所有系統集成的問題,因

2010-03-30 16:43:08 1181

1181 采用SiGe:C BiCMOS工藝技術的射頻/微波產品

恩智浦將在2010年底前推出超過50種采用SiGe:C技術的產品,其QUBiC4 SiGe:C工藝技術可提供高功率增益和優

2010-05-24 11:06:35 1367

1367 參考流程 8.0 版(Reference Flow 8.0)提供高級DFM 性能WILSONVILLE, Ore. and HSINCHU, Taiwan – 2007 年6 月5 日 –明導公司 (Mentor Graphics 納斯達克代號: MENT) 與臺灣半導體制造

2010-06-20 11:14:03 1112

1112 對3D封裝技術結構特點、主流多層基板技術分類及其常見鍵合技術的發展作了論述,對過去幾年國際上硅通孔( TSV)技術發展動態給與了重點的關注。尤其就硅通孔關鍵工藝技術如硅片減薄

2011-12-07 11:00:52 149

149 隨著芯片微縮,開發先進工藝技術的成本也越來越高。TSMC對外發言人孫又文表示,臺積電會繼續先進工藝技術節點的投入和開發,今年年底臺積電將推出20nm工藝

2012-08-30 14:34:30 1782

1782 Mentor Graphics公司日前宣布Calibre LFD(光刻友好設計)光刻檢查工具已獲得TSMC的20nm IC制造工藝認證。 Calibre LFD可對熱點進行識別,還可對設計工藝空間是否充足進行檢查。光學臨近校正法

2012-09-29 10:30:46 1761

1761 電子發燒友網核心提示 :Mentor Graphics公司日前宣布Calibre LFD(光刻友好設計)光刻檢查工具已獲得TSMC的20nm IC制造工藝認證。 Calibre LFD可對熱點進行識別,還可對設計工藝空間是否充足進

2012-10-08 16:00:14 915

915 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 909

909 本文重點描述運用MEMS微機械加工工藝技術設計、加工、生產胎壓傳感器IC芯片,希望對大家學習MEMS有所幫助

2012-12-11 14:17:26 7238

7238 臺灣半導體制造公司(TSMC)將為蘋果提供AP/ GPU集成的解決方案,并且采用20nm Soc片上系統工藝為蘋果代工。

2013-01-17 20:58:17 1257

1257 新思科技提供其基于FinFET技術的半導體設計綜合解決方案。

2013-02-18 13:20:08 1149

1149 FinFET制程的設計規則手冊(DRM)第0.5版的認證,同時從即刻起可以提供一套TSMC 16-nm可互通制程設計套件(iPDK)。憑借其對iPDK標準強大的支持,Synopsys的Laker定制解決方案為用戶提供了從180-nm到16-nm的多種TSMC工藝技術的全面對接。

2013-09-23 14:45:30 1050

1050 全球知名電子設計創新領先公司Cadence設計系統公司 (NASDAQ: CDNS),今日宣布臺積電采用了Cadence?16納米FinFET單元庫特性分析解決方案。

2014-10-08 19:03:22 1594

1594 俄勒岡州威爾遜維爾,2015 年 4 月 6 日—Mentor Graphics公司(納斯達克代碼:MENT )今天宣布,TSMC和Mentor Graphics已經達到在10nm EDA認證合作的第一個里程碑

2015-04-20 14:18:06 1658

1658 2015年4月27日 – 移動應用、基礎設施與航空航天、國防應用中RF解決方案的領先供應商Qorvo, Inc.(納斯達克代碼:QRVO)日前宣布推出一項全新的砷化鎵(GaAs)贗晶型高電子遷移率晶體管(pHEMT)工藝技術,與競爭對手的半導體工藝相比,該技術能夠提供更高的增益/帶寬和更低的功耗。

2015-04-28 11:37:09 973

973 Mentor Graphics公司(納斯達克代碼:MENT)今天宣布,Calibre? nmPlatform 已通過TSMC 10nm FinFET V0.9 工藝認證。此外,Mentor

2015-09-21 15:37:10 1300

1300 三星于2015年第一季度發布了半導體芯片行業首款采用14nmLPE (Low-Power Early) 工藝量產的Exynos 7 Octa處理器,成為FinFET邏輯制程上的行業引領者。

2016-01-15 17:12:47 927

927 俄勒岡州威爾遜維爾,2016 年 3 月 11 日—Mentor Graphics公司(納斯達克代碼:MENT)今日宣布,與三星電子合作,為三星代工廠的10 納米 FinFET 工藝提供各種

2016-03-11 14:39:21 1266

1266 WILSONVILLE, Ore., 2016年3月15日— Mentor Graphics公司(納斯達克代碼:MENT)今天發布了一款結合設計、版圖布局和驗證的解決方案,為TSMC集成扇出型 (InFO) 晶圓級封裝技術的設計應用提供支持。

2016-03-15 14:06:02 988

988 TSMC已經按照Synopsys的IC Compiler? II布局及 布線解決方案,完成了在其最先進的10-納米(nm)級FinFET v1.0技術節點上運行Synopsys數字、驗收及自定義實施工具的認證。

2016-03-23 09:12:01 1731

1731 Mentor Graphics公司(納斯達克代碼:MENT)今天宣布,借由完成 TSMC 10 納米 FinFET V1.0 認證,進一步增強和優化Calibre? 平臺和 Analog

2016-03-24 11:13:19 816

816 2016年5月19日,北京訊——ARM今日發布了首款采用臺積電公司(TSMC)10納米FinFET工藝技術的多核 64位 ARM?v8-A 處理器測試芯片。仿真基準檢驗結果顯示,相較于目前常用于多款頂尖智能手機計算芯片的16納米FinFET+工藝技術,此測試芯片展現更佳運算能力與功耗表現。

2016-05-19 16:41:50 662

662 半導體的制造流程以及各工位的詳細工藝技術。

2016-05-26 11:46:34 0

0 PCB測試工藝技術,很詳細的

2016-12-16 21:54:48 0

0 撓性電路板化學鎳鈀金工藝技術研究

2017-01-22 20:56:13 0

0 確保連續四代全可編程技術及多節點擴展的領先優勢四代先進工藝技術和3D IC以及第四代FinFET技術合作 2015年5月28日, 中國北京 - All Programmable 技術和器件的全球領先

2017-02-09 03:48:04 198

198 三星10納米工藝技術公告:全球領先的三星電子先進的半導體元器件技術正式宣布,其第二代10納米(nm)FinFET工藝技術,10LPP(Low Power Plus)已經合格并準備就緒用于批量生產。

2017-05-03 01:00:11 580

580 節點FinFET技術,7LPP和8LPP工藝技術不僅進一步優化了功耗、性能和面積特性,擴展能力也更為出色。目前,客戶已經可以應用下一代技術開始早期設計。

2017-06-02 16:04:34 1237

1237 在2011年初,英特爾公司推出了商業化的FinFET,使用在其22納米節點的工藝上[3]。從IntelCorei7-3770之后的22納米的處理器均使用了FinFET技術。由于FinFET具有

2018-07-18 13:49:00 119524

119524

楷登電子(美國 Cadence 公司)今日正式公布其與臺灣積體電路制造股份有限公司(TSMC)全新12nm FinFET緊湊型(12FFC)工藝技術開發的合作內容。憑借Cadence 數字

2018-05-08 11:07:00 1422

1422 TSMC最新版5nm FinFET 和 7nm FinFET Plus 工藝的認證。Mentor 同時宣布,已更新了 Calibre nmPlatform 工具,可支持TSMC的晶圓堆疊封裝 (WoW)技術

2018-05-17 15:19:00 3391

3391 Synopsys設計平臺用于高性能、高密度芯片設計 重點: Synopsys設計平臺獲得TSMC工藝認證,支持高性能7-nm FinFET Plus工藝技術,已成功用于客戶的多個設計項目。 針對

2018-05-17 06:59:00 4461

4461 Synopsys Synopsys近日宣布, Synopsys 設計平臺獲得TSMC最新版且最先進的5nm工藝技術認證,可用于客戶先期設計。通過與TSMC的早期密切協作,IC CompilerII

2018-06-01 09:35:00 3784

3784 Mentor Graphics Corp. 與英特爾公司宣布,Mentor 的電路模擬和驗收工具已經完全啟用英特爾面向 Intel Custom Foundry 客戶的 14nm三柵極工藝技術

2018-06-02 12:00:00 1381

1381 印刷電路板工藝:伴隨微間距LED顯示屏發展趨勢,4層、6層板被采用,印制電路板將采用微細過孔和埋孔設計,印制電路圖形導線細、微孔化窄間距化,加工中所采用的機械方式鉆孔工藝技術已不能滿足要求,迅速發展起來的激光鉆孔技術將滿足微細孔加工。

2018-07-06 14:11:06 3768

3768 基于7nm工藝技術的控制器和PHY IP具有豐富的產品組合,包括LPDDR4X、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP。

IP解決方案支持TSMC 7nm工藝技術所需的先進汽車設計規則,滿足可靠性和15年汽車運行要求。

2018-10-18 14:57:21 6541

6541 新思科技(Synopsys)推出支持TSMC 7nm FinFET工藝技術的汽車級DesignWare Controller和PHY IP。DesignWare LPDDR4x、MIPI CSI-2

2018-11-13 16:20:23 1517

1517 關鍵詞:5nm , Compiler , PrimeTime 新思科技(Synopsys)宣布其數字和定制設計平臺通過了TSMC最先進的5nm EUV工藝技術認證。該認證是多年廣泛合作的結果,旨在

2018-10-27 22:16:01 255

255 4月16日,三星官網發布新聞稿,宣布已經完成5納米FinFET工藝技術開發,現已準備好向客戶提供樣品。

2019-04-16 17:27:23 3008

3008 PCB板上的線路圖形就是PCB線路板廠家采用曝光成像與顯影蝕刻工藝技術來完成的,無論是PCB多層線路板還是柔性線路板在制作線路圖形時都要用到曝光成像與顯影工藝技術。下面來詳細介紹這兩種工藝的加工特點及加工原理。

2019-04-28 15:10:52 31336

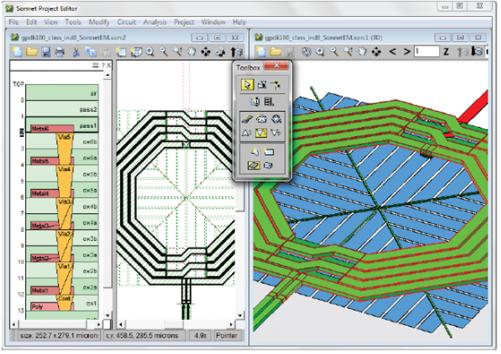

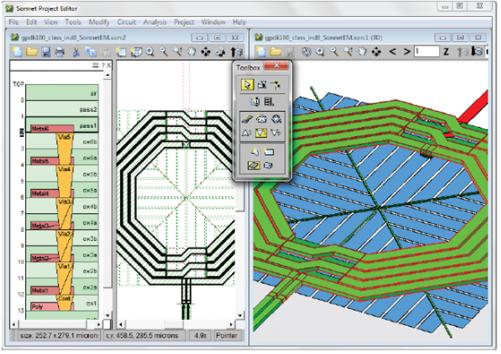

31336 在14版本中,SONNET新引入了一種名為工藝技術層的屬性定義層,以實現EDA框架和設計流程的平滑過渡。該工藝技術層實際上是用戶創建的EM工程中 的多個屬性對象的集合體,其中包括了很多基本屬性設置,比如層的命名、物理位置、金屬屬性、網格控制選項等等。

2019-10-08 15:17:41 2021

2021

Mentor 與 TSMC 的合作現已擴展到先進封裝技術領域, Mentor Calibre? 平臺的 3DSTACK 封裝技術將進一步支持 TSMC 的先進封裝平臺。

2020-05-28 08:48:25 1011

1011 本文檔的主要內容詳細介紹的是CMOS工藝技術的學習課件免費下載。

2020-12-09 08:00:00 0

0 日 /美通社/ -- Arasan Chip Systems為臺積公司(TSMC)行業領先的22nm工藝技術擴展其IP產品,用于臺積公司22nm工藝SoC設計的eMMC PHY IP立即可用。臺積公司22nm工藝

2021-01-21 10:18:23 2385

2385 電子發燒友網為你提供PCBA灌膠的工藝技術和三種方法資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:43:40 34

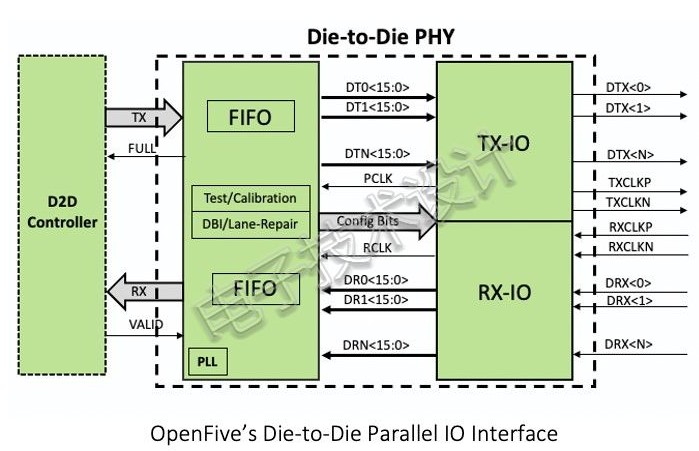

34 最大的RISC-V架構廠商SiFive近日宣布,其OpenFive部門已成功采用臺積電(TSMC)的N5工藝技術流片公司首個SoC,采用2.5D封裝HBM3存儲單元,帶寬7.2Gbps。在半導體行業中,流片意味著芯片設計大功告成,一般會在一年內投入商用。

2021-05-01 09:33:00 2960

2960

多絞屏蔽線處理及焊接工藝技術綜述

2021-07-12 09:45:59 3

3 Cadence 和 TSMC 聯手進行 N3 和 N4 工藝技術合作, 加速賦能移動、人工智能和超大規模計算創新 雙方共同客戶現可廣泛使用已經認證的 N3 和 N4 流程 PDK 進行設計 完整

2021-10-26 15:10:58 1928

1928 淺析ROHM的汽車照明解決方案

2021-11-19 14:50:28 5

5 淺析LED電磁兼容解決方案

2022-01-25 16:10:59 10

10 Siemens Digital Industries Software 宣布,其用于模擬、數字和混合信號 IC 設計的電源完整性分析的全新 mPower? 解決方案現已通過 TSMC 的 N7 和 N5 工藝技術認證。

2022-03-16 14:36:14 1489

1489 全面解讀電子封裝工藝技術

2022-10-10 11:00:51 876

876 工藝技術的FINFLEX架構認證 此外,該認證也可擴展到臺積電N4工藝技術 Ansys宣布Ansys電源完整性解決方案榮獲臺積電FINFLEX創新架構以及N4工藝技術認證,持續深化與臺積電的長期技術

2022-11-17 15:31:57 696

696 2006電子元器件搪錫工藝技術要求

2023-08-23 16:48:03 3

3 流程,能兼容所有的 TSMC(臺積電)先進節點,包括最新的 N3E 和 N2 工藝技術。 這款生成式設計遷移流程由 Cadence 和 TSMC 共同開發,旨在實現定制和模擬 IC 設計在 TSMC

2023-09-27 10:10:04 301

301 電子產品裝聯工藝技術詳解

2023-10-27 15:28:22 373

373

密性等。本文介紹了五種用于MEMS封裝的封帽工藝技術,即平行縫焊、釬焊、激光焊接、超聲焊接和膠粘封帽。總結了不同封帽工藝的特點以及不同MEMS器件對封帽工藝的選擇。本文還介紹了幾種常用的吸附劑類型,針對吸附劑易于飽和問題,給出了封帽工藝解決方案,探

2024-02-25 08:39:28 171

171

電子發燒友App

電子發燒友App

評論