1. 背景 這篇文章主要介紹了DDR3IP核的寫實現(xiàn)。 2. 寫命令和數(shù)據(jù)總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 5068

5068

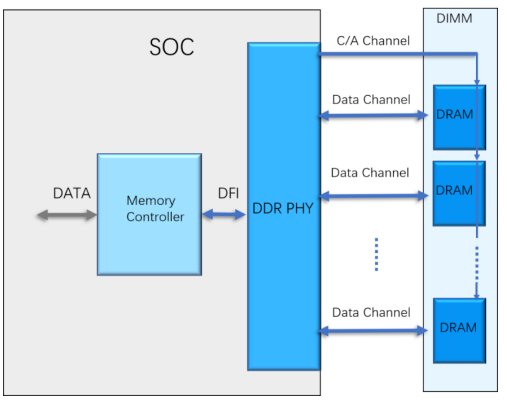

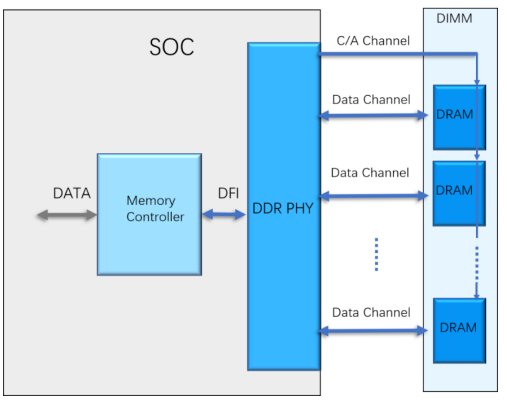

DDR PHY是DRAM和內(nèi)存控制器通信的橋梁,它負責把內(nèi)存控制器發(fā)過來的數(shù)據(jù)轉(zhuǎn)換成符合DDR協(xié)議的信號,并發(fā)送到DRAM。

2021-04-20 11:37:25 4540

4540

完全可以用靠近輸入輸出引腳處的邏輯資源來實現(xiàn)DDR觸發(fā)器,而且最后的結(jié)果表明,這種實現(xiàn)方式可以滿足時序要求。 從圖4中也可以看到,控制器內(nèi)部有兩個時鐘,clk和clk_90,兩者之間的相位差為90°。圖中

2018-12-18 10:17:15

交叉存取來提高帶寬。一個易于使用和可預測的存儲器控制器,如:ECP3 DDR3存儲器控制器,在用戶基于其對數(shù)據(jù)處理的基本算法的了解的情況下來分配存儲器緩沖區(qū)時,可以最小的硬件和軟件開銷來實現(xiàn)最大的帶寬

2019-05-24 05:00:34

DDR3存儲器接口控制器是什么?有什么優(yōu)勢?

2021-04-30 06:57:16

通過 ODT 同時管理所有內(nèi)存顆粒引腳的信號終結(jié),并且阻抗值也可以有多種選擇,內(nèi)存控制器可以根據(jù)系統(tǒng)內(nèi)干擾信號的強度自動調(diào)整阻值的大小。”如題,DDR2和DDR3的ODT功能只存在DQ,DQS和DM中,而這三個信號不存在多顆粒共用情況,都是每片DRAM顆粒獨立工作,怎么能起到抑制反射的作用呢?

2018-01-19 09:43:18

DDR4,開發(fā)版使用的是DDR3。DRAM:動態(tài)隨機存儲器,內(nèi)部存儲單元的以電容電荷表示數(shù)據(jù),1代表有電荷,0代表無數(shù)據(jù)。DRAM結(jié)構(gòu)簡答,所以成本低,集成度高。但是存取速度不如SRAM。? 2.DDR?常見頻率100MHZ,133MHZ,166M,200MHz。?計算容量:行地址位row=

2022-02-07 06:15:06

小,256Kb-16Mb 5.集成度低,單位容量價格高 6.靜態(tài)功耗低,運行功耗大 DRAM 1.速度較慢 2.需要刷新來保持數(shù)據(jù) 3.需要MCU帶外部存儲控制器 4.容量大,16Mb-4Gb 5.集成度高,單位容量價格低 6.運行功耗低

2020-12-10 15:49:11

圍設備。外圍設備連接的引腳連接到微型計算機功能,稱為輸入/輸出端口(I/O端口)。端口是微型計算機和外圍設備連接的端子。如果您想從微型計算機打開/關閉LED,您可以通過執(zhí)行程序中的端口控制來實現(xiàn)。端口

2021-09-10 09:14:16

實現(xiàn)特權(quán)同學的例程 特權(quán)FPGA VIP視頻圖像開發(fā)套件例程詳解2——DDR2控制器讀寫測試 時,進行IP核配置時,進入下一步配置參數(shù)時,變成黑屏重裝軟件也不行

2018-01-24 08:23:17

靜態(tài)隨機存取存儲器SRAM是什么?有何優(yōu)缺點?動態(tài)隨機存取存儲器DRAM是什么?有何優(yōu)缺點?

2021-12-24 07:04:20

6655時鐘PLL配置與DDR3的配置1 時鐘概述PLL與PLL控制器的邏輯組成和處理流程如圖1所示。PLL控制器能夠通過PLLDIV1到PLLDIV16這些分頻器靈活便利的配置和修改內(nèi)部的時鐘信號

2018-01-24 21:27:10

4的JEDEC標準DDR4接口的變體,它包含了對完整系統(tǒng)支持所需的獨特功能。本文將幫助工程師了解Xilinx FPGA控制器的Everspin STT-DDR4設計指南

2021-01-15 06:08:20

你好任何人都可以指導我,Xilinx ISE中的DDR控制器是否有任何IP實現(xiàn)。如果沒有如何實現(xiàn)DDR控制器以上來自于谷歌翻譯以下為原文Hi can any one guide me

2019-02-27 12:13:51

/ p作為輸入時鐘連接到CLKGENERATOR,DDR控制器在Phy側(cè)運行800Mhz,在控制器運行200Mhz.Slave AXI總線寬度為AXI.DDRis 512bits。卡皮爾古普塔project_6.srcs.rar 6322 KB

2019-09-10 07:58:12

Rambus DRAM與CTM時鐘同步輸出數(shù)據(jù)。如果時鐘與數(shù)據(jù)信號的布線長度等相同,則時鐘與數(shù)據(jù)具有相同的延遲時間到達DRAM控制器,所以DRAM控制器可以與時鐘同步接受數(shù)據(jù)。 另一方面

2008-12-04 10:16:36

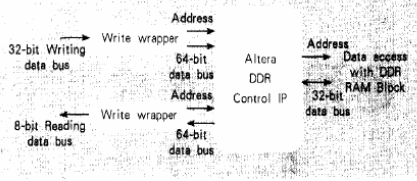

本文和設計代碼由FPGA愛好者小梅哥編寫,未經(jīng)作者許可,本文僅允許網(wǎng)絡論壇復制轉(zhuǎn)載,且轉(zhuǎn)載時請標明原作者。Altera DDR2控制器使用IP的方式實現(xiàn),一般很少自己寫控制器代碼。ddr

2020-02-25 18:33:00

為什么XMC庫不使用控制器的端口輸出寄存器TESTBOARD_150PC_OUT ?

程序庫僅使用端口輸出修改寄存器 Pn_OMR 來設置或清除數(shù)字輸出。

2024-03-06 06:17:41

分析閃存控制器的架構(gòu),首先得了解SSD。一般來說SSD的存儲介質(zhì)分為兩種,一種是采用閃存(Flash芯片)作為存儲介質(zhì),另外一種是采用DRAM作為存儲介質(zhì)。我們通常所說的SSD就是基于閃存的固態(tài)硬盤

2019-09-27 07:12:52

)”,正如圖中所示,它們各有分工。存儲控制器產(chǎn)生DDR2芯片實際讀寫操作需要的時序;ALTMEMPHY有兩部分功能,一個功能是對DDR2做自動校正(Aoto-Calibration),另一個功能是實現(xiàn)DDR

2016-10-27 16:36:58

我是一名labview FPGA程序員,使用的是NI 7975 fpga模塊,它具有kintex 7 fpga。該模塊具有外部DDR3 DRAM 0f 2GB以及kintex 7 fpga資源。數(shù)據(jù)應該從芯片到芯片之間會有多少延遲?這是DDR3 DRAM雙端口(同時讀寫操作可能??)???

2020-05-20 14:42:11

這是我自己寫ddr2控制器的寫操作,但為什么寫的地址不按順序?qū)懀姓l做過嗎?

2017-03-20 16:36:20

我可以使用mig生成ddr控制器(xc6vlx130t)嗎?mig向?qū)е恢С?b class="flag-6" style="color: red">ddr2和ddr3!

2020-06-12 07:32:48

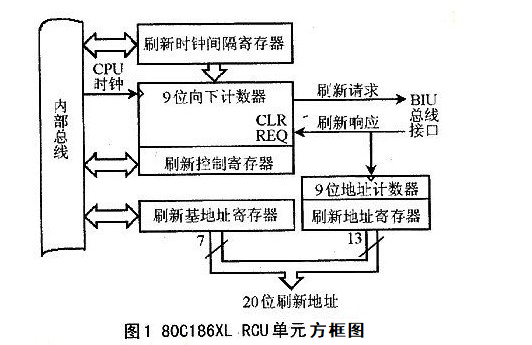

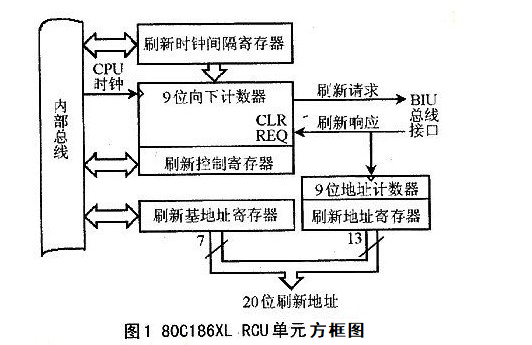

控制單元。RCU單元可以自動產(chǎn)生DRAM刷新總線周期,它工作于微處理器的增益模式下。經(jīng)適當編程后,RCU將向?qū)⑻幚?b class="flag-6" style="color: red">器的BIU(總線接口)單元產(chǎn)生存儲器讀請求。對微處理器的存儲器范圍編程后,BIU單元執(zhí)行刷新周期時,被編程的存儲器范圍片選有效。

2019-11-07 06:01:59

請求。物理層接口前端連接至內(nèi)存控制器模塊,后端連接外部存儲設備,其主要功能是捕獲DDR3發(fā)出的數(shù)據(jù),產(chǎn)生DDR3所需要的控制指令信號,并通過輸入輸出緩存發(fā)送所有DDR3的控制信號、地址信號以及數(shù)據(jù)信號

2018-08-02 09:34:58

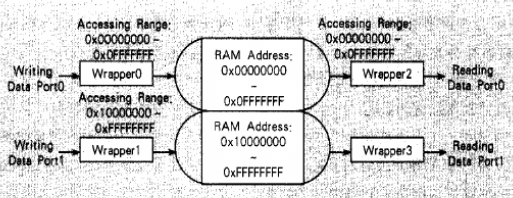

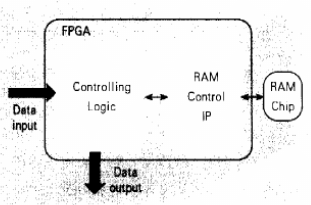

作者:吳連慧,周建江,夏偉杰摘要:為了解決視頻圖形顯示系統(tǒng)中多個端口訪問DDR3的數(shù)據(jù)存儲沖突,設計并實現(xiàn)了基于FPGA的DDR3存儲管理系統(tǒng)。DDR3存儲器控制模塊使用MIG生成DDR3控制器

2018-08-02 11:23:24

80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場的上導產(chǎn)品之一,已廣泛應用于電腦終端、程控交換和工控等領域。在該嵌入式微處理器片內(nèi),集成有DRAMRCU單元,即DRAM刷新控制單元。RCU單元可以自動產(chǎn)生DRAM刷新總線周期,它工作于微處理器的增益模式下。

2019-09-25 07:38:04

如何實現(xiàn)雙路輸出控制器的設計?

2022-02-11 07:57:24

如何實現(xiàn)觸摸屏控制器TSC輔助輸入的應用?TSC輔助輸入的主要特性有哪些?如何實現(xiàn)TSC掉電期間的ESD保護?有什么輔助輸入要求?

2021-04-20 06:52:13

DDR3存儲器控制器面臨的挑戰(zhàn)有哪些?如何用一個特定的FPGA系列LatticeECP3實現(xiàn)DDR3存儲器控制器。

2021-04-30 07:26:55

你好使用Xilinx的任何一個端口MIG DDR2 SDRAM控制器都是我遇到了問題我有vhdl頂級系統(tǒng),其中我實例化ddr2控制器我的ddr2包裝器與testcase一起工作正常(由MIG提供

2019-08-19 10:47:06

你好如何在不使用DDR內(nèi)存控制器的情況下設計FPGA BRAM(或任何其他內(nèi)存模塊_SD,DDR以外的本地等)大容量存儲單元?當我通過示例設計“VC707_bist”替換DRAM控制器和BRAM

2019-04-04 15:10:55

TL494是什么?回路控制器的工作原理是什么?如何用TL494和輸入輸出電路構(gòu)成一個單回路控制器呢?

2021-10-09 08:09:00

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰(zhàn)性。在FPGA中實現(xiàn)高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數(shù)高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

嗨,我已經(jīng)搜索了很多關于配置PS DRAM控制器(DDRC)板參數(shù)的信息,鏈接如下,http://www.xilinx.com/support/answers/46778.htm, 我想知道如何獲得包裝長度?謝謝!

2019-11-07 08:43:39

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq

2021-01-07 16:02:09

如何調(diào)試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

嵌入式控制器的輸入端口設計分析,不看肯定后悔

2021-05-31 06:19:13

摘要:介紹怎樣在嵌入式CPU 80C186XL DRAM刷新控制單元的基礎上,利用CPLD技術和80C196XL的時序特征設計一個低價格、功能完整的DRAM控制器的方法,并采用VHDL語言編程實現(xiàn)

2011-02-24 09:33:15

學單片機的都必須清楚微控制器的輸入輸出,點燈是練習輸出,而輸入最基礎的就需要去練習——按鍵。

2021-11-29 07:38:40

大家好,我想設計自己的DDR控制器并在FPGA上驗證它。我將在verilog中實現(xiàn)我剛開始閱讀JESDC79C DDR規(guī)格..但我很困惑如何編寫那些初始化序列?請建議如何處理這個設計DDR控制器

2019-04-29 11:59:22

需要一個PWM控制器來實現(xiàn)升壓電路的開關,但是目前找到的PWM控制器的輸入電壓都在4-5V,有沒有什么PWM控制器有輸入電壓大概1V或以下的。謝謝!

2019-09-03 08:57:45

有沒有辦法重置和重新初始化 DDR 控制器?DRAM 類型是 LPDDR4。

我們的目標:我們嘗試為組裝有不同大小 RAM 的電路板系列實施解決方案。

為了獲得可重現(xiàn)的結(jié)果,我們尋求在嘗試下一個配置

2023-05-16 09:03:04

目前有一個項目需要使用DDR3作為顯示緩存,VGA作為顯示器,F(xiàn)PGA作為主控器,來刷圖片到VGA上。VGA部分已經(jīng)完成,唯獨這個DDR3以前沒有使用過,時序又比較復雜,所以短時間內(nèi)難以完成,希望做過DDR3控制器的大神指點一二。急求!!!!

2015-11-16 09:18:59

本文介紹了怎樣在嵌入式CPU 80C186XL DRAM刷新控制單元的基礎上,利用CPLD技術和80C196XL的時序特征設計一個低價格、功能完整的DRAM控制器的方法,并采用VHDL語言編程實現(xiàn)。

2021-04-28 07:10:38

LTC3718的典型應用是用于DDR和QDR存儲器終端的高電流,高效率同步開關穩(wěn)壓控制器

2019-05-31 08:11:00

你好我在Spartan 6 LX150T設計中使用DDR2控制器,并且正在努力解決時鐘資源問題。我發(fā)現(xiàn)DDR控制器在其memc1_infrastructure_inst模塊中有一個BUFGCE組件

2019-06-26 14:50:14

DDR SDRAM在嵌入式系統(tǒng)中有哪些應用?DDR SDRAM的工作方式有哪幾種?怎樣去設計DDR SDRAM控制器?

2021-04-30 07:04:04

FPGA與DDR2存儲器接口DDR2控制器的設計原理是什么?DDR2控制器的應用有哪些?

2021-04-30 06:28:13

通過前段時間的學習,我們基本上已經(jīng)掌握了關于單片機的端口控制,可以通過控制端口的電位變化來實現(xiàn)一些功能。有時間也可以練習一些復雜的變化,來熟悉自己的所學知識。輸出是說的差不多了,那么接下來的一段時間

2022-01-18 10:37:36

設計實現(xiàn)了一種基于FPGA 的,可用于多數(shù)據(jù)緩存的、能夠高效利用帶寬的多端口SDRAM 控制器。本文使用狀態(tài)機的設計思想,采用Verilog 硬件描述語言設計了時序控制程序。得到的SDR

2009-08-27 09:43:33 22

22 DDR2 SDRAM控制器的設計與實現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設計方法!詳述了其基本結(jié)構(gòu)和設計思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 實現(xiàn)了一個三端口非透明型SDRAM 控制器,該控制器面向用戶具有多個端口,通過輪換優(yōu)先級的設計保證了多個端口平均分配SDRAM的帶寬且不會降

2010-03-03 14:37:14 11

11 本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結(jié)構(gòu)和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 臺灣DRAM廠商大舉轉(zhuǎn)產(chǎn)DDR3

2010年PC主流內(nèi)存標準從DDR2向DDR3的轉(zhuǎn)換正在逐步成為現(xiàn)實。據(jù)臺灣媒體報道,由于下游廠商的DDR2訂單量近期出現(xiàn)急劇下滑,多家臺系DRAM芯片

2010-01-18 09:25:13 602

602 中央控制系統(tǒng)的視頻輸入端口

VGA輸入:V

2010-01-07 11:53:57 776

776 ADI,全球領先的高性能信號處理解決方案供應商,最近推出 GPIO(通用輸入/輸出)端口擴展器和鍵盤矩陣控制器 ADP5585和 ADP5589

2011-09-14 14:17:53 1477

1477 本文提出一種新穎的解決方案:利用80C186XL的時序特征,采用CPLD技術,并使用VHDL語言設計實現(xiàn)DRAM控制器。

2012-02-02 11:29:58 1185

1185

基于協(xié)議控制器的DDR3訪存控制器的設計及優(yōu)化_陳勝剛

2017-01-07 19:00:39 15

15 DDR2SDRAM控制器在機載顯控系統(tǒng)中的應用_孫少偉

2017-03-19 11:26:54 1

1 DDR 控制器部產(chǎn)品營銷總監(jiān) 概述 DDR DRAM內(nèi)存控制器要滿足眾多市場競爭的需求。一款出色的內(nèi)存控制器必須能夠增加存儲器接口的帶寬,滿足CPU、圖形處理、系統(tǒng)實時DRAM的延遲需求,同時符合

2017-11-18 18:23:12 2522

2522 為了解決視頻圖形顯示系統(tǒng)中多個端口訪問DDR3的數(shù)據(jù)存儲沖突,設計并實現(xiàn)了基于FPGA的DDR3存儲管理系統(tǒng)。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR

2017-11-18 18:51:25 6412

6412

提出一種便于用戶操作并能快速運用到產(chǎn)品的DDR2控制器IP核的FPGA實現(xiàn),使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作

2017-11-22 07:20:50 4687

4687

DRAM (動態(tài)隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統(tǒng)的存儲系統(tǒng)設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 本文透過對于靜態(tài)隨機存取內(nèi)存(SRAM)單元縮減布局面積的研究,提出一種新的 存取技術 ,可望提升動態(tài)隨機存取內(nèi)存( DRAM )單元的訪問速度。 超頻與內(nèi)存的關聯(lián)性 提升供應電壓以及降低環(huán)境溫度有助于增加微處理器、芯片組、主存儲器的頻率頻率。

2018-03-28 12:03:00 4031

4031

DDR 同步動態(tài)隨機存取存儲器 (Synchronous Dynamic Random Access Memory, SDRAM)控制器使用雙倍數(shù)據(jù)速率(Dual Data Rate,DDR)版本

2018-05-30 09:29:00 7

7 本文首先介紹的是PID控制器的工作原理,其次介紹的是pid控制器的輸入輸出,最后介紹了PID控制器的參數(shù)整定以及PID控制器的控制實現(xiàn),具體的跟隨小編一起來了解一下。

2018-06-01 09:09:01 25658

25658 本應用說明描述了一個參考系統(tǒng),該系統(tǒng)演示了Microblaze?處理器系統(tǒng)中多通道(MCH)片上外圍總線(OPB)雙數(shù)據(jù)速率(DDR)同步DRAM(SDRAM)控制器的使用。MCH OPB DDR

2019-09-12 14:14:00 0

0 、PSRAM、MRAM等存儲芯片供應商英尚微電子解析這款比腦力更強大的DDR SDRAM控制器。 任何DRAM控制器背后的智商都是與命令時序和執(zhí)

2020-07-24 14:25:27 719

719 DRAM作為PC必備器件之一,大家自然對DRAM較為熟悉。但是,大家知道DRAM存儲具有哪些分類嗎?大家了解DRAM控制器是如何設計出來的嗎?如果你對DRAM以及本文即將要闡述的內(nèi)容具有興趣,不妨繼續(xù)往下閱讀哦。

2020-10-31 11:51:19 3766

3766

100V 輸入 DC/DC 控制器產(chǎn)生正或負的穩(wěn)壓輸出

2021-03-19 08:09:16 4

4 本應用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實現(xiàn)的 DDR SDRAM 控制器。該實現(xiàn)運用了直接時鐘控制技術來實現(xiàn)數(shù)據(jù)采集,并采用自動校準電路來調(diào)整數(shù)據(jù)線上的延遲。

2021-03-26 14:42:41 4

4 本文首先分析了DDR SDRAM的基本特征,并提出了相應的解決方案詳細介紹了基于J EDEC DDR SDRAM規(guī)范的DDR SDRAM控制器設計方案。該控制器采用Verilog HDL硬件描述語言實現(xiàn),并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 AN-284:用模擬輸入/輸出端口實現(xiàn)無限采樣保持電路

2021-04-22 16:19:39 12

12 LTC3718:適用于DDR/QDR存儲器終端的低輸入電壓DC/DC控制器產(chǎn)品手冊

2021-05-22 16:14:04 6

6 基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)簡介(arm嵌入式開發(fā)平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)(嵌入式開發(fā)式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現(xiàn)總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 )。它的性能更高,并且不額外占用其他的可編程邏輯資源 (PL)。使用它的時候,在硬件設計方面和設計流程上,和之前的軟核控制器(DDR4 IP)也有著很大的不同。今天我們來介紹一下I/O planning方面的設計考慮和實現(xiàn)流程。

2022-07-06 10:42:17 3523

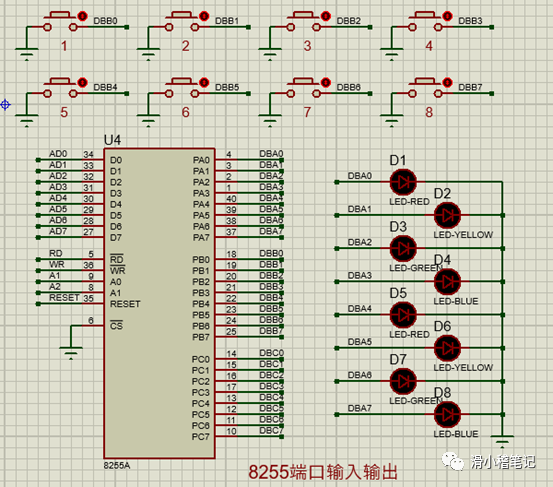

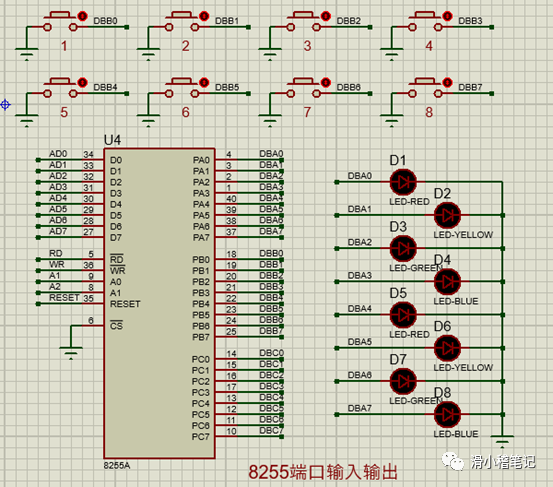

3523 8086的輸入輸出控制是通過8255芯片控制的,用LED代表輸出的數(shù)據(jù),按鍵代表輸入的數(shù)據(jù),八個LED接在8255的PA端口上,八個按鍵接在PB端口上,通過8086控制8255A進行數(shù)字量的輸入與輸出。

2023-03-02 09:56:04 1515

1515

的作用。

編寫程序:編寫控制程序,包括輸入和輸出信號的邏輯關系和運算方法。

連接設備:將需要控制的設備連接到PLC控制器的輸入和輸出端口上。

2023-03-25 09:41:14 794

794 電子發(fā)燒友網(wǎng)站提供《完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 10:16:45 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論