導讀:

DDR4全稱,DDR4-DRAM,與其他DDRDRAM一樣,是當前電子系統架構中使用最為廣泛的的RAM存儲器。 這句話可以分解出3個關鍵字:存儲器、DRAM、DDR4。

存儲器: 先說存儲器,說到存儲,顧名思義,它是個動詞,以生活為例,假如有個酸奶,你不想吃的時候,將酸奶存到某冰箱、某層、某個位置,當你想吃的時候,在某冰箱、某層次、某個位置中取出該酸奶。 這個過程,我們稱為存儲,結合生活,我們可以看到存儲要有3個關鍵動作: 1、酸奶放哪了,你得知道。如果不知道放哪了,酸奶就跟丟了一樣。這個過程,映射到電子領域中,稱為“尋址”。 2、存儲酸奶、取出酸奶。你需要先走到某冰箱跟前,拉開某層抽屜,在具體某個位置,拿出酸奶,這個過程,映射到電子領域中,稱為“讀/寫” 3、酸奶放到那個位置,在需要的時候,得還能吃。這個過程,映射到電子領域中,稱為“數據保存”。 所以,概括一下,存儲器就是“可以尋址”、“能讀寫數據”、“能保存數據”的一種電子器件。

DRAM: 我們再說說DRAM。DRAM全稱Dynamic Random Access Memory,翻譯過來為動態隨機讀取存儲器。所謂隨機,指的是“想存哪個位置,就存哪個位置”,聽起來很自由,很靈活。所謂動態,指的是保存數據過程中,需要不斷的補充電量,聽起來很耗電,很費勁,為啥我們還要用DRAM結構?因為在電路結構上,DRAM結構比SRAM簡單很多。

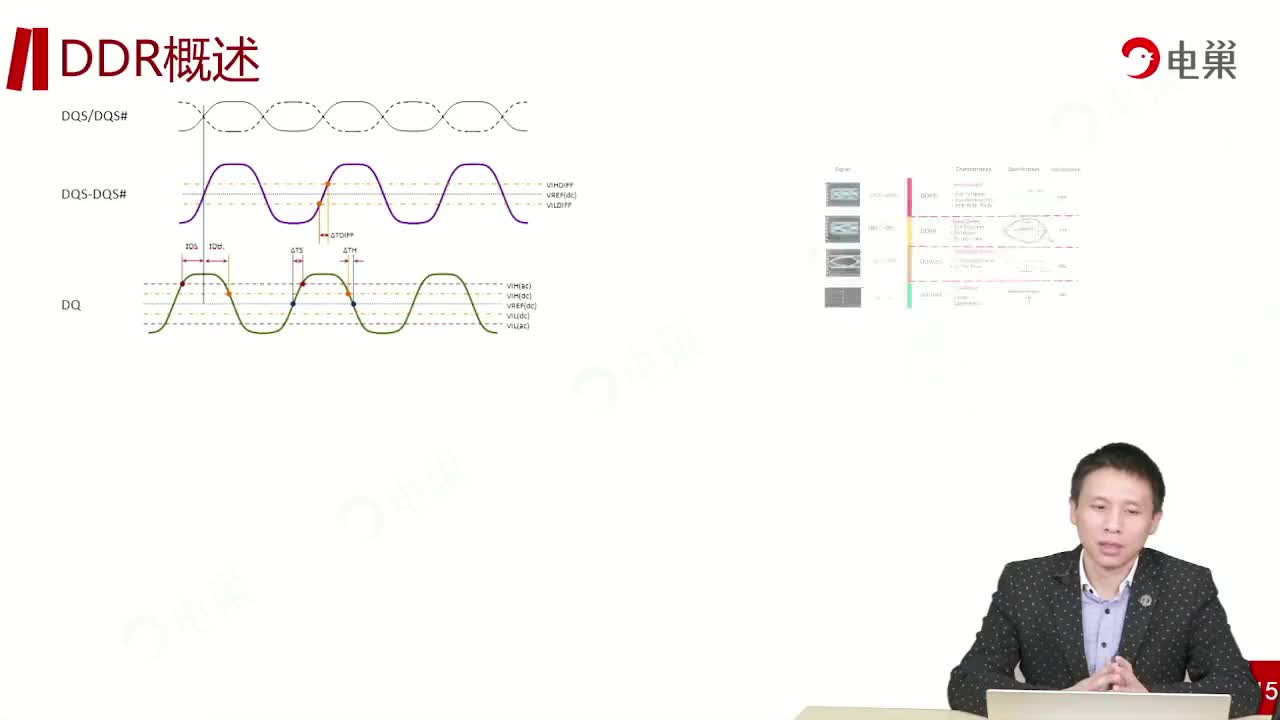

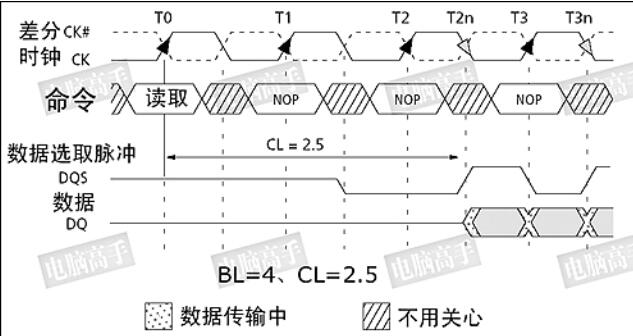

DDR: 最后說說DDR。我們聊到DDR,大家都會聯想到存儲器,但是實際上DDR并不指代存儲器,DDR實際是一種技術,全稱Double Data Rate,翻譯過來為雙倍速率,只是這都技術廣泛使用在DRAM上,所以人們習慣將DDR代指為存儲器,所以在后續的硬件設計過程中,在其他總線上看到DDR,請不要驚慌,因為你看到的DDR可能不一定和存儲有關。 那雙倍速率指的是什么?我們可以簡要說下,初代存儲器在讀寫數據時,每次都在時鐘信號從低變高或從高變低時,采樣數據,在1個時鐘周期,只能采樣1個數。后續聰明的人類在時鐘從低到高時,采樣一個數據,時鐘從高到低時,再采樣1個數據,一個時鐘周期,可以采樣2個數據。所以讀寫速度比以前快了2倍。這種技術手段,就指的是DDR。 所以,概括下:DDR4-DRAM是第四代支持雙數據讀取,支持隨機位置存取的靜態存儲器。

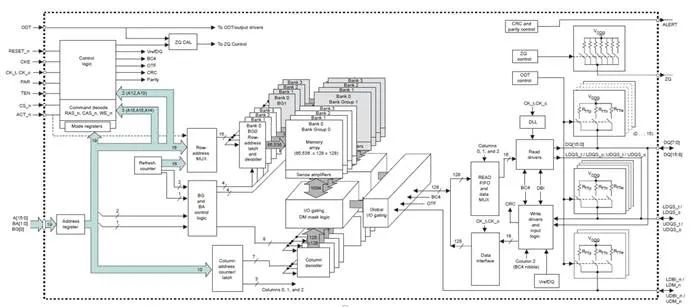

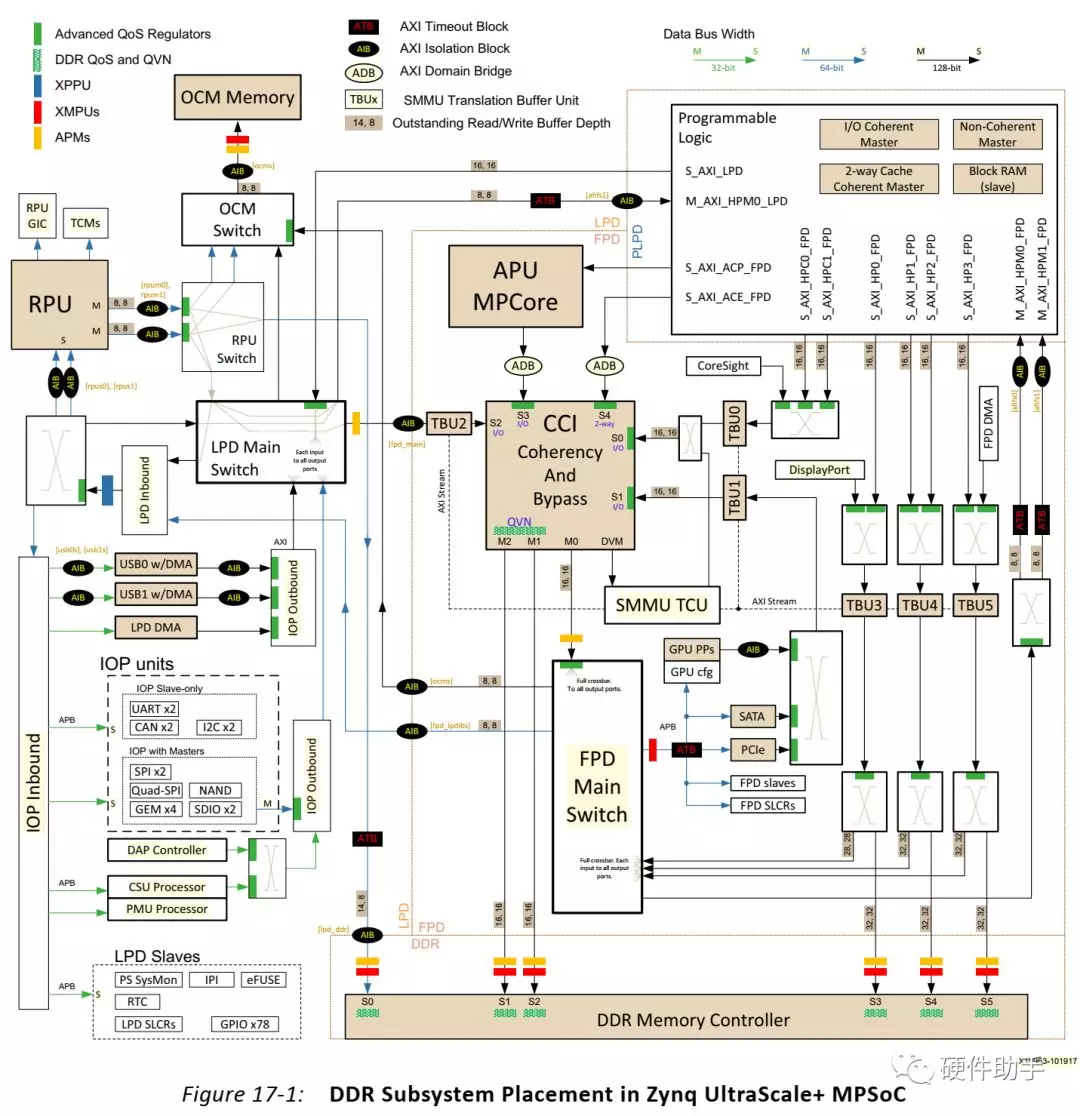

DDR4-DRAM的工作原理: 一顆DDR4芯片的內部功能框圖如下

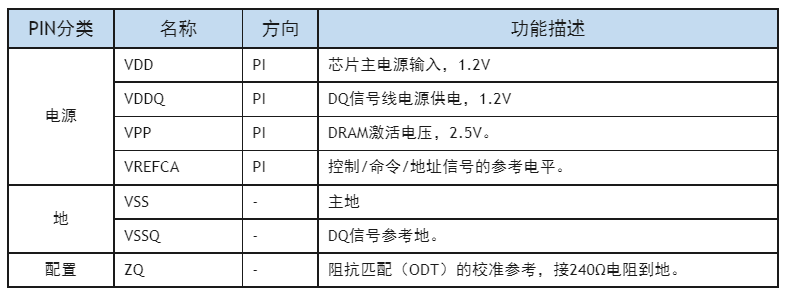

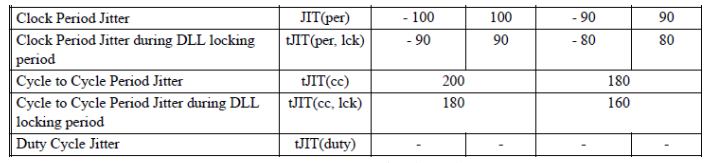

其引腳按照功能可以分為7類:前3類為電源、地、配置。

后4類為:控制信號、時鐘信號、地址信號、數據信號

一、DDR4 信號完整性測試新要求

在 DDR4 規范 JESD79‐4 中,對物理層信號測試要求有:DQ 眼圖模板測試、抖動分析、電氣特性測試,時序測試。相比 DDR3,DDR4 對眼圖測試和抖動測試提出了新的要求。

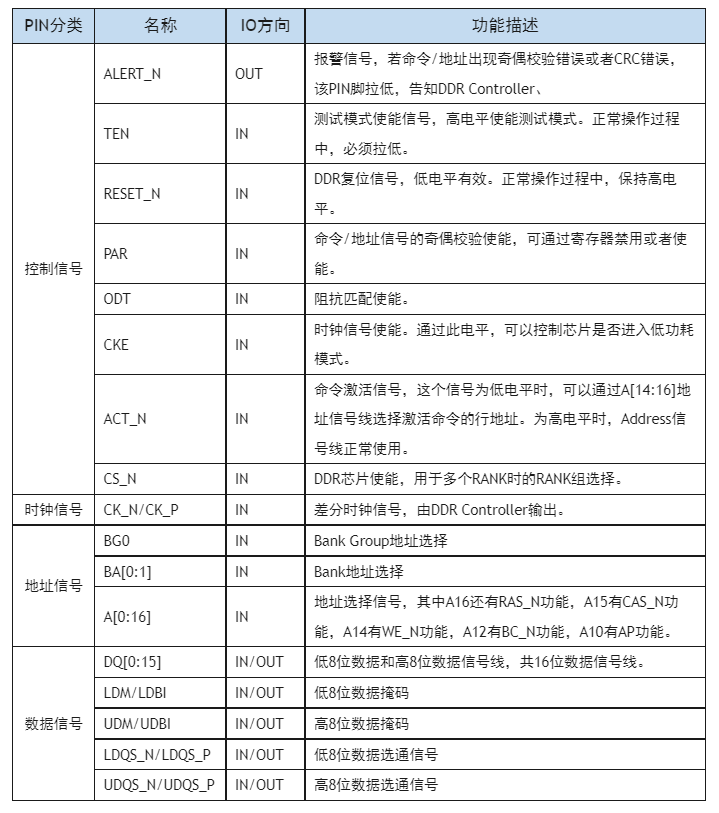

抖動測試

在 DDR3 的測試中,對 Clock 的抖動的測試要求是:Period Jitter、Cycle‐Cycle Jitter、Duty Cycle Jitter。DDR3 的 Spec 中做了這樣的推算:如果你的內存滿足了規范要求的所有電氣特性和時序特性,就可以一直正常的運行。現實狀況下,這是沒有考慮其他因素的理想情況,像隨機抖動等也會影響產品的工作,而 DDR3 都沒有對這些進行測試。

DDR3 Clock 抖動測試

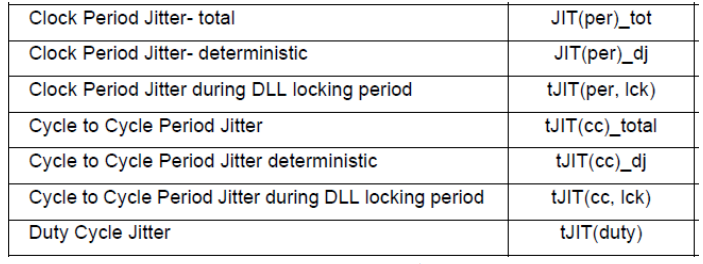

在 DDR4 的規范中,采用了更實際的方法來考慮這些因素,測試要求包含了隨機抖動 Rj 和確定性抖動 Dj,在規范中,總體抖動 Tj 被定義為在一定誤碼率下的確定性抖動 Dj 和隨機性抖動 Rj 的和,對抖動做了分解。

DDR4 Clock Jitter 要求

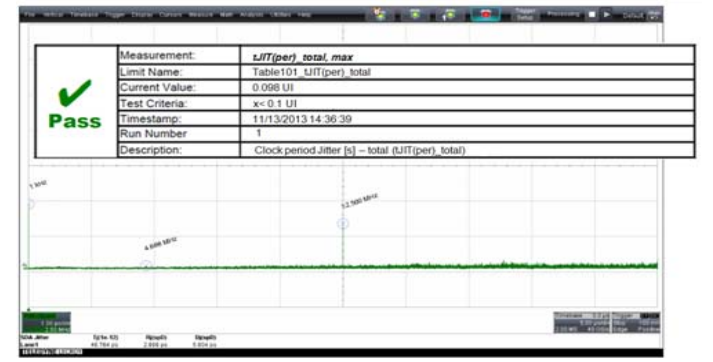

Lecroy Qualiphy‐DDR4 Jitter 測試結果

眼圖模板測試

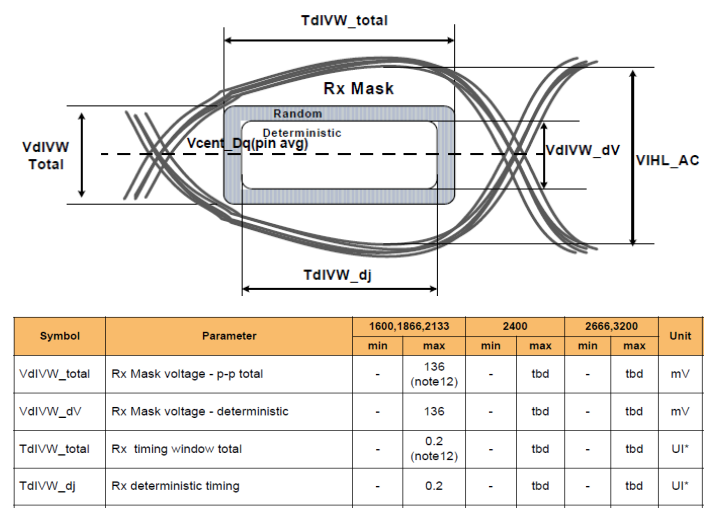

在 DDR3 測試中,眼圖只是作為一個 Debug 的手段,不是強制要求測試,而且沒有模板。但是在 DDR4 中,要求進行 DQ 輸入接收端眼圖模板測試,下圖是眼圖模板的定義,在 DDR4‐2133 及以下頻率,TdIVW_total 和 TdIVW_dj 相等。VdIVW_total 和 VdIVW_dV 相等,從本質上,現在還沒有在模板中定義隨機成分。

DDR4 眼圖模板定義

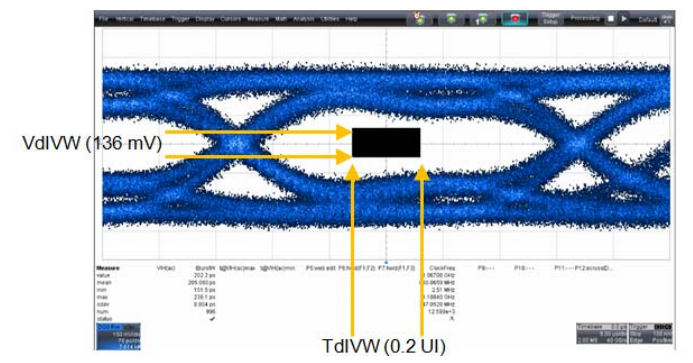

DDR4 DQ 眼圖

二、DDR4 信號完整性測試挑戰

DDR4 的速率提升一倍,同時信號電壓降低也接近一倍,這對測試探測技術提出了更高的要求。

DDR4 規范中的所有測試都是定義在 BGA 或者 DIMM 的管腳處,但是,在很多時候,我們很難直接探測到 BGA 管腳處,這樣測出來的結果誤差會非常大,解決方案是使用 Interposer 夾具或者虛擬探測技術,探測到理想點的波形。

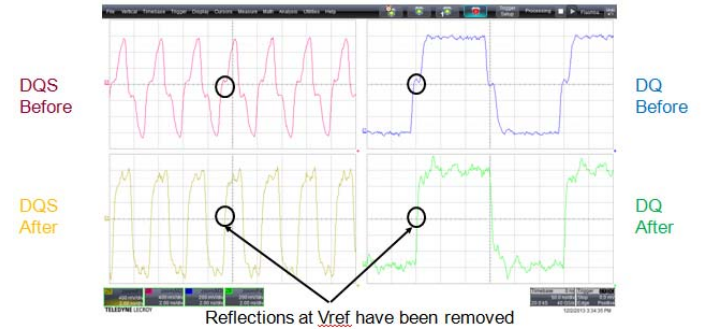

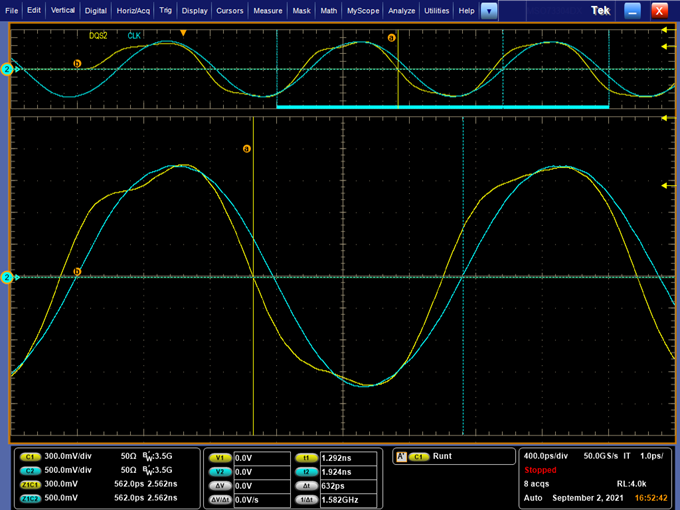

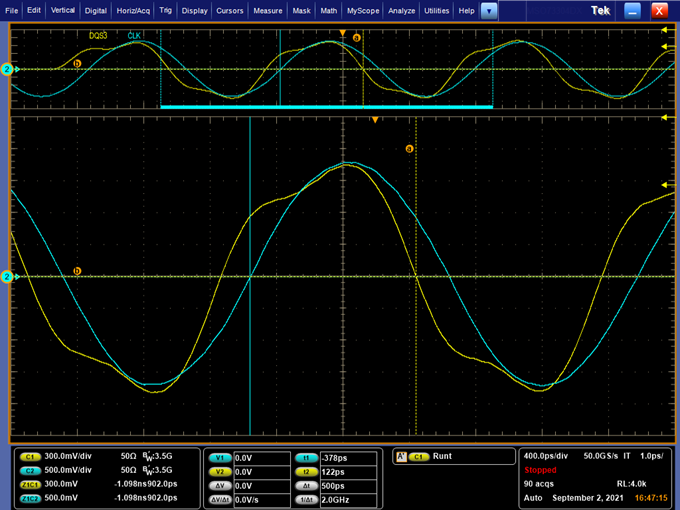

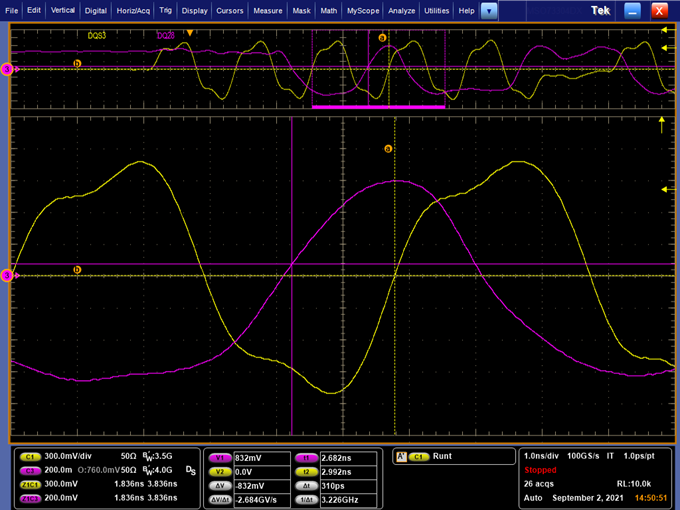

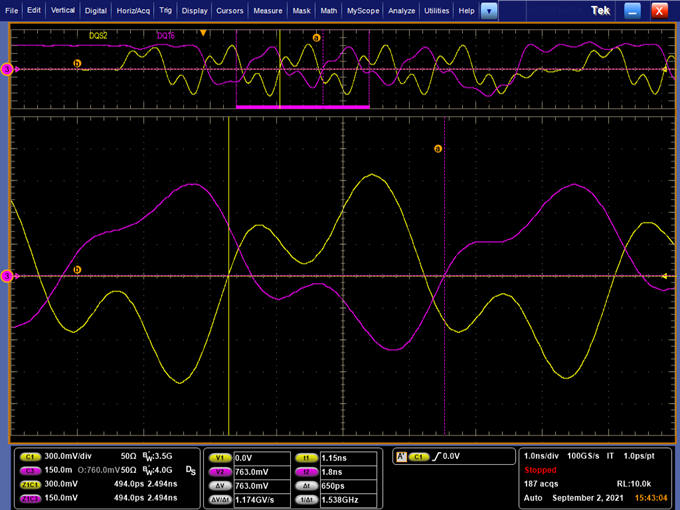

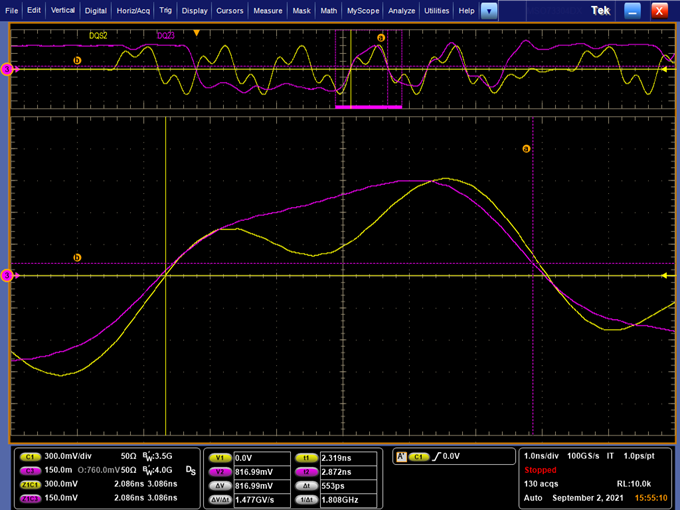

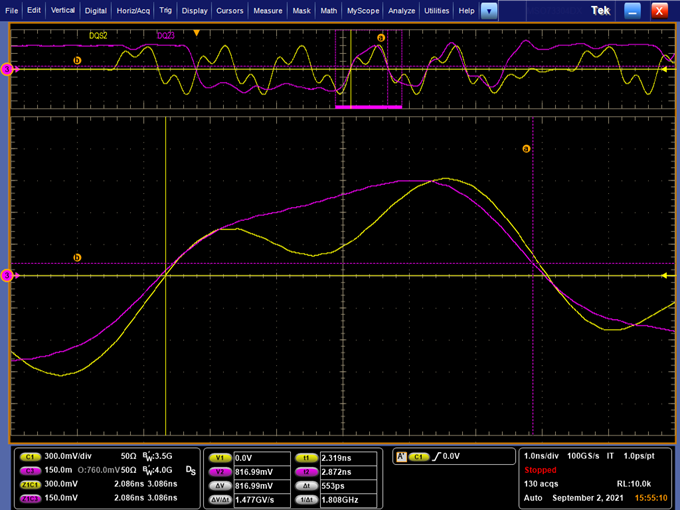

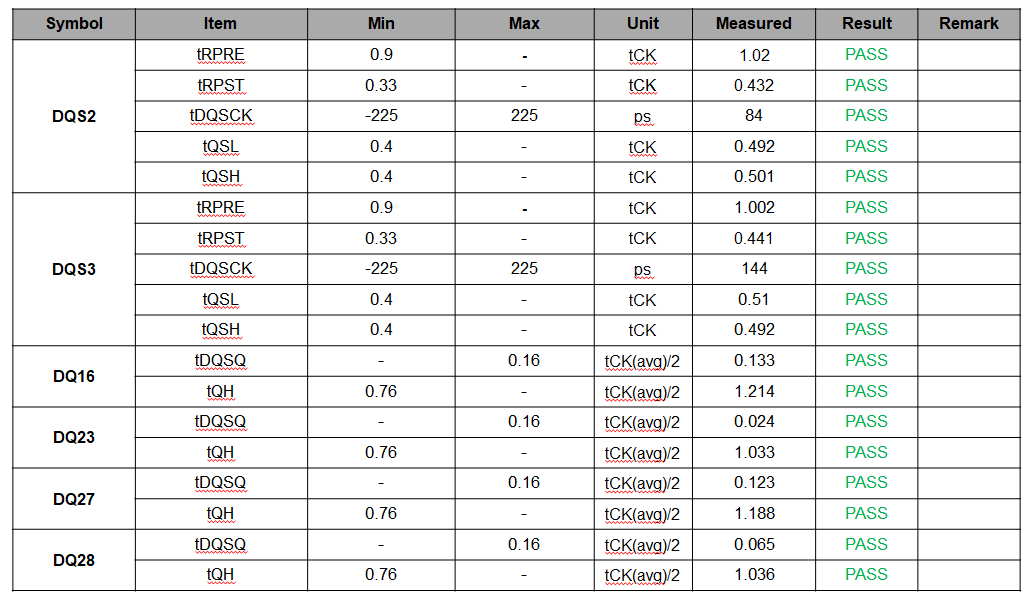

下圖是使用 Virtual Probe 測試 DQS 和 DQ,上方是實際測試點的波形,下方是使用Virtual Probe測試到的BGA處的信號波形,可以很明顯的看到,反射被去除了,這樣測試結果更加準確。

三、DDR4 測試點選取原則

DDR測試點選取的一般原則,即:測讀信號盡量靠近CPU,測量寫信號盡量靠近RAM。

首先,考慮到走線對信號的衰減,一般在靠近芯片的接收側對信號進行量測,這樣,“看”到的信號和芯片“看”到的信號會更加接近。

其次,這樣也會減小反射。

探頭的接入或多或少會導致接入點的阻抗產生變化,原本100Ω左右的差分對走線在探頭連接處變成其他的值(例如50Ω),這樣信號會在這個點產生反射。一般DDR的接收端阻抗的連續性沒有發送端好,所以信號在接收端也會產生反射。

如果信號前進過程中兩個反射點離得比較遠,距離(單位為inch)>信號的上升時間(單位為ns),會對信號產生比較明顯的影響,如果量測到的信號在上升沿有回溝或者在信號高低電平中間有凹陷,這些都是多次反射造成的。

建議探頭的連接點在DDR信號的接收端,能減少這樣多次反射帶來的影響。

四、DDR4 信號完整性測試案例

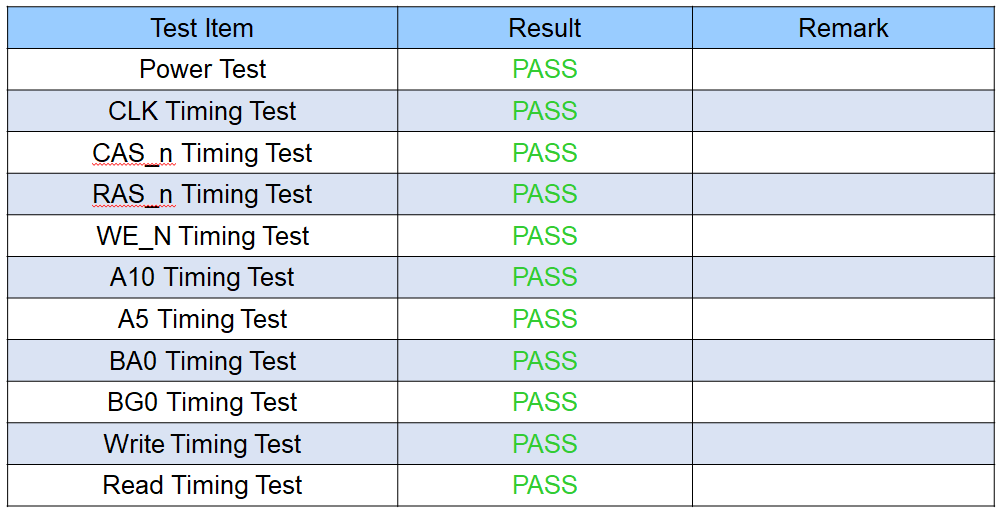

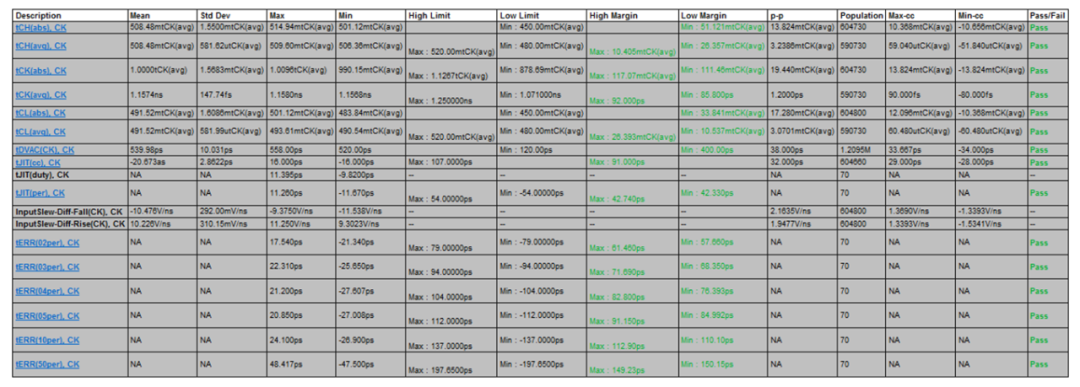

(1) DDR4測試項目及測試結果:

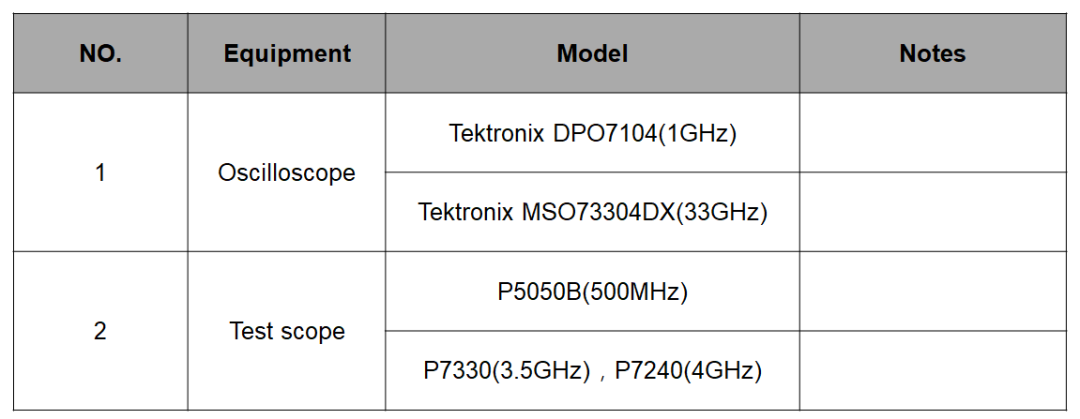

(2) 測試設備及標準:

(3) 測試圖片及結果:

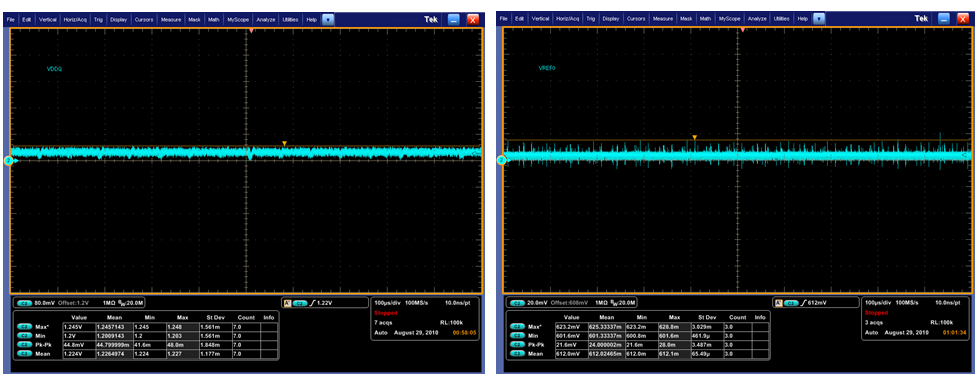

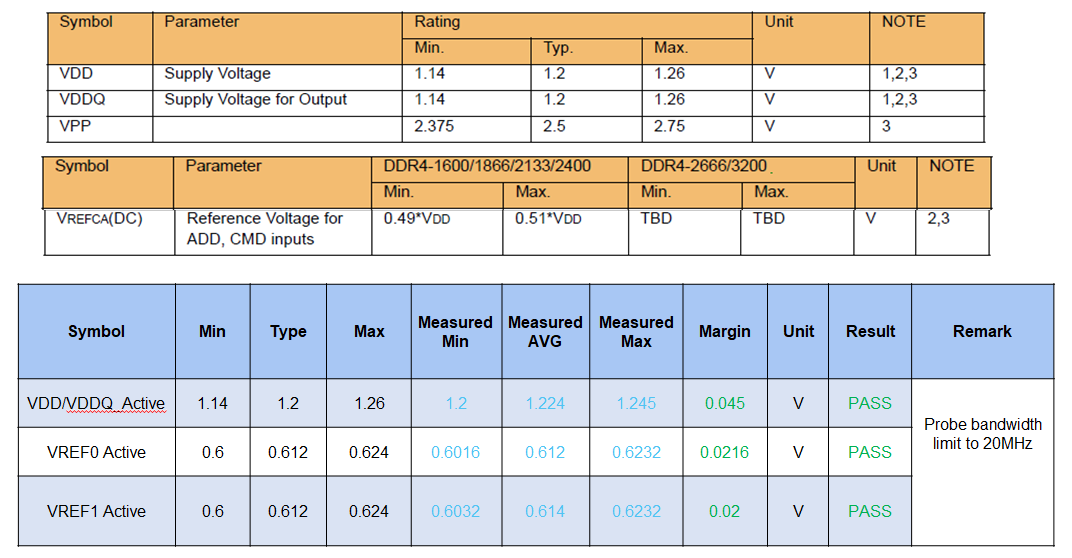

Power Test

Power Test Spec& Result?

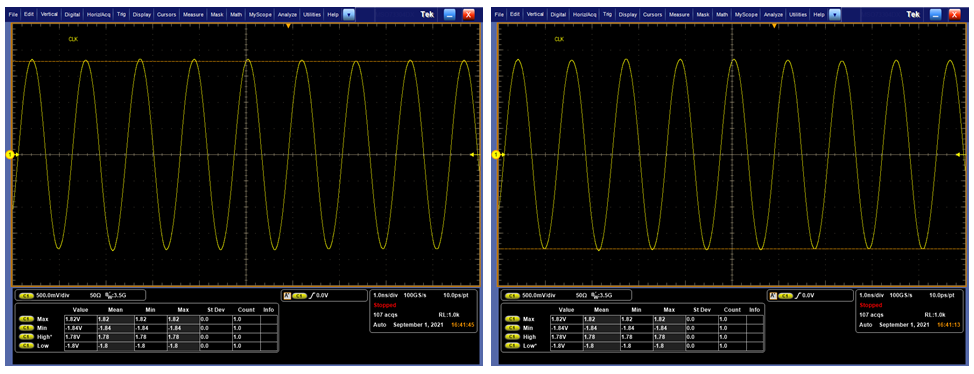

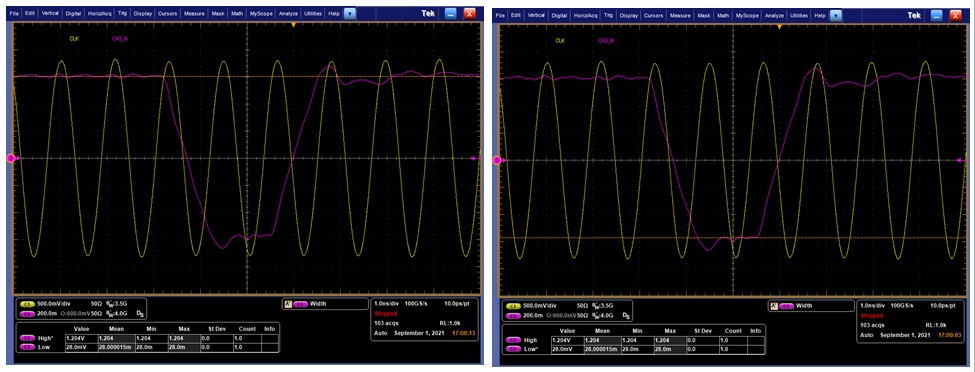

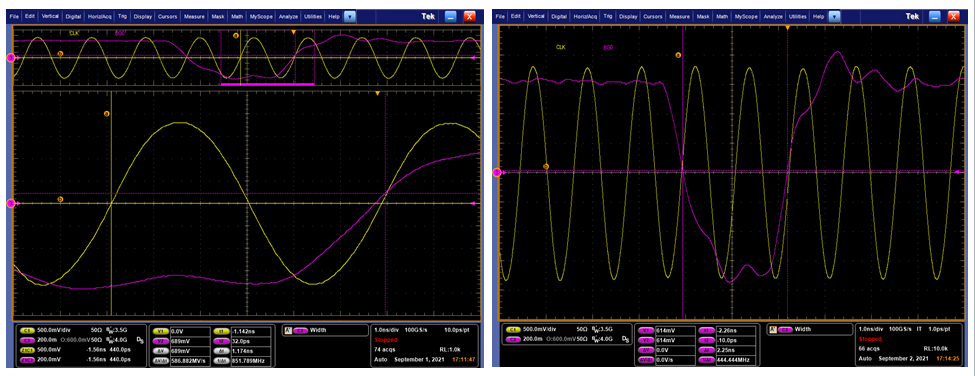

CLK Timing

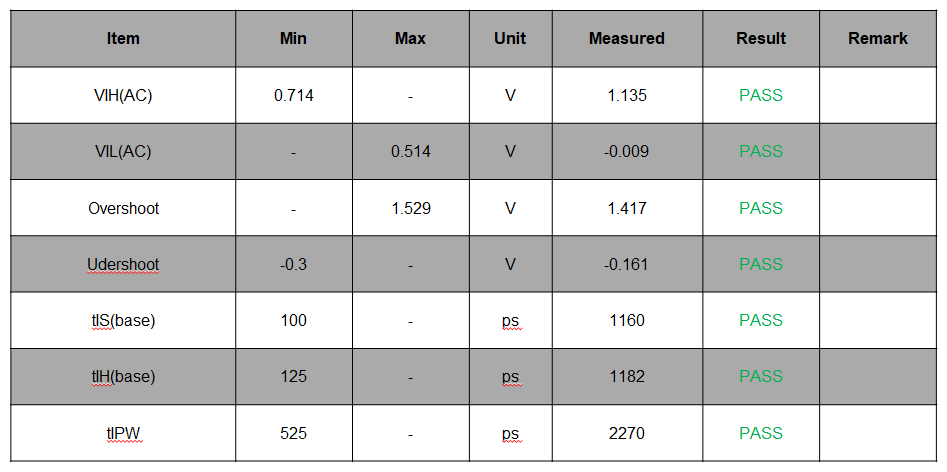

CLK Timing Test Spec?

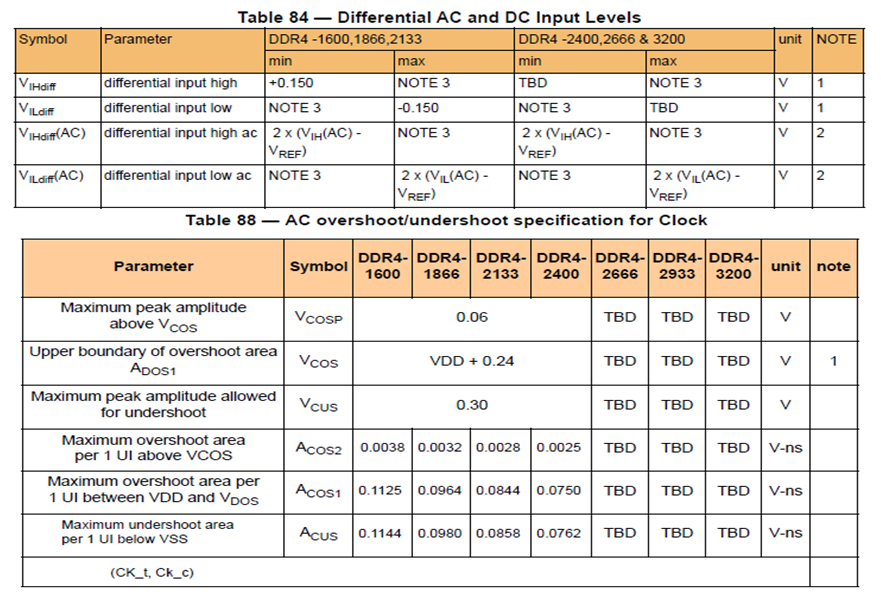

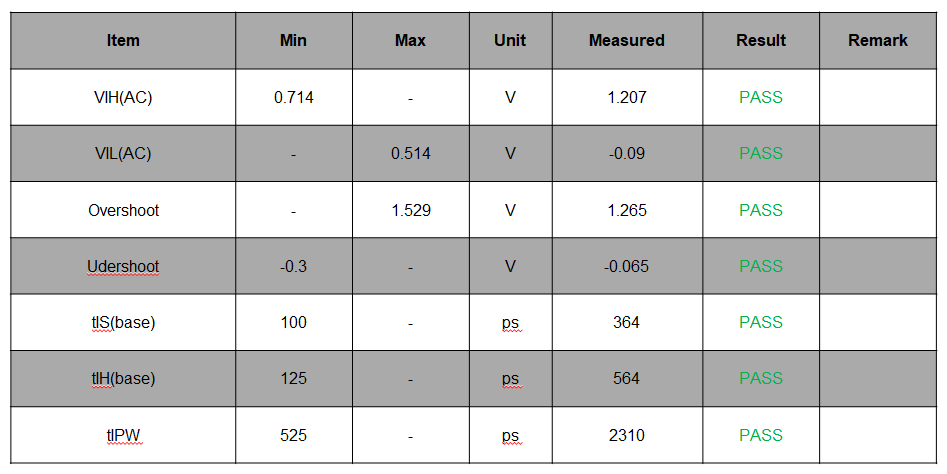

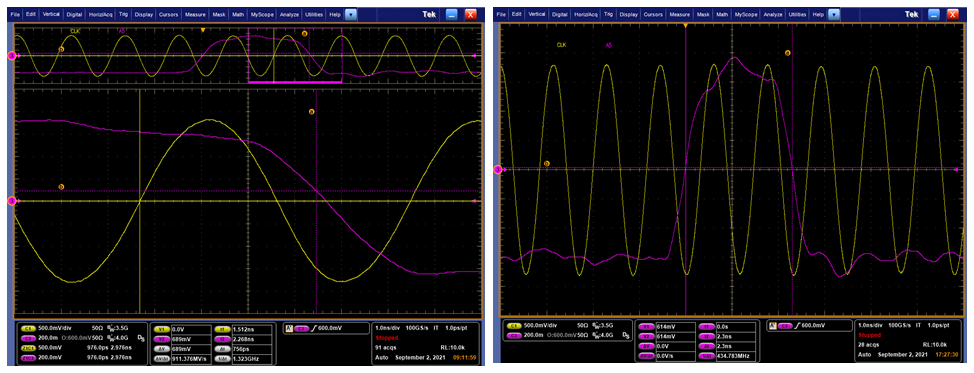

CLK Timing Test? Result?

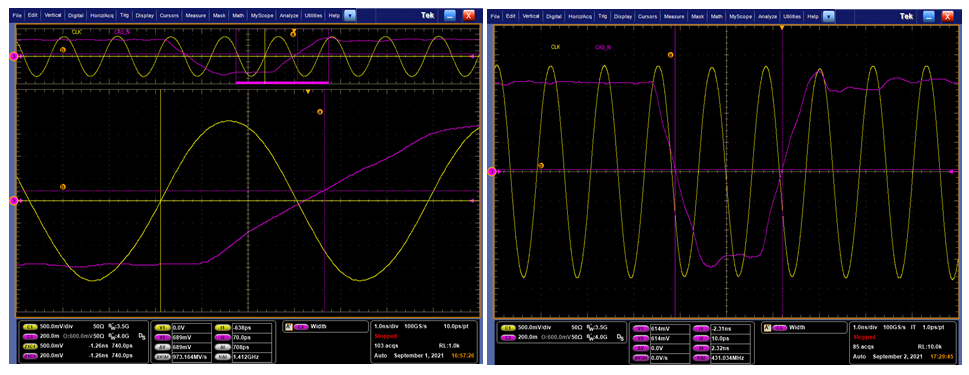

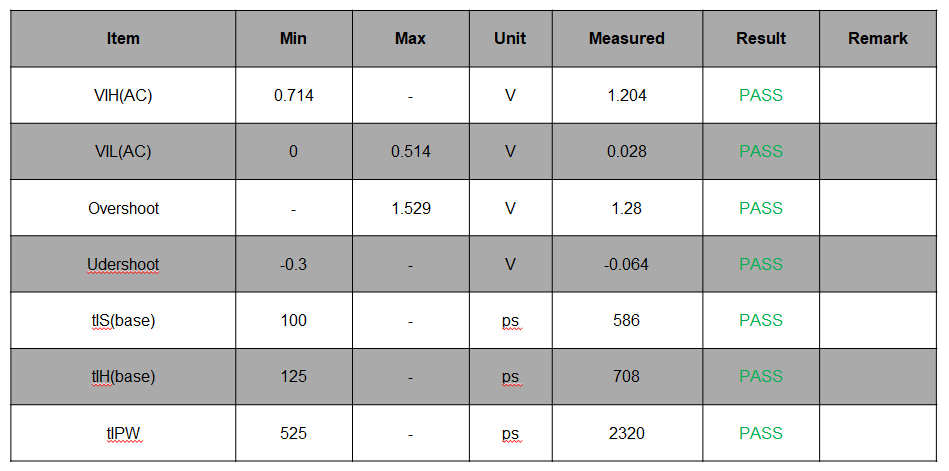

CAS_n Timing Test

CAS_n Timing Test Result?

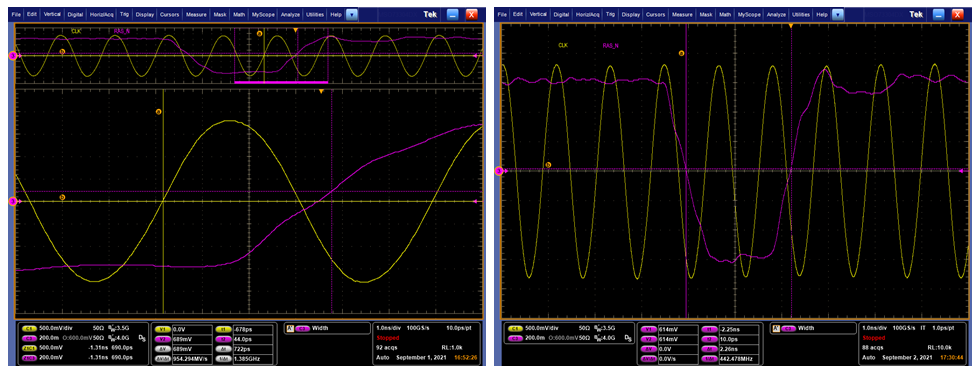

RAS_n Timing Test

RAS_n Timing Test Result?

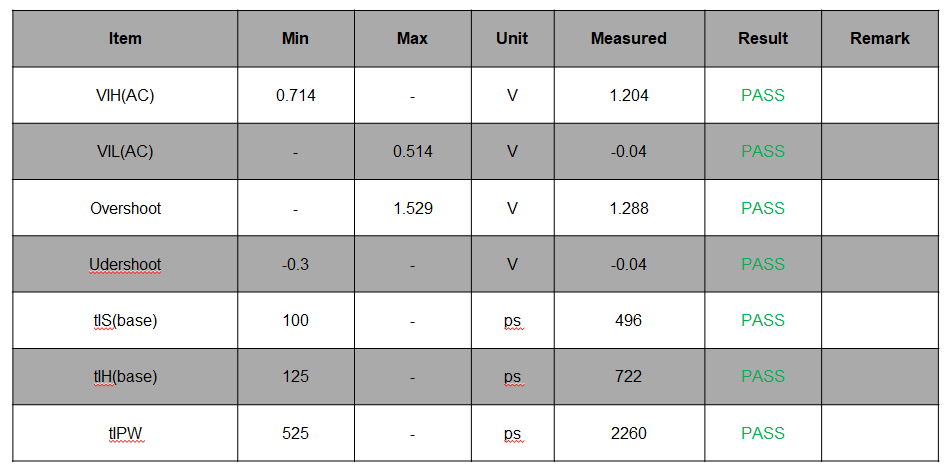

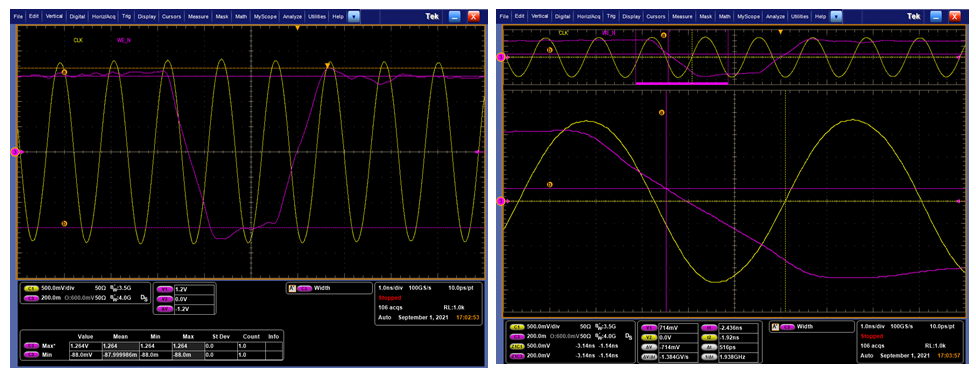

WE_N Timing Test

WE_n Timing Test Result?

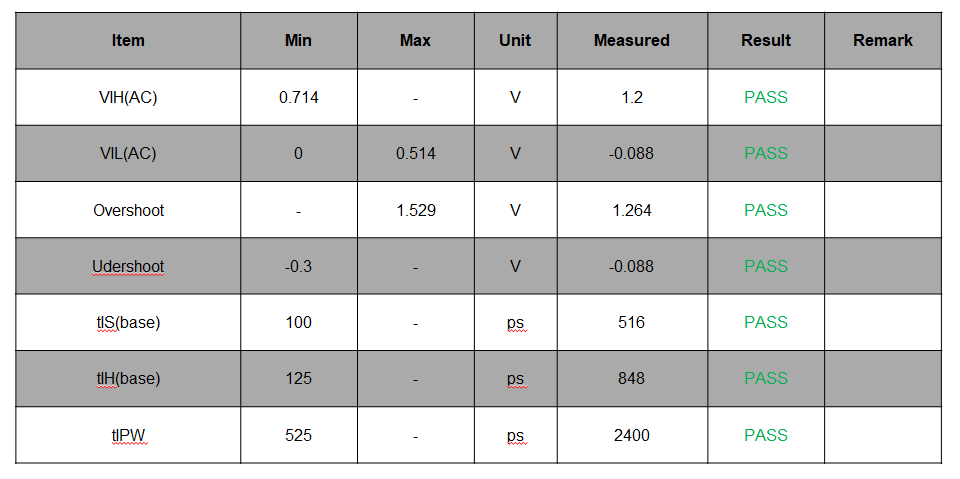

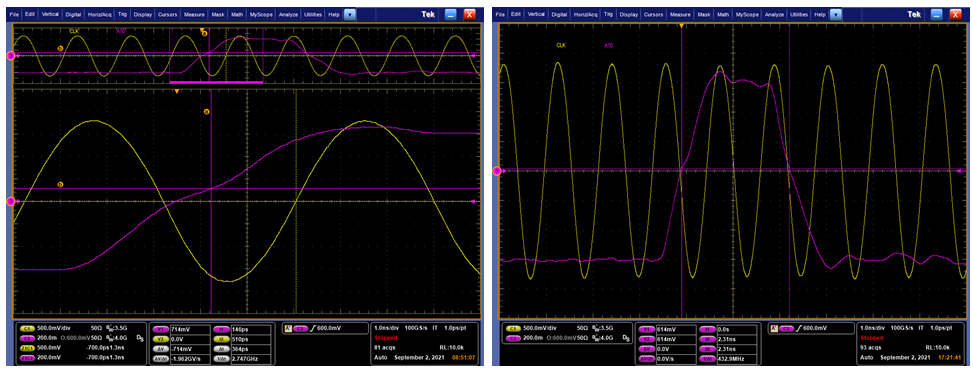

A10 Timing Test

A10 TimingTest Result?

A5 Timing Test

A5 TimingTest Result?

BA0 Timing Test

BA0 TimingTest Result

BG0 Timing Test

BG0 TimingTest Result?

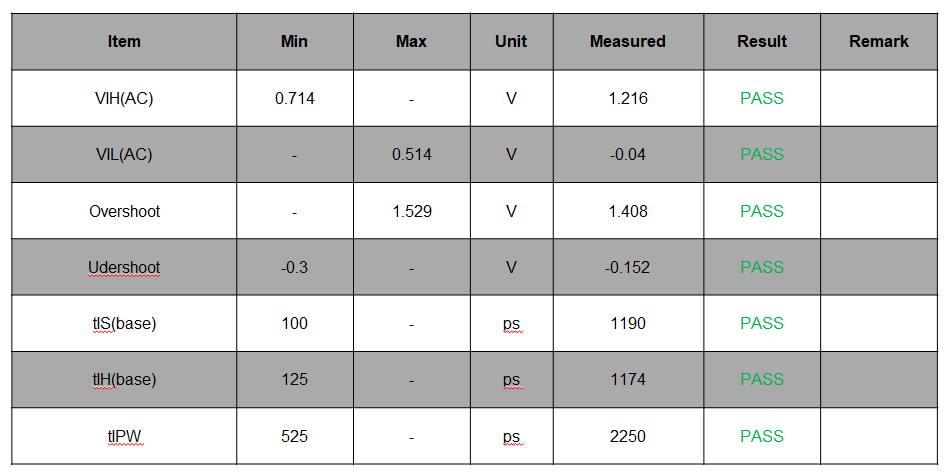

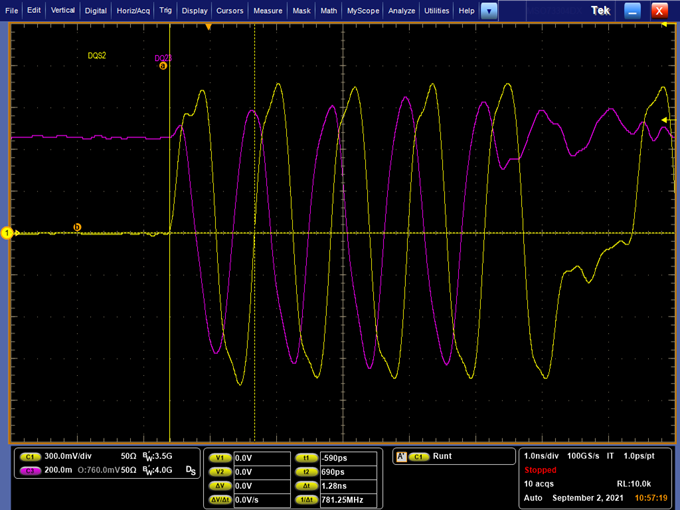

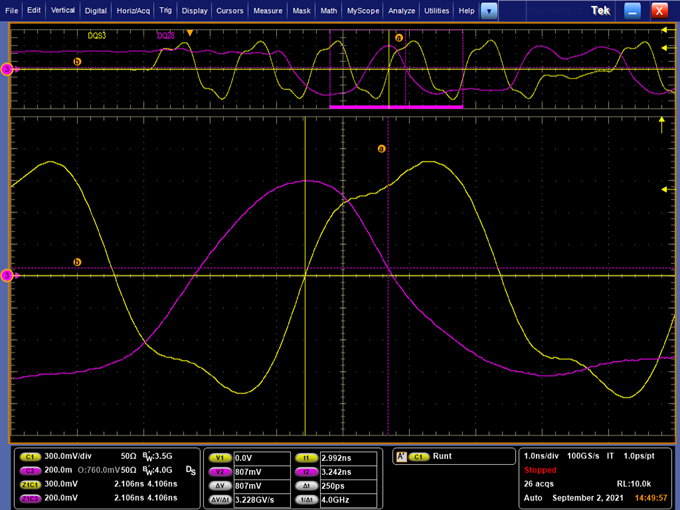

Write? Timing Test

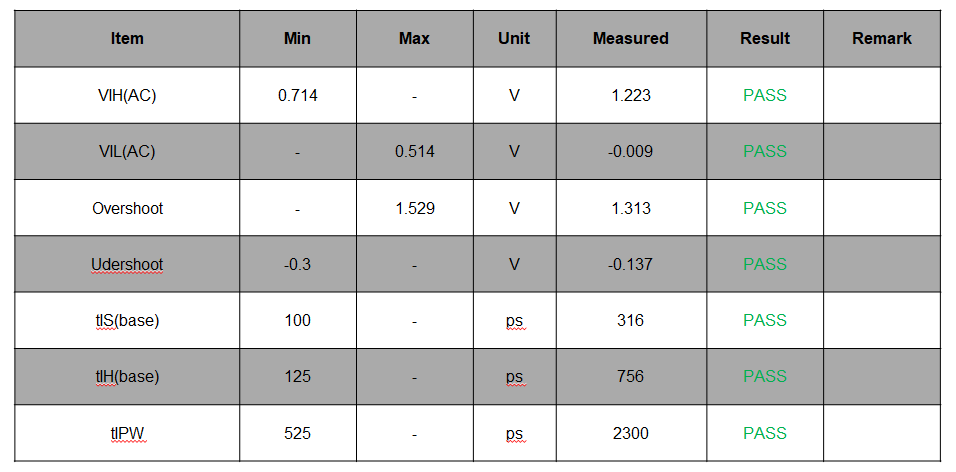

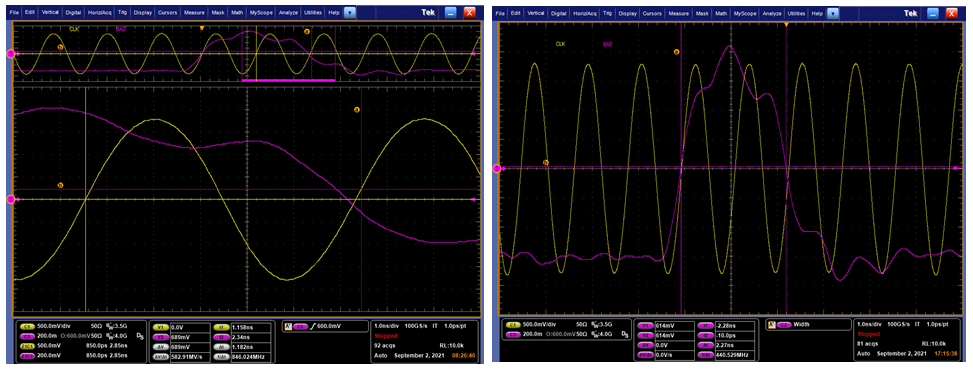

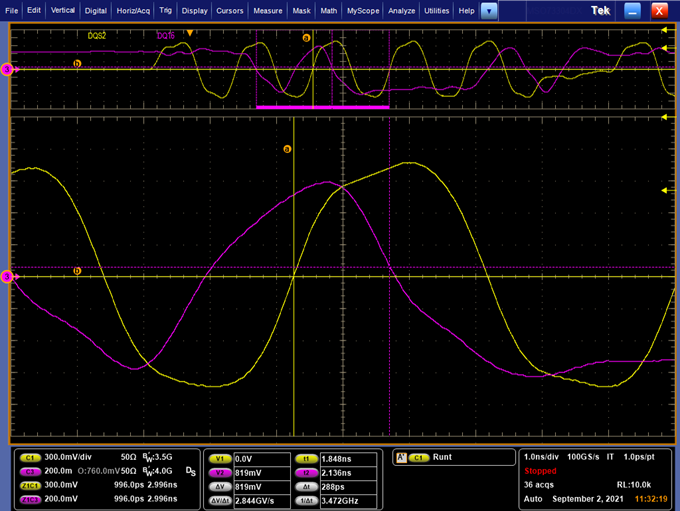

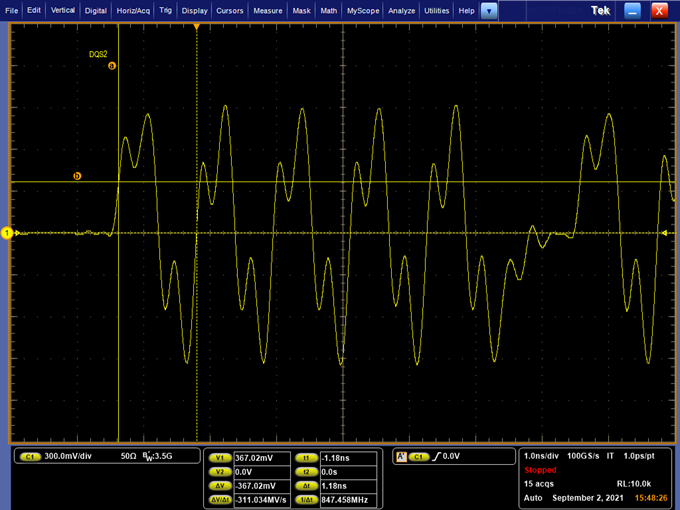

DQS2? Write? Preamble? tWPRE

DQS2 Falling Setup To From CKRising tDSS

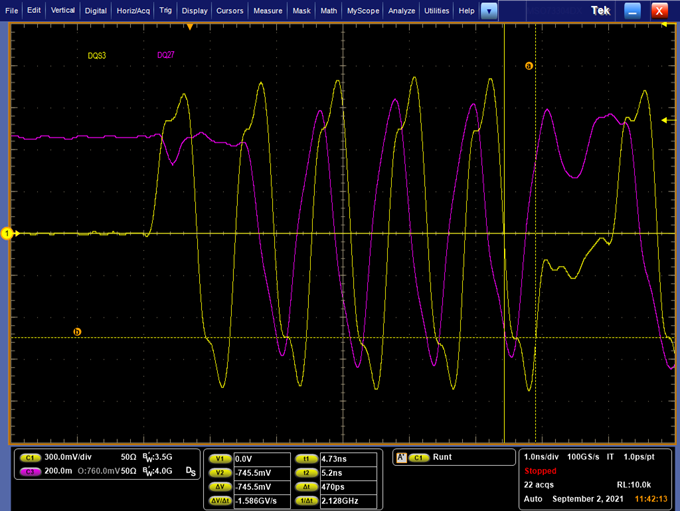

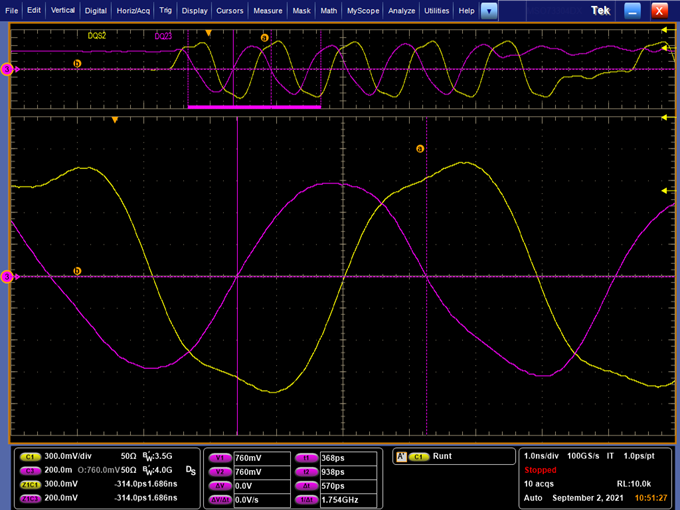

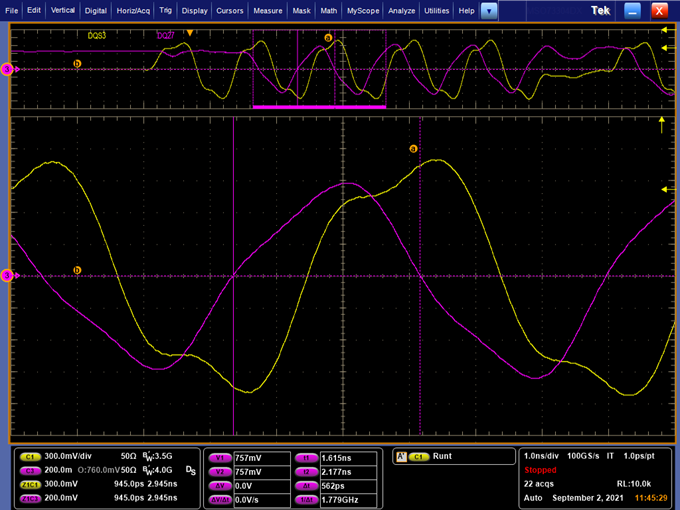

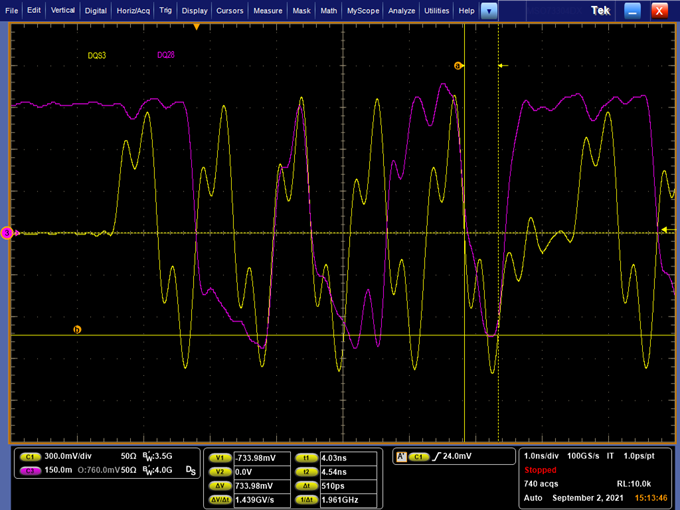

DQS3 Write Postamble tWPST

DQS3 Falling Setup Hold From CK Rising tDSH

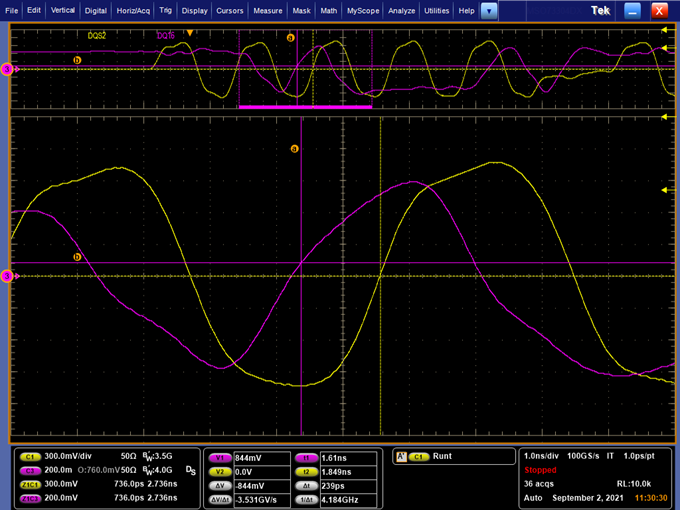

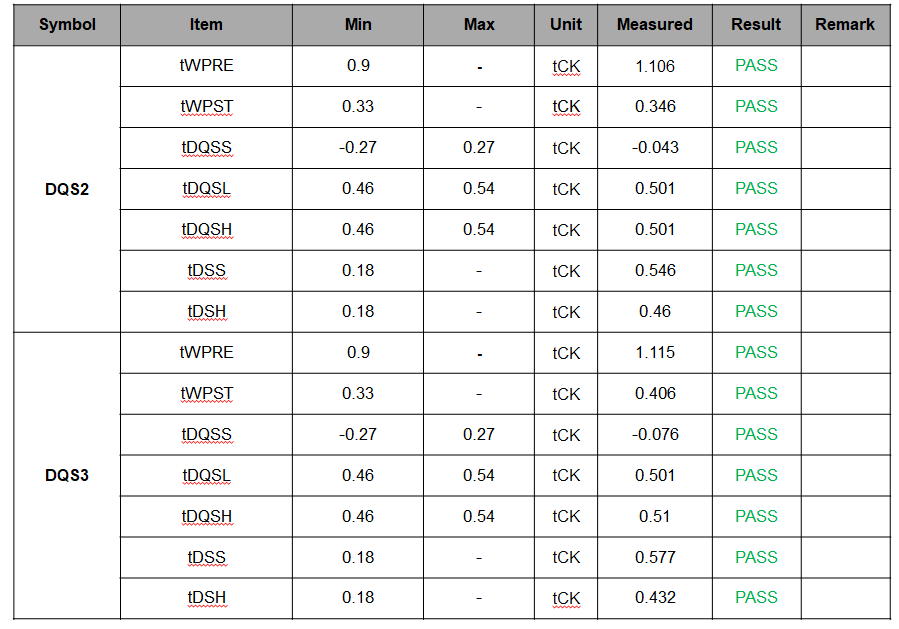

DQ16?Input Set Time tDS?

DQ16?Input Hold Time tDH

DQ23?AC Input Pules Width tDIPW

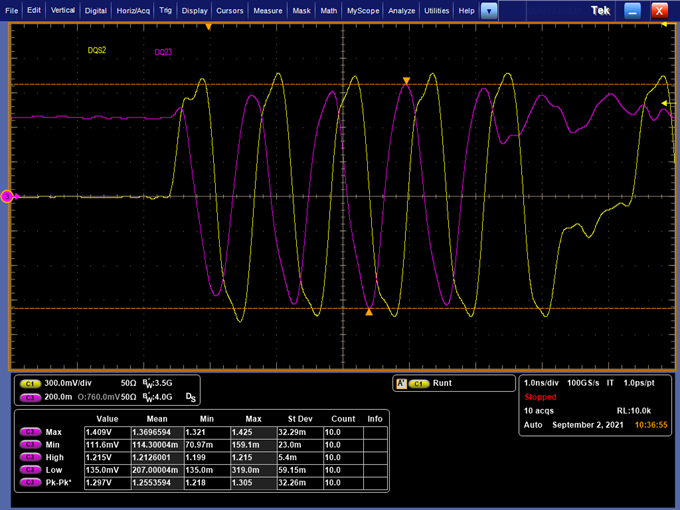

DQ23?AC input swing pk-pk

DQ27AC InputPules Width tDIPW

DQ28?Input?Set Time tDS

DQ28?Input?Hold Time tDH

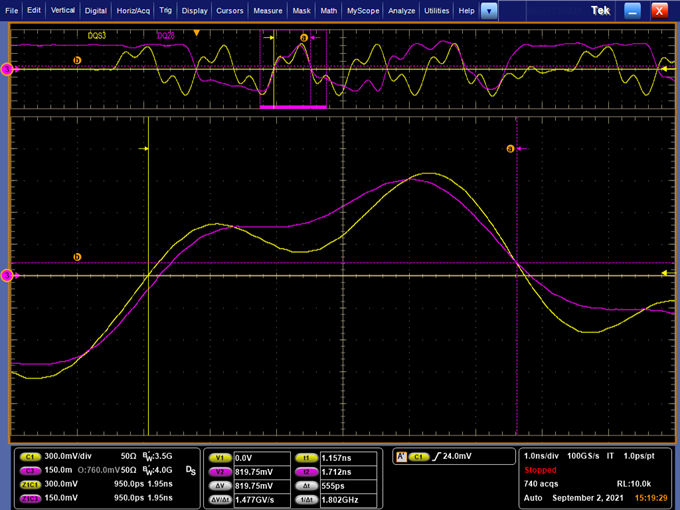

Write?Data Test?Result

Read Timing Test

DQS2 Read Preamble tRPRE

DQS3 Read Postamble tRPST

DQ16 Output Hold Time From DQS2 tQH

DQ23 Output Hold Time From DQS2 tQH

DQ27OutputHoldTime From DQS3 tQH

DQ28 Output HoldTime From DQS3 tQH

Read Data Test Result

啟威測實驗室提供DDR2/3/4/5信號完整性測試及一致性驗證。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論