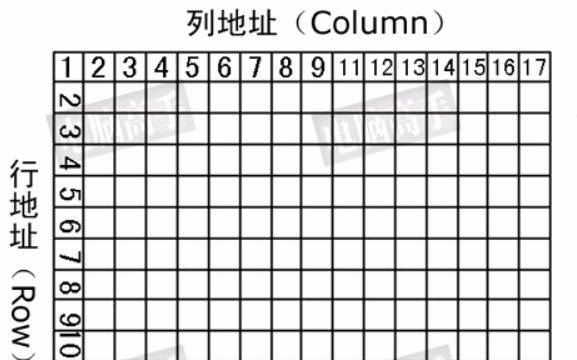

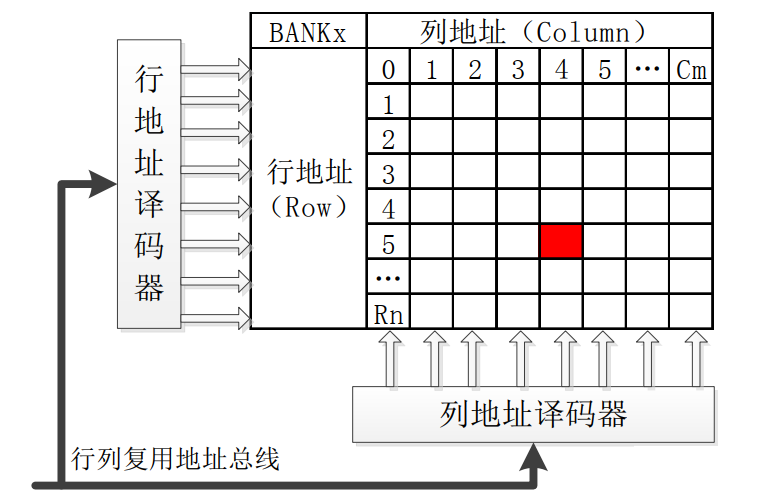

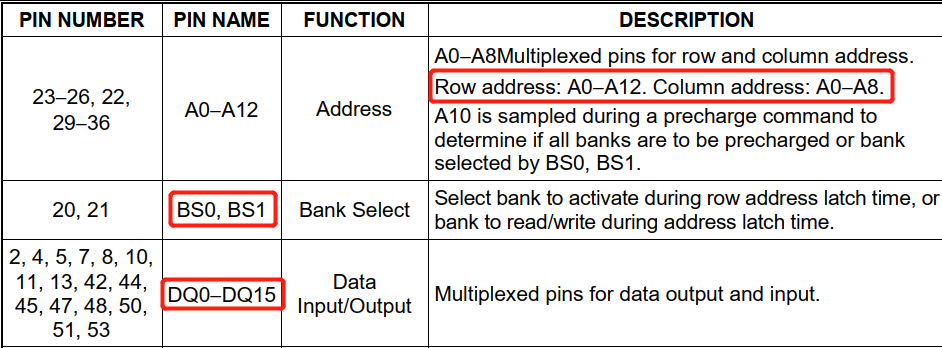

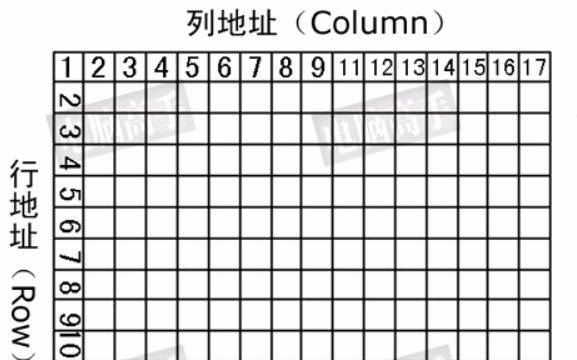

介紹SDRAM電路設計之前先了解下SDRAM的尋址原理。SDRAM內部是一個存儲陣列,可以把它想象成一個表格,和表格的檢索原理一樣,先指定行,再指定列,就可以準確找到所需要的存儲單元。

2015-01-26 09:49:53 4627

4627

初始后的SDRAM在得到了RAS、CAS、WE的值后開始執行相應的命令。在對SDRAM進行讀、寫過程中,必須要先進行頁激活ACT操作,保證存儲單元是打開的,以便從中讀取地址或者寫入地址,然后通過

2020-07-07 08:00:00 2373

2373

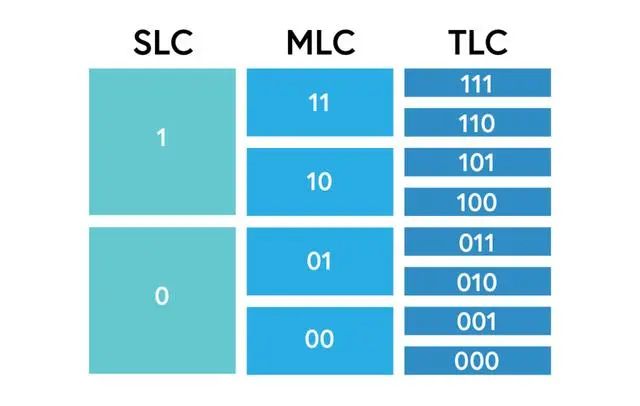

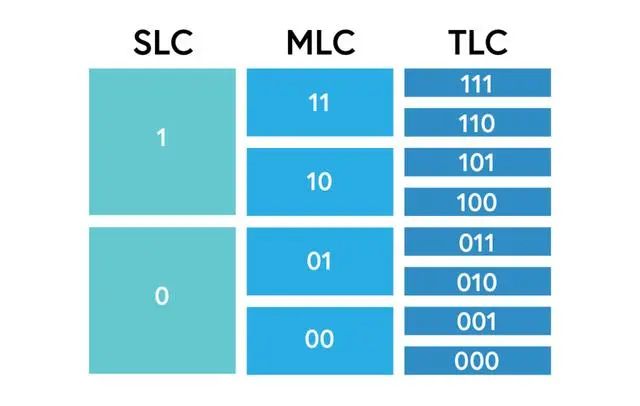

就基本的 SSD 存儲單元而言,有 SLC、MLC、TLC 和 QLC。其中,TLC 是最受歡迎的,不過,QLC 最終將取代它們。在 I/O 方面,有 SATA 和 NVMe。

2022-08-26 16:41:35 3275

3275

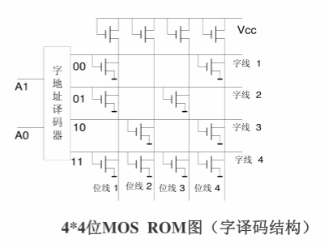

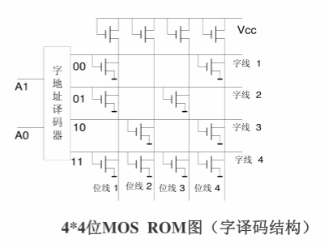

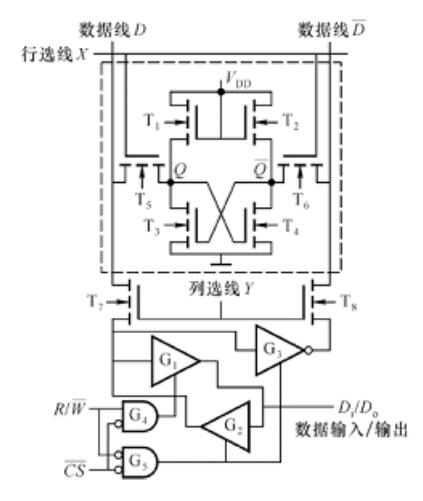

地址譯碼器根據地址信號總線,選中相應的存儲單元。假設譯碼器有j條地址輸入線,則可以尋址2的j次方個存儲器單元,則存儲矩陣由2的j次方個存儲器單元組成,每個存儲單元為k位。

2022-10-18 17:08:18 4345

4345

在芯片設計時,通常需要用到各種類型的存儲單元,用以臨時或者永久地存儲數據。根據應用場合的不同,所用到的存儲單元也不同。本文對常見的幾個存儲單元進行了介紹,并簡述了其工作原理和特點。需要特別說明

2022-12-02 17:36:24 1953

1953

牛津大學設計了一種新型計算機存儲單元,可以同時通過電和光信號對其進行訪問或寫入,大幅度提升了帶寬和功率效率,也進一步推動了芯片級光子學技術的發展。

2020-01-21 08:38:00 1375

1375 80C51單片機片內RAM低128個存儲單元劃分為哪4個主要部分?各部分主要功能是什么?

2011-10-08 16:10:02

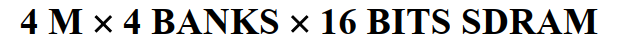

SDRAM有4個Bank,也就是相當于有4張這樣的表格。所以SDRAM的容量計算方式為:SDRAM容量 = 數據位寬 x 存儲單元數量(行地址 x 列地址 x Bank數)二、SDRAM引腳介紹講

2018-03-26 14:35:04

存儲位元與存儲單元是什么含義?數據通信的方式可以分為哪幾種呢?

2022-01-21 07:17:58

設存儲器讀/寫周期為 0.5us, CPU在1us內至少要訪問一次。試問采用哪種刷新方式比較合理? 兩次刷新的最大時間間隔是多少? 對全部存儲單元刷新遍所需的實際刷新時間是多少?

2021-10-26 07:05:19

1、一些概念:(1)存儲容量存儲器多能存儲的二進制信息的總位數存儲容量 = 存儲器總存儲單元數*每個存儲單元的位數(2)存儲器的速度①存取時間:對存儲器中某一個單元的數據進行一次存(取)所需要的時間

2021-12-09 06:31:47

都有頁模式。SDRAM是其中的一種。SDRAMSDRAM(Synchronous DRAM,同步動態隨機存儲器),即數據的讀寫需要時鐘來同步。其存儲單元不是按線性排列的,是分頁的。DRAM和SDRAM

2012-08-15 17:11:45

芯片。這時得到了4個 字長為4得芯片,這四個芯片按字方向擴展得到16K,說明一塊DRAM芯片存儲單元數位4K.而刷新是針對每塊芯片來說的,所以我們只需要研究一塊芯片的刷新機制按照存儲矩陣形式,得到共有

2022-03-02 06:18:45

1.(判斷題)DRAM上電時存儲單元的內容是全0,而Flash上電時存儲單元的內容是全1。(4分) A.正確B.錯誤 FLASH可保存 上電后不知道是啥2.(判斷題)眼圖可以用來分析高速信號的碼間

2021-07-22 08:57:49

判斷題:DRAM上電時存儲單元的內容是全0,而Flash上電時存儲單元的內容是全1

2017-08-23 09:29:31

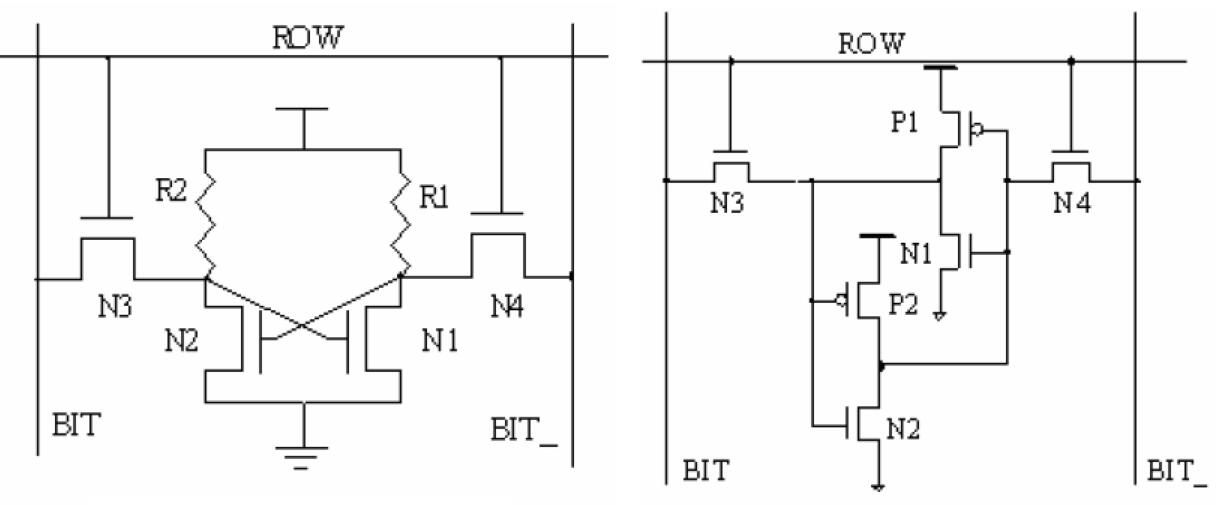

方式邊界對齊的數據存放方法主存的基本結構和工作過程存儲系統的層次結構半導體存儲器靜態MOS存儲器 SRAM靜態MOS存儲單元靜態MOS存儲器的結構動態MOS存儲器 DRAM四管動態MOS存儲元的工作原理

2021-07-28 07:59:20

Nand Flash的物理存儲單元的陣列組織結構Nand flash的內部組織結構,此處還是用圖來解釋,比較容易理解:圖2.Nand Flash物理存儲單元的陣列組織結構[url=][img=1,0

2018-06-12 10:10:18

請教Arm專家大俠: SOC內SRAM各存儲單元, 其“每次上電冷啟動后、還未寫入應用數據前的初始狀態數據”是否是由其硬件電路保證總是一樣的(全0或全1)?不會隨機變化(有時為0有時為1)? 能否從硬件原理角度簡單說明下? 謝謝。

2022-08-19 15:37:40

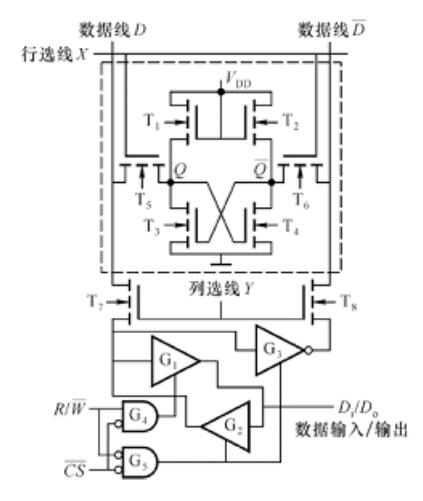

同時有4個或8個存儲單元按上述方法被選中進行讀寫操作。在SRAM 中,排成矩陣形式的存儲單元陣列的周圍是譯碼器和與外部信號的接口電路。存儲單元陣列通常采用正方形或矩陣的形式,以減少整個芯片面積并有利于數據

2022-11-17 14:47:55

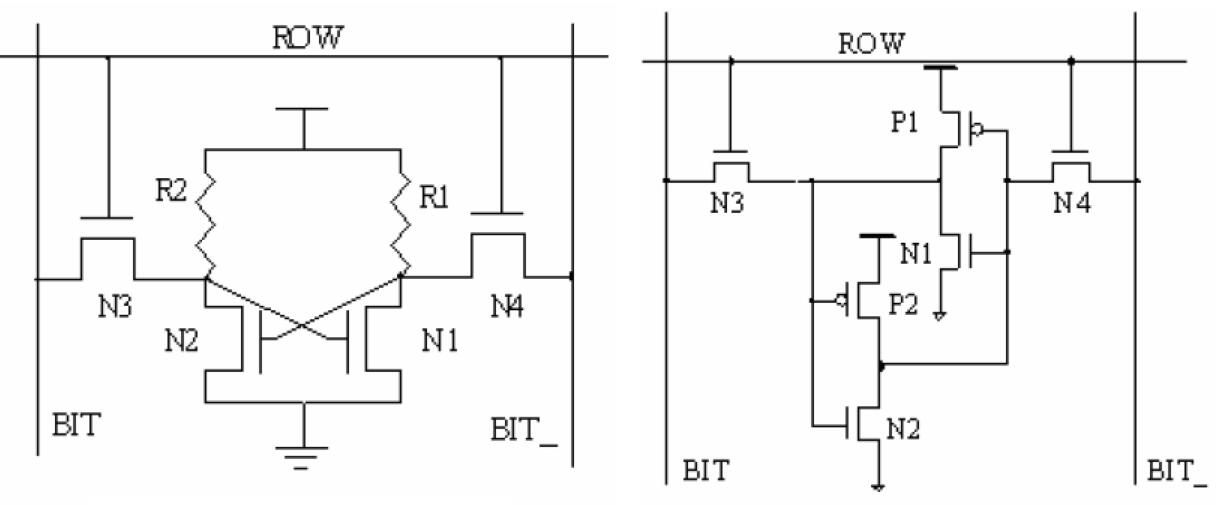

靜態RAM的基本構造塊是SRAM存儲單元。通過升高字線的電平觸發存儲單元,再通過位線對所觸發的存儲單元進行讀出或寫入。在靜態CMOS存儲器中,存儲單元陣列將會占去整個存儲器芯片面積的一半以上,在一些

2020-06-05 15:18:24

niosii編譯提示on-chip menmory 存儲單元不夠,怎么解決?

2015-01-18 09:31:43

SDRAM的內容結構,就如同Excel的表格:其中的一個小表格就是SDRAM內部的一個存儲單元,而要確定這個存儲單元的為止,只需要知道行地址(rowaddress)和列地址(coladdress)就可以了

2017-05-08 22:20:54

就對應了另外一個地址了。圖3是隨意舉了個例子(不要與ARM芯片對應),旨在說明地址重映射的過程。圖3表示把0x00000000地址上的存儲單元映射到新的地址0x00000007上。CPU存取

2022-05-23 15:03:37

主存中存儲單元地址是如何進行分配的?存儲芯片的容量有多大?

2021-10-19 08:25:52

4.2.1.主存中存儲單元地址的分配:存儲字長:存儲器中一個存儲單元(存儲地址)所存儲的二進制代碼的位數,即存儲器中的MDR的位數。字(word) : 若干個字節組成一一個”字” ( word)。一

2021-07-28 06:43:06

本帖最后由 elecfans電子發燒友 于 2018-1-2 21:02 編輯

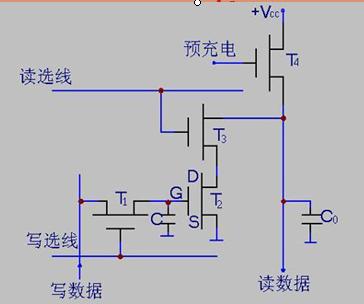

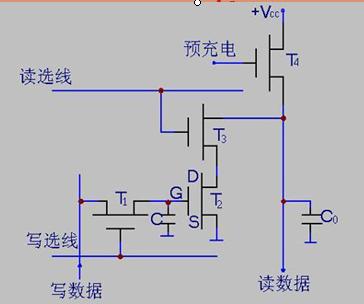

自己動手搭建電路可以發現許多有趣的東西。今天為大家帶來的是“靜態存儲單元”及其“寫控制電路”的搭建。 “靜態

2017-01-08 12:11:06

在分析傳統SRAM存儲單元工作原理的基礎上,采用VTC蝴蝶曲線,字線電壓驅動,位線電壓驅動和N曲線方法衡量了其靜態噪聲容限。 在這種背景下,分析研究了前人提出的多種單元優化方法。這些設計方法,大部分

2020-04-01 14:32:04

你好如何在不使用DDR內存控制器的情況下設計FPGA BRAM(或任何其他內存模塊_SD,DDR以外的本地等)大容量存儲單元?當我通過示例設計“VC707_bist”替換DRAM控制器和BRAM

2019-04-04 15:10:55

怎么把單片機存儲單元清0或置1?

2023-10-16 07:59:42

分為靜態隨機存儲器(SRAM)、動態隨機存儲器(DRAM)及SDRAM。1個SRAM單元通常由4~6個晶體管組成,當這個SRAM單元被賦予O或者1的狀態之后,它會保持這個狀態直到下次被賦予新的狀態或者

2020-08-12 00:00:00

怎么隨機存取存儲器ram中的存儲單元

2023-09-28 06:17:04

畫中畫的效果。在調試DDR3的過程中,我有一些高速存儲器的使用心得,特分享給大家。首先我先介紹一下SDRAM存儲器的讀寫時序。SDRAM即同步動態隨機存儲單元,主要用來存儲較大容量的數據。我們都知道,數據

2020-01-04 19:20:52

是SDRAM尋址的基本原理。如圖 33.1.1所示:圖 33.1.1 SDRAM尋址原理圖 31.1.1中的“單元格”就是SDRAM存儲芯片中的存儲單元,而這個“表格”(存儲陣列)我們稱之為L-Bank

2020-08-17 15:25:11

概述:AT24C08是ATMEL公司出品的一款8192位的串行電可擦寫可編程只讀存儲器(EEPROM),每個存儲單元有1024字,每個字為8位。AT24C08系列芯片采用8引腳PDIP,8引腳JEDEC SOI

2021-04-06 08:35:58

/DDR/DDR2芯片的datasheet細細比對,也許用這篇文比較也無法完全說明白他們的迥異,但是至少特權同學希望通過這篇文章能夠讓大家對他們之間的區別有一個大概的認識,尤其一樣對SDR SDRAM

2014-12-30 15:22:49

確定一個存儲單元,每個存儲單元里面就是我們的數據了,我們的芯片是16位的,所以我們的存儲單元也就是16位的。這樣一來,CPU通過片選信號選中一片SDRAM,然后訪問某一個L-bank,通過行列地址確定

2015-03-19 17:05:19

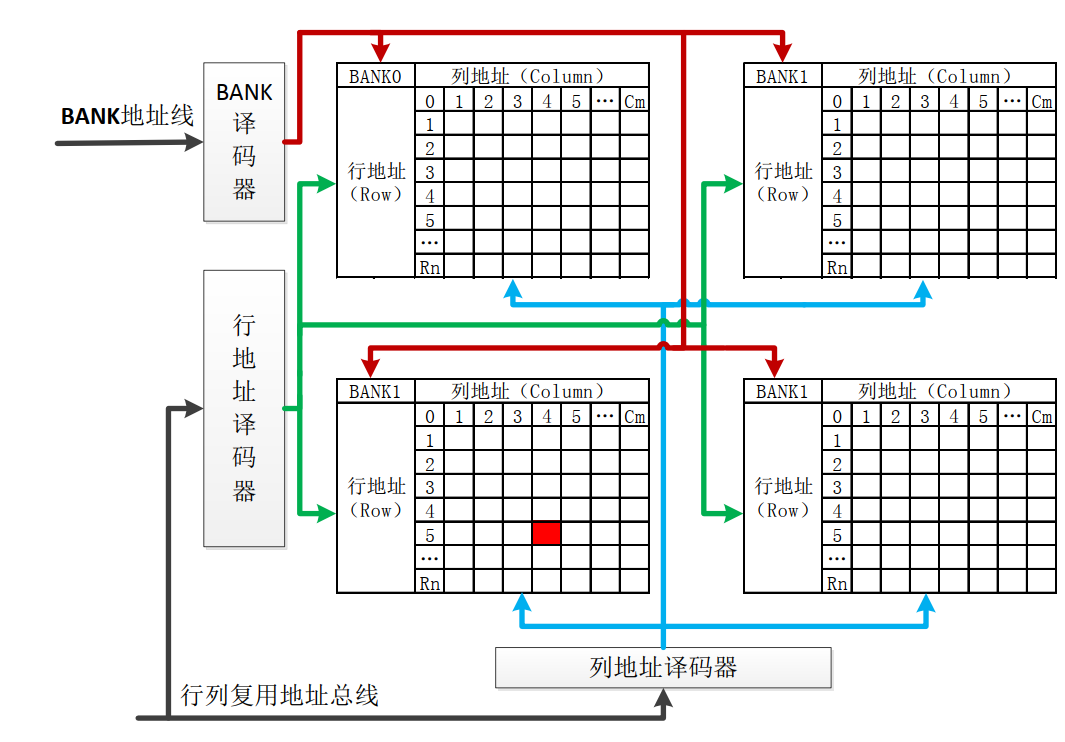

高速SDRAM存儲器接口電路設計SDRAM可作為軟嵌入式系統的(NIOSII)的程序運行空間,或者作為大量數據的緩沖區。SDRAM是通用的存儲設備,只要容量和數據位寬相同,不同公司生產的芯片都是兼容

2019-06-03 05:00:07

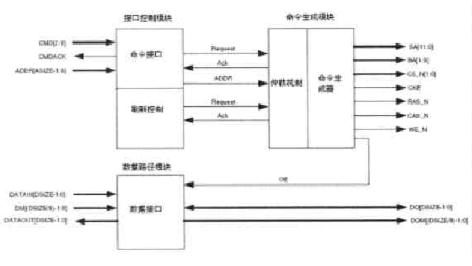

提出了一種在HDTV SOC 系統中實現多模塊共享存儲單元的高效SDRAM 控制器。通過利用合理的請求仲裁、Full Page 讀寫、指令與數據分離、指令緩存和前后相關處理等機制,實現了高吞吐

2009-08-14 16:09:14 13

13 SDRAM設計詳細說明

完成SDRAM的上層驅動設計,對SDRAM讀寫、管理無誤,與其他模塊的接口正確。

口令:MMCTEAM

SDRAM的工作原理

2010-04-22 14:02:57 0

0 SDRAM幀存儲器部分電路

2010-05-07 18:41:54 21

21 對第一代開關電流存儲單元產生的時鐘饋通誤差做了合理的近似分析,設計了一種高性能開關電流存儲單元。該電路僅在原存儲單元的基礎上增加了一個MOS管,使誤差降為原來的4%,

2010-07-05 14:50:48 22

22 存儲器的分類

內部存儲器的系統結構

動、靜態讀寫存儲器RAM的基本存儲單元與芯片

2010-11-11 15:35:22 67

67 低電壓甲乙類開關電流存儲單元

引言 開關電流存儲單元是電流模式采樣數據信號處理系統的基本單元電路,其性能的優

2007-08-15 16:06:29 563

563 三態MOS動態存儲單元電路

2009-10-10 18:45:49 1213

1213

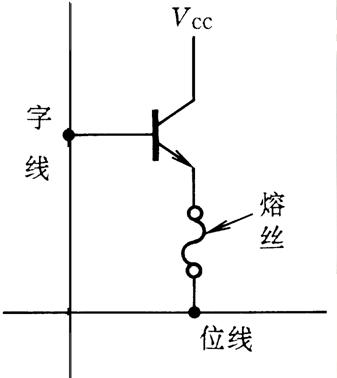

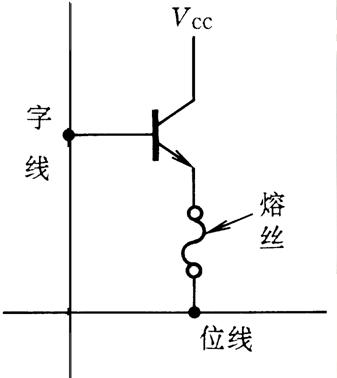

熔絲型PROM的存儲單元

2009-12-04 12:25:26 2228

2228

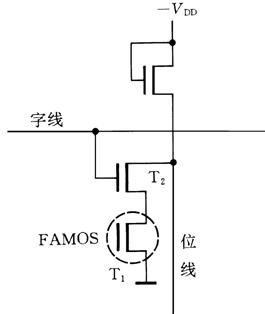

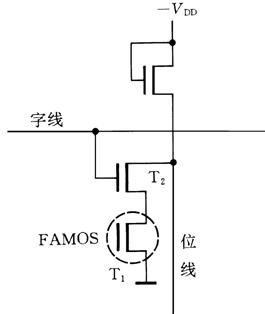

使用FAMOS管的存儲單元

2009-12-04 12:27:29 875

875

E2PROM的存儲單元

2009-12-04 13:03:57 1468

1468 E2PROM存儲單元的三種工作狀態

2009-12-04 13:04:45 1334

1334 六管NMOS靜態存儲單元

2009-12-04 15:30:03 6567

6567 四管動態MOS存儲單元

2009-12-04 16:34:14 2284

2284 單管動態MOS存儲單元

2009-12-04 16:50:24 3757

3757 RAM RAM是指通過指令可以隨機的、個別的對各個存儲單元進行訪問的存儲器,一般訪問時間基本固定,而與存儲單元地址無關。RAM的速度比較快,但其保存的信息需要電力支持,一旦丟失

2011-08-25 18:02:19 8706

8706 一種面向多核系統的DDR2SDRAM控制單元_章裕

2017-01-03 18:00:37 5

5 應用于超低電壓下的SRAM存儲單元設計_劉冰燕

2017-01-07 21:39:44 0

0 使用賽道存儲單元的近閾值非易失SRAM_孫憶南

2017-01-07 21:45:57 1

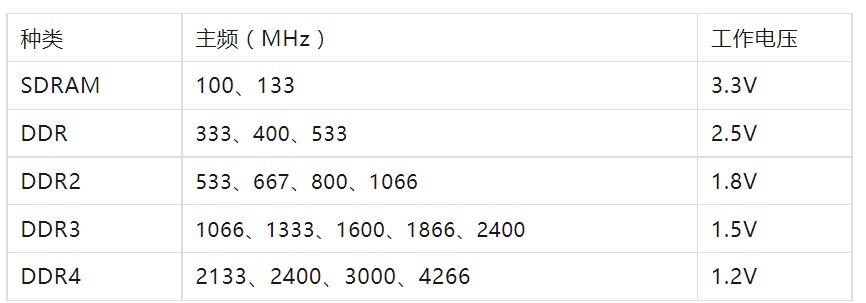

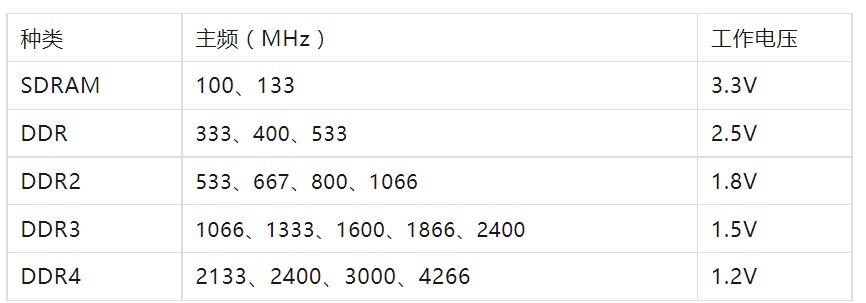

1 記憶技術不停滯不前。存儲器結構的變化速度更快和更有效的結構的創建和使用在連續幾代人如DRAM SDRAM DDR DDR1、2、3、等。

2017-06-06 14:22:11 5

5 IS42S16400是ISSl公司推出的一種單片存儲容量高達64 Mb(即8 MB)的16位字寬高速SDRAM芯片。SDRAM的主要特點是:①同

2017-10-23 10:48:11 1

1 。O工P存儲器的種類很多,很多是基于熔絲和反熔絲,本文介紹的O工P存儲器基于反熔絲結構。在反熔絲O工P存儲器中,通過對選中單元的編程改變了存儲單元內部的結構。理想的讀機制下,沒有編程的存儲單元讀取時會讀出0,而通過編程的存儲單元在讀取時會讀出1。反

2017-11-07 11:45:21 11

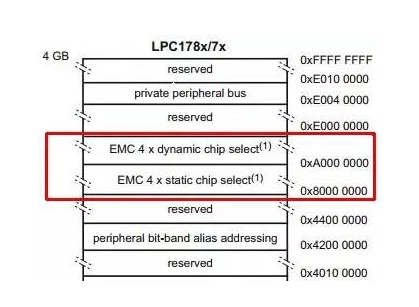

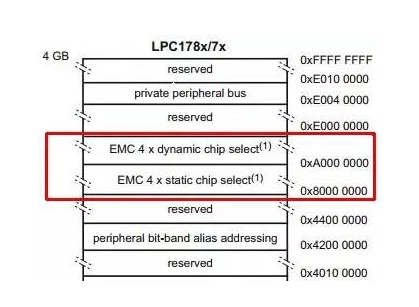

11 EMC與外部的動態存儲器相連時,其占用的地址線相對來說是比較少的,這還是跟動態存儲器的這種存儲結構是有一定關系的。就拿SDRAM來說,其內部存儲是按行列分布的,如下圖所示,就像表格一樣,有對應的行地址和列地址,每一個小方格就是一個存儲單元。

2018-05-08 17:38:00 6385

6385

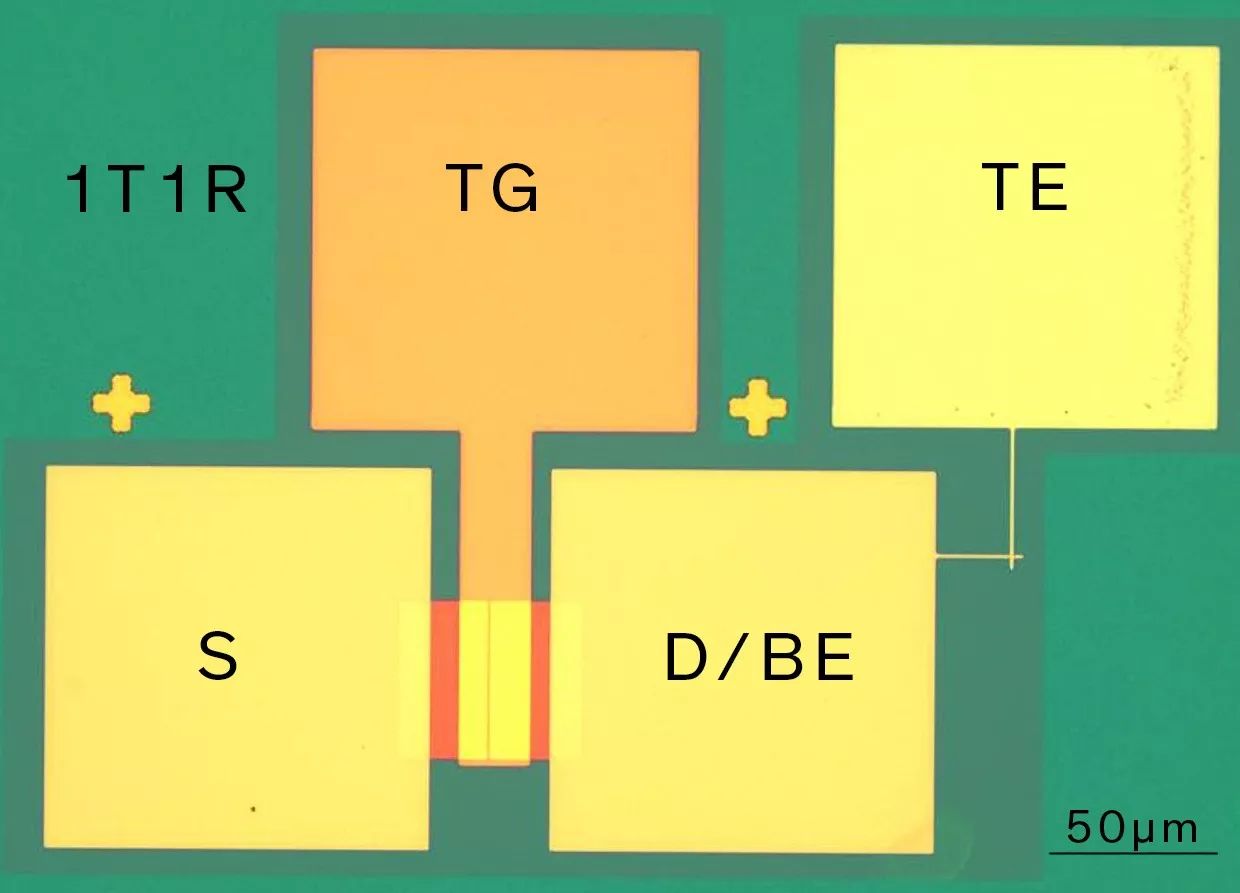

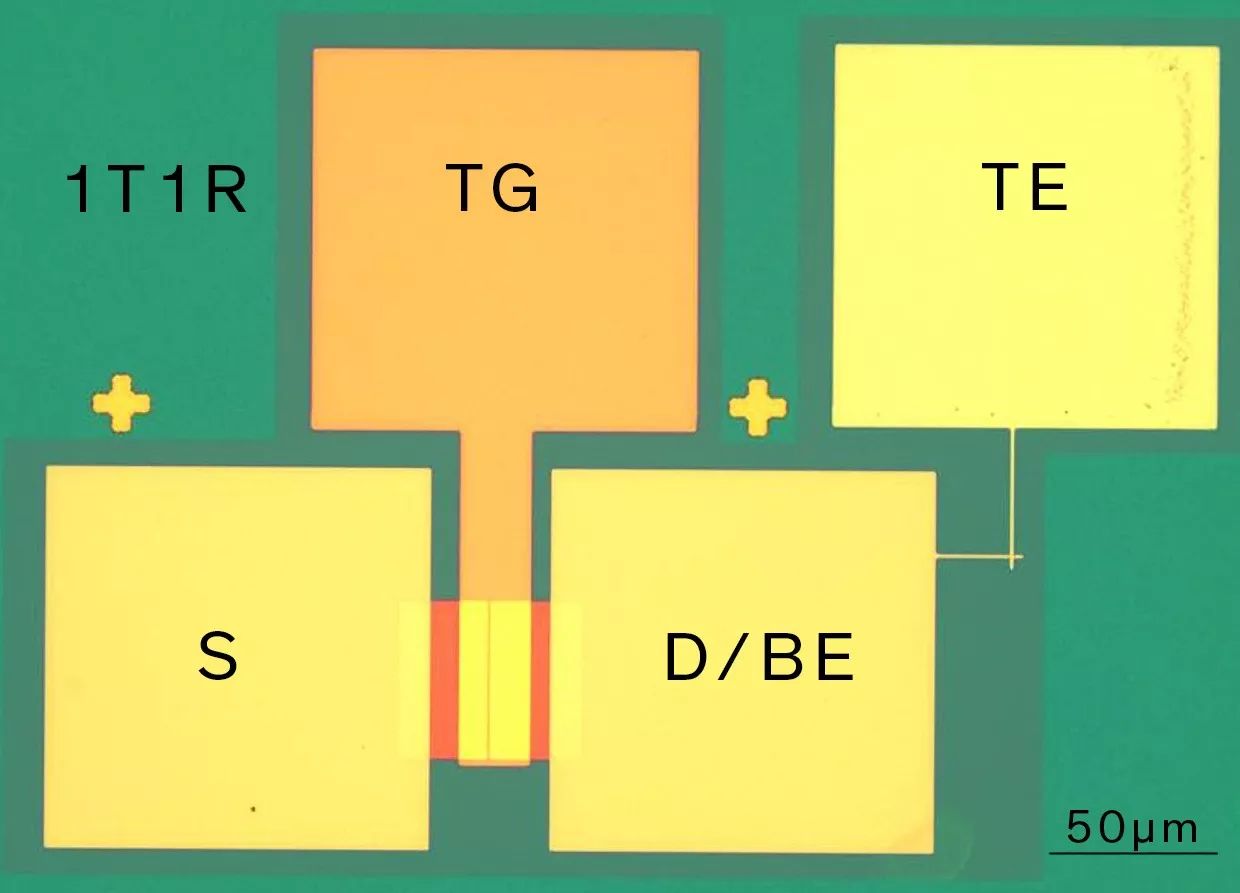

斯坦福研究人員開發的芯片被稱為“單晶體管單阻變存儲器”(1T1R)單元。這種1T1R存儲單元相對于含有阻變存儲器但沒有晶體管的存儲單元,能夠提供極大好處。

2018-01-23 17:23:59 6482

6482

介紹SDRAM電路設計之前先了解下SDRAM的尋址原理。SDRAM內部是一個存儲陣列,可以把它想象成一個表格,和表格的檢索原理一樣,先指定行,再指定列,就可以準確找到所需要的存儲單元,這是內存芯片

2018-06-11 17:11:00 3659

3659

SDRAM存儲器相關資料下載

2018-05-02 11:46:57 49

49 存儲單元數量=行數*列數(得到一個L-Bank的存儲單元數量)*L-Bank的數量也可用M*W的方式表示芯片的容量,M是該芯片中存儲單元的總數,單位是兆(英文簡寫M,精確值是1048576),W代表每個存儲單元的容量,也就是SDRAM芯片的位寬,單位是bit;

2018-06-19 09:37:49 5353

5353

東芝公司近日發布了BENAND產品。該產品基于單層存儲單元(SLC)NAND閃存,并且內嵌錯誤糾正功能(ECC)。BENAND產品正式批量生產的時間為2012年3月。BENAND在東芝公司最先

2018-10-08 17:11:00 1940

1940 SDRAM是同步動態隨機存取存儲器的縮寫。在微控制器應用中,微控制器通過使用外部存儲控制器(EMC)操作訪問SDRAM ,SDRAM時鐘頻率通常為100MHz或133MHz。

2019-11-23 11:38:01 6043

6043

鎧俠株式會社(Kioxia Corporation)宣布開發出創新的儲存單元結構“Twin BiCS FLASH”。該結構將傳統3D閃存中圓形存儲單元的柵電極分割為半圓形來縮小單元尺寸以實現高集成化。

2019-12-24 17:01:22 3210

3210 采用單端(Single-Ended)時鐘信號,第二代、第三代與第四代由于工作頻率比較快,所以采用可降低干擾的差分時鐘信號作為同步時鐘。SDR SDRAM的時鐘頻率就是數據存儲的頻率,數據讀寫速率

2020-04-03 16:04:01 1489

1489 存儲單元的作用:可以進行讀寫操作以及存放數據。

2020-03-22 17:34:00 4034

4034 靜態RAM的基本構造塊是SRAM存儲單元。通過升高字線的電平觸發存儲單元,再通過位線對所觸發的存儲單元進行讀出或寫入。在靜態CMOS存儲器中,存儲單元陣列將會占去整個存儲器芯片面積的一半以上,在一些

2020-05-14 09:19:47 3282

3282

個名為Row Hammer的頑固安全漏洞。 Spin Memory的垂直環繞柵晶體管可以縮小MRAM和RRAM存儲單元。 Spin Memory將設備稱為通用選擇器(Universal

2020-09-04 16:10:13 2090

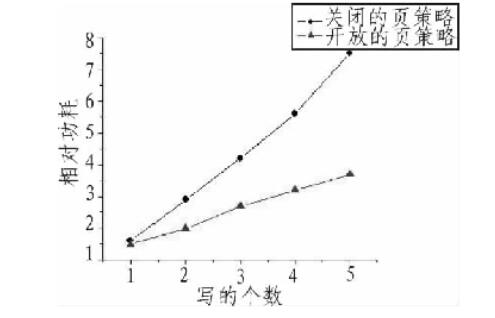

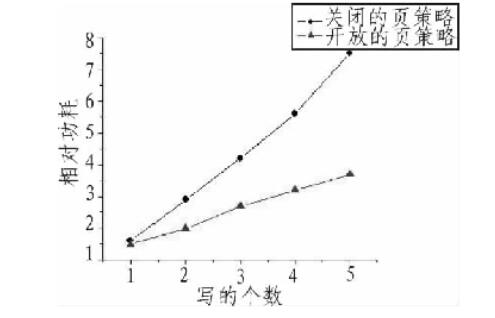

2090 器件中,SDRAM的價格低,體積小和速度快,容量大等優點而獲得大家的青睞。 SDRAM功耗來源 SDRAM內部一般分為多個存儲體,通過行、列地址分時復用,系統地址總線對不同存儲體內不同頁面的具體存儲單元進行尋址。SDRAM每個存儲體有即激活狀態和關閉狀

2020-12-02 16:36:40 758

758

按照數據存取的方式不同,ram中的存儲單元分為兩種:靜態存儲單元一靜態RAM(SRAM);動態存儲單元動態RAM(DRAM)。 1.靜態存儲單元(SRAM):它由電源來維持信息,如觸發器,寄存器

2020-12-02 14:31:30 2182

2182

該方法把邏輯上相鄰的結點存儲在物理位置上相鄰的存儲單元里,結點間的邏輯關系由存儲單元的鄰接關系來體現。

2020-12-02 10:17:55 35091

35091 器件中,SDRAM的價格低,體積小和速度快,容量大等優點而獲得大家的青睞。 SDRAM功耗來源 SDRAM內部一般分為多個存儲體,通過行、列地址分時復用,系統地址總線對不同存儲體內不同頁面的具體存儲單元進行尋址。SDRAM每個存儲體有即激活狀態和關閉狀

2020-12-06 07:41:00 1350

1350 數據必須首先在計算機內被表示,然后才能被計算機處理。計算機表示數據的部件主要是存儲設備;而存儲數據的具體單位是存儲單元;因此,了解存儲單元的結構是十分必要的。

2021-01-08 10:03:55 2269

2269 4Gb DDR3 SDRAM E-die是一個32Mbit x 16 I/Os x 8個存儲單元的設備。這種同步設備實現高速雙數據傳輸率高達2133Mb/秒/引腳(DDR3-2133)的一般

2021-01-22 08:00:00 12

12 的設計方法。結合實際系統,設計給出了使用FPGA實現 SDRAM控制器的硬件接口,在 Altera公司的主流FPGA芯片EPlC6Q240C8上,通過增加流水級數和將輸出觸發器布置在IO單元中,該控制器可達到185MHz的頻率。

2021-01-26 15:30:52 13

13 采用HSPICE分別對設計的存儲單元、延遲單元和積分器電路進行了仿真,晶體管模型選用TSMC0.18μm標準數字工藝參數。電源電壓為±1 V;輸入電流iin=40μA,信號頻率fin=100 kHz

2021-02-18 10:06:39 1450

1450

存儲體是屬于計算機系統的重要組成部分,以存儲為中心的存儲技術。存儲單元通常按字節編址,一個存儲單元為一個字節,每個字節能存放一個8位二進制數。

2022-01-03 16:17:00 8804

8804 存儲解決方案的全球領導者鎧俠株式會社(Kioxia Corporation)今天宣布發布通用閃存(UFS) 3.1版[1]嵌入式閃存設備。該設備采用了其創新的每單元4字節的四層存儲單元(QLC)技術

2022-01-20 12:26:52 233

233 OCE28V256X是一種單電壓(3.3V)、異步、rad-hard 32kbit x8內存設備,使用抗-基于保險絲的一次性可編程(OTP)存儲單元。采用了標準的1 30nm CMOS工藝用于

2022-06-08 11:22:48 1

1 中國科學院上海微系統與信息技術研究所研究員宋志棠、王浩敏組成聯合研究小組,首次利用GNR邊緣接觸制備了世界上最小的相變存儲單元器件。

2022-08-02 14:26:26 902

902 閃速存儲器(Flash Memory)又稱閃存(Flash),是一種非易失性存儲器,用存儲單元閾值的高低表示數據。浮柵(Floating Gate )場效應管(見圖5-80)是Flash存儲單元采用的主要技術。

2022-08-08 15:46:00 1076

1076 SDRAM支持多BANK,通過指定BANK號,行地址,列地址找到目標存儲單元。

2022-12-19 15:07:41 665

665 問:PICC編譯器會自己分配存儲單元到其他bank嗎?還是需要用戶來強制分配呢? 答:你需要用一個bankx限定符來分配存儲器到其他bank。例如: bank1 char fred; 這將

2023-01-22 16:30:00 448

448 內存芯片中每個單元都有以字節線和比特線組合的獨立地址。以2016年主流4GB單面8芯片內存條為例,每粒內存芯片有4G個獨立地址。

2023-04-25 10:05:08 5457

5457

,通過指定BANK號,行地址,列地址找到目標存儲單元。圖1存儲結構SDRAM信號線SDRAM內部框圖如下以W9825G6KH內部框圖舉例:圖2W9825G6KH框圖

2022-12-19 11:46:20 682

682

存儲主控芯片是一種集成電路芯片,用于控制和管理存儲設備。它負責管理多個存儲單元(如內存、固態硬盤、閃存卡等)之間的數據傳輸和存取操作。存儲主控芯片通常包括處理器、內存控制器、接口控制器等功能模塊,以實現高效、可靠的數據傳輸和存儲管理。

2023-07-10 15:50:17 2818

2818 SDRAM全稱Synchronous Dynamic RAM,同步動態隨機存儲器。首先,它是RAM,即隨機存儲器的一種。

2023-08-08 15:10:46 896

896

盤點芯邦科技存儲主控芯片 USB控制器芯片 SD卡控制器芯片 存儲主控芯片是一種集成電路芯片,用于控制和管理存儲設備。它負責管理多個存儲單元 (如內存、固態硬盤、閃存卡等)之間的數據傳輸和存取操作

2023-10-25 12:43:00 1055

1055

的SDRAM作為其存儲器,極大地增加了存儲容量。 首先,我們來看一下SDRAM的工作原理。SDRAM由若干存儲單元組成,每個

2024-01-04 14:09:23 343

343

電子發燒友App

電子發燒友App

評論