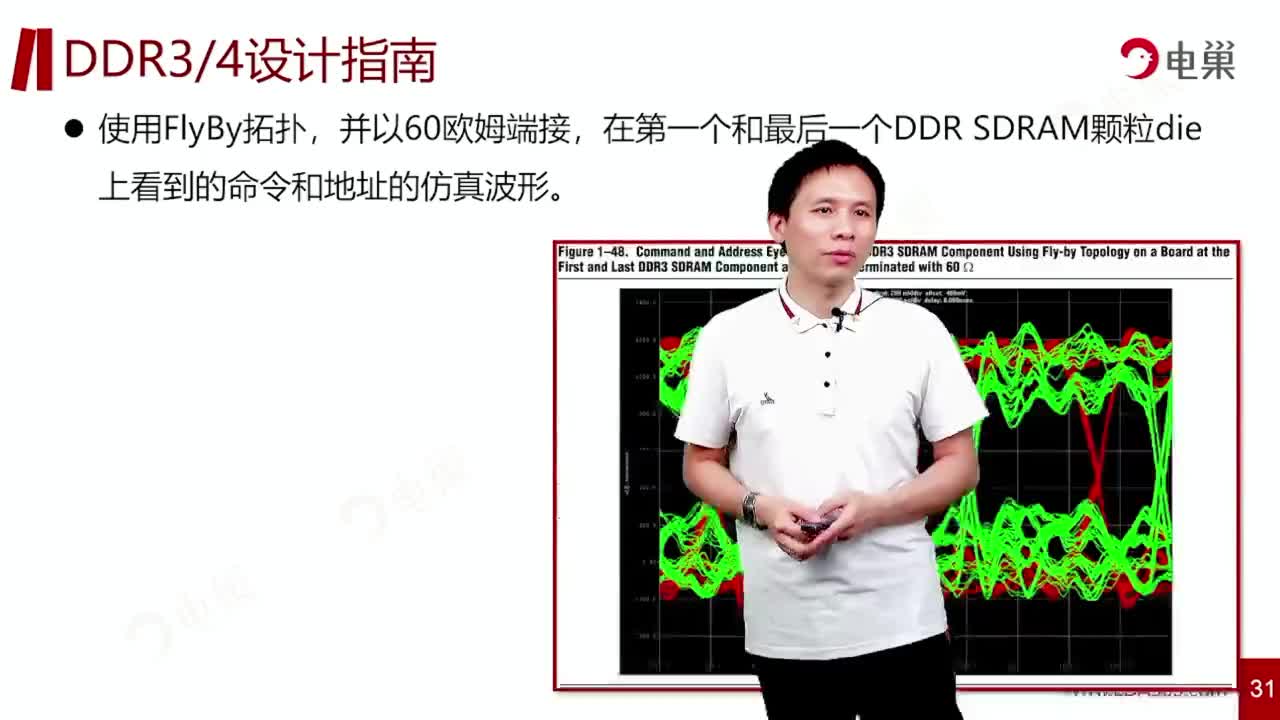

導讀:DDR5協議發布已經有一段時間了,其中的變化還是比較大的,地址信號采取了ODT的端接形式,本篇文章為大家仿真一下DDR5地址信號。同時,我也推薦大家關注我在仿真秀原創的精品課《DDR3/4/5系列信號完整性仿真24講》,讓你清楚掌握DDR協議和仿真關鍵技術要點。

2022-12-01 10:24:03 933

933 《基于“礦板”低成本學習Zynq系列》之六-DDR測試

2023-07-19 19:19:44 1744

1744

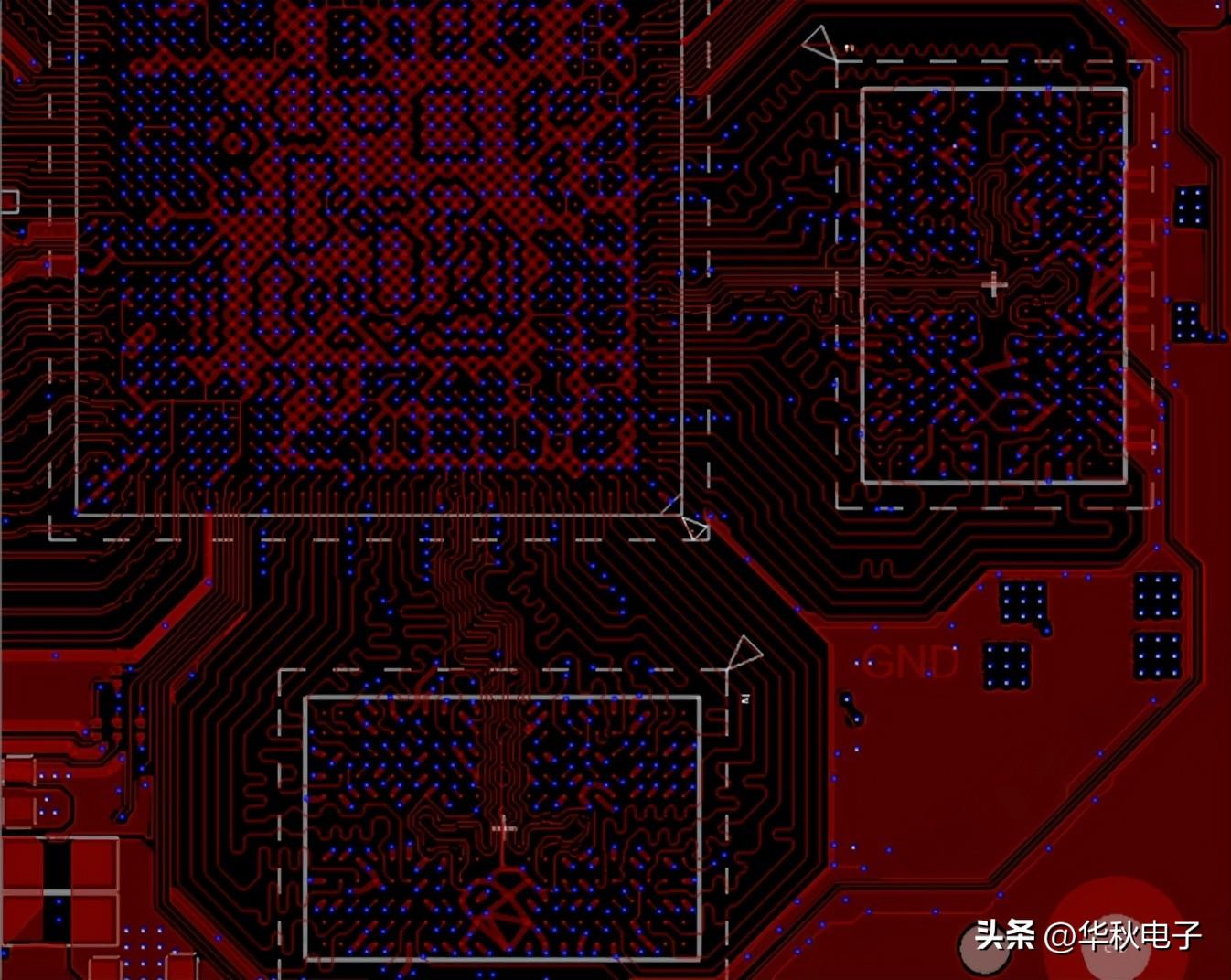

由于RK3588 DDR接口速率最高達4266Mbps,PCB設計難度大,所以強烈建議使用瑞芯微原廠提供的DDR模板和對應的DDR固件,DDR模板是經過嚴格的仿真和測試驗證后發布的。 在單板

2023-08-18 10:55:43 556

556

RK3588 DDR接口速率最高達4266Mbps,PCB設計難度大,所以強烈建議使用瑞芯微原廠提供的DDR模板和對應的DDR固件,DDR模板是經過嚴格的仿真和測試驗證后發布的。 在單板PCB設計空間足夠的情況下,優先考慮留出DDR電路模塊所需要的布局布線空間,拷貝瑞芯微原廠提供的DDR模

2023-08-21 17:16:50 563

563

RK3588 DDR接口速率最高達4266Mbps,PCB設計難度大,所以強烈建議使用瑞芯微原廠提供的DDR模板和對應的DDR固件,DDR模板是經過嚴格的仿真和測試驗證后發布的。 在單板PCB設計空間足夠的情況下,優先考慮留出DDR電路模塊所需要的布局布線空間,拷貝瑞芯微原廠提供的DDR模

2023-08-24 08:40:05 899

899

相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內存下部設計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設計可以保證金手指和內存插槽有足夠的接觸面

2023-09-19 14:49:44 1485

1485

DDR5已經開始商用,但是有的產品還才開始使用DDR4。本文分享一些DDR4的測試內容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達到 3200Mb/s,這樣高速的信號,對信號完整性的要求就更加嚴格,JESD79‐4 規范也對 DDR4 信號的測量提出了一些要求。

2024-01-08 09:18:24 464

464

50個經典541單片機超級仿真(附程序+proteus打開仿真),

2014-07-23 14:26:05

DDR SDRAM參考設計VHDL版(有詳細的文檔,仿真綜合文件)File/Directory Description

2012-08-11 09:33:30

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-02-10 22:50:27

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-02-10 22:55:45

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條,筆記本

2009-08-17 23:00:19

的完整性。 3仿真分析 對DDR3進行仿真分析是以結合項目進行具體說明:選用PowerPC 64位雙核CPU模塊,該模塊采用Micron公司的MT41J256M16HA—125IT為存儲器

2014-12-15 14:17:46

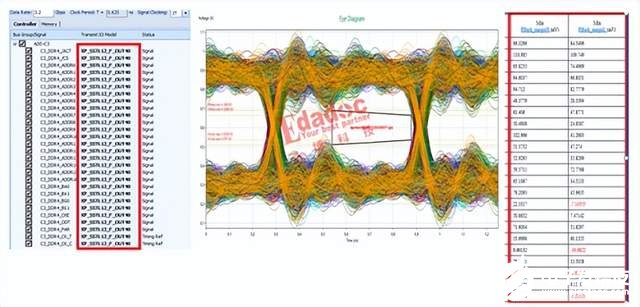

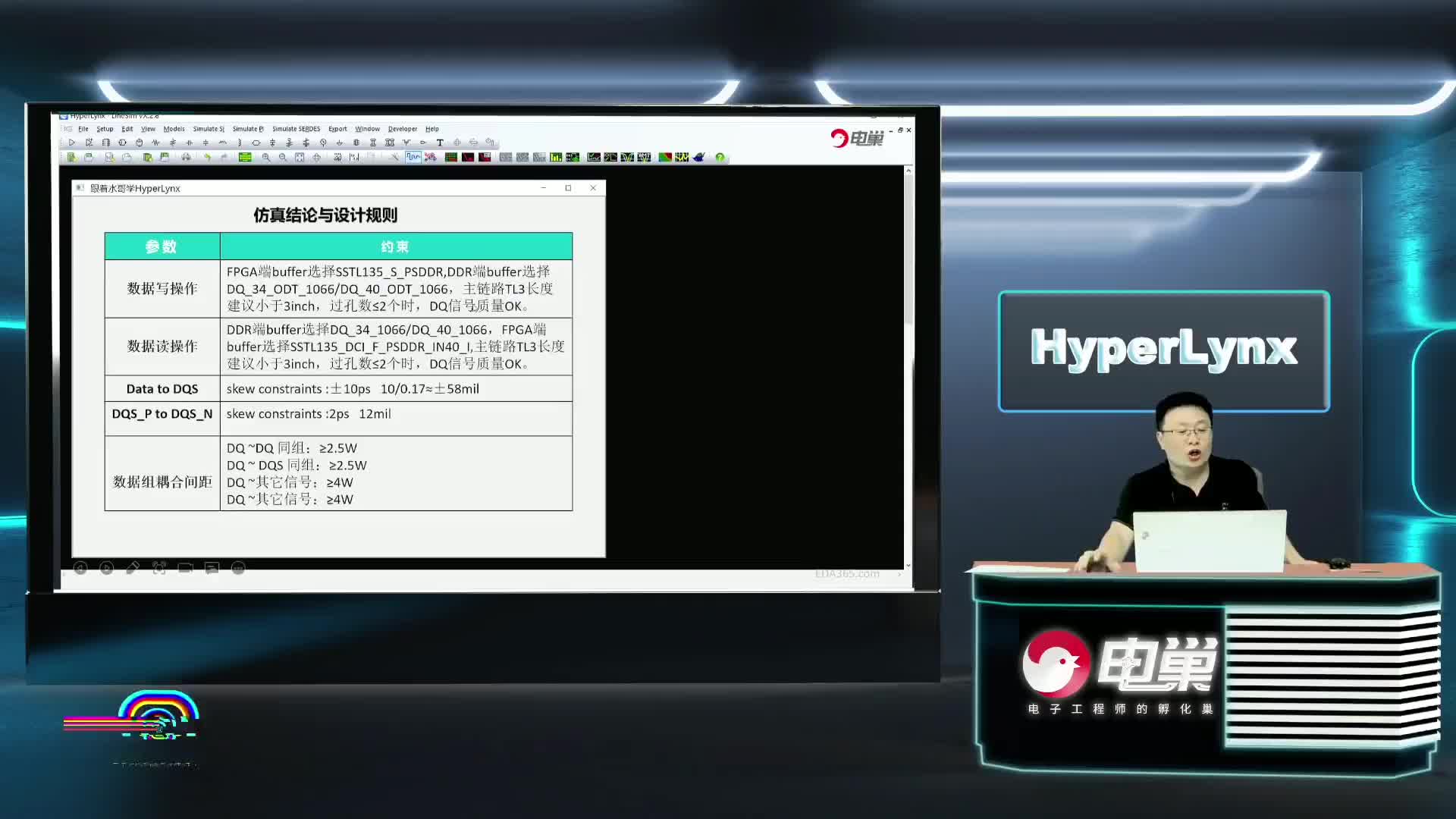

作者:黃剛DDR仿真作為一個非常普遍的仿真模塊,基本上入門SI行業的人都會首先接觸到。記得本人剛接觸這個行業的時候,也是先接觸DDR模塊的仿真。從DDR2到DDR4,可能很多同行都一直使用同一

2019-07-24 06:56:33

這個工程是用來做DDR壓力測試的,通過特殊的數據模式,以EDMA方式寫,讀DDR,校驗結果。在L138的EVM板驗證正常運行.

對于DDR的穩定性測試,CPU的訪問方式是不夠的,有時CPU訪問通過

2018-06-21 13:45:30

kernel 中的 DDR 變頻功能 如何讓 kernel 一次 DDR 變頻都不運行 如何查看 DDR 的容量 如何修改 DDR 頻率 如何修改 DDR 某個頻率對應的電壓 如何關閉 DDR 的負載變頻

2022-06-20 15:35:47

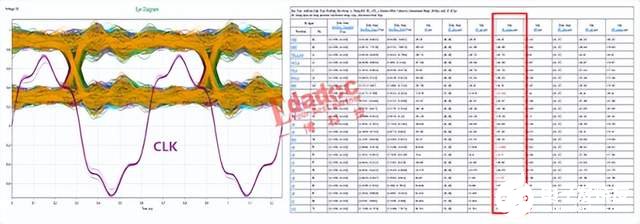

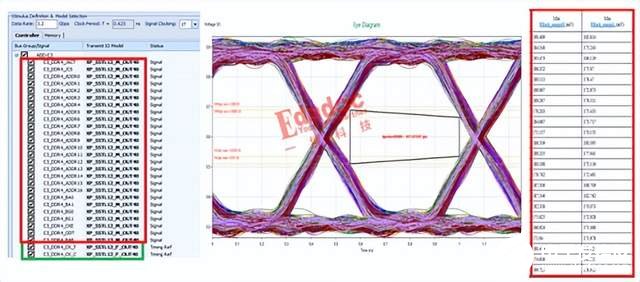

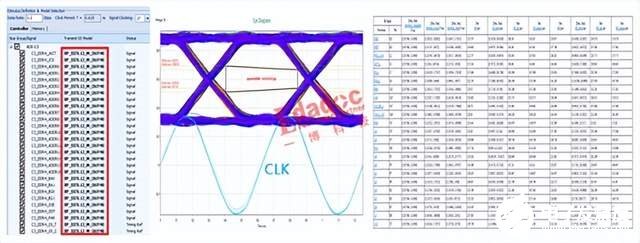

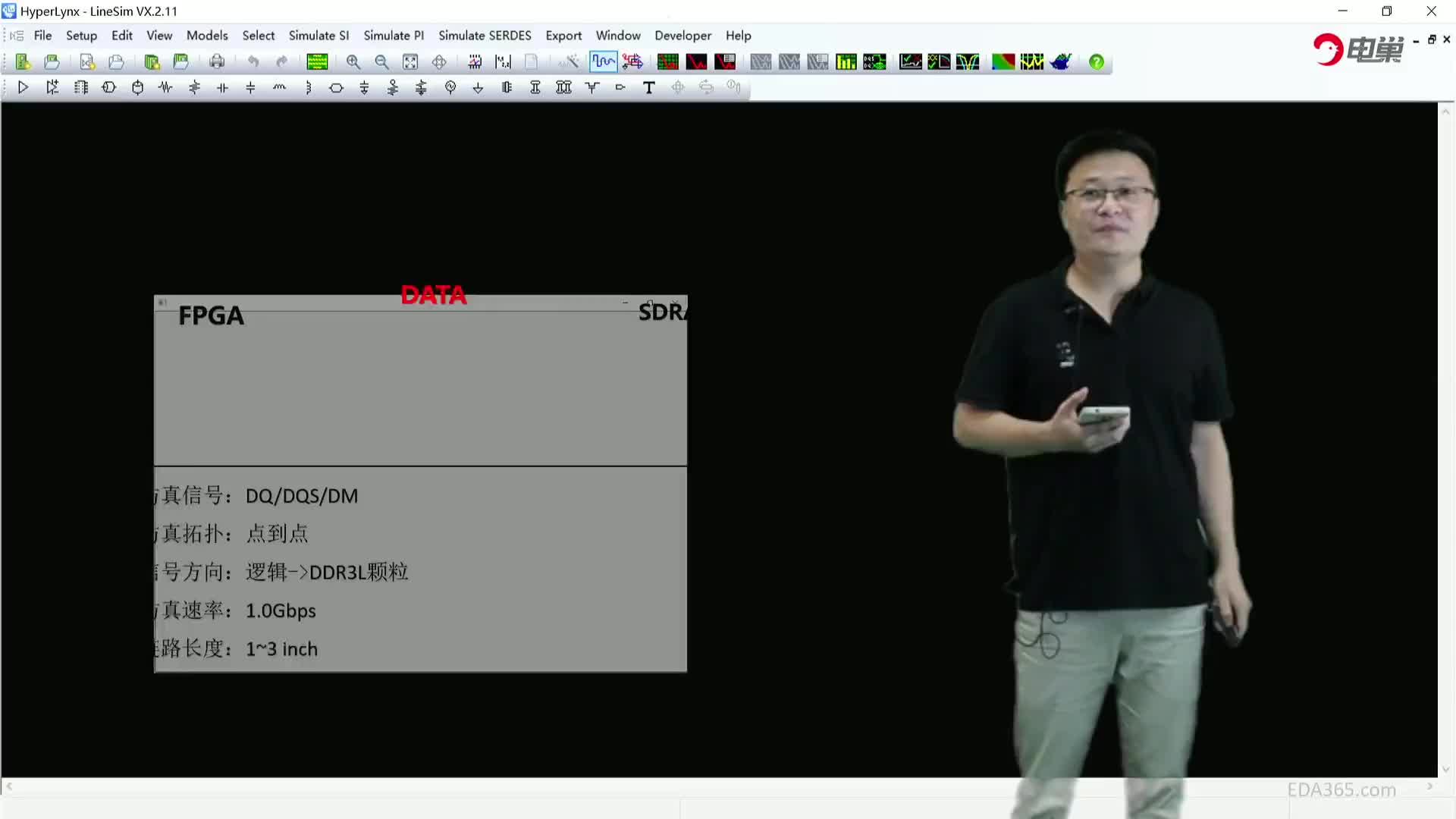

上篇文章我們用仿真實例向大家展示了DDR中地址相對于時鐘的建立時間與保持時間。那么數據信號相對于DQS又是什么樣的關系呢?我們知道,DDR和普通的SDRAM相比起來,讀取速率為普通SDRAM的兩倍

2016-11-08 16:59:51

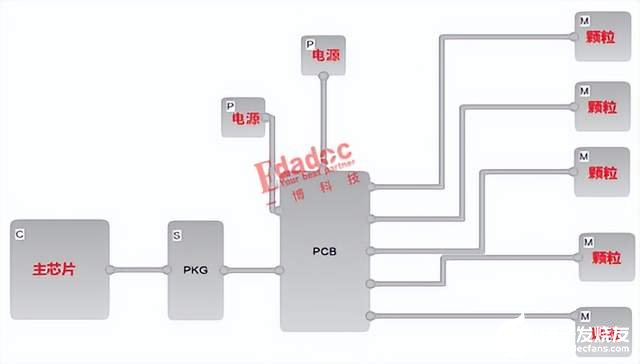

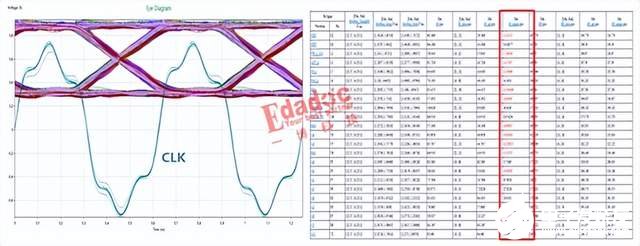

來看一下具體波形。建立如下通道,分別模擬DDR3的地址信號與時鐘信號。圖1 地址/時鐘仿真示意圖為方便計算,我們假設DDR的時鐘頻率為500MHz,這樣對應的地址信號的速率就應該是500Mbps,這里

2018-09-20 10:29:55

著迷等等吧。All right,那今天就再給大家分享一個DDR仿真和測試完美對應的經典案例吧!不知道現在大家做的DDR4系統的指標是怎么樣了?從高速先生和最近眾多客戶的配合來看,從一個通道的總容量

2023-02-02 13:45:09

使用CCS5.4 對EVMDM8168 DDR2 進行測試,測試結果為

第一次測試

Error at 8d033180

FAIL... error code 32... quitting

第二次

2018-06-21 11:49:55

`經典教程書籍--開關電源仿真(PSpice和SPICE3應用)`

2011-03-16 17:50:09

使用兩片DDR2)接口。兩個測試工程與對應的功能如下所示。由于兩種模式的測試方式完全相同,這里僅以兩片32bit模式的工程為例,講解測試過程。1、解壓

2016-12-15 14:43:40

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

AVR單片機寄存器DDR,PORT和PIN之間有什么對應關系?

2021-11-01 06:31:52

DDR、PORT和PIN是什么?AVR單片機寄存器DDR、PORT和PIN之間的對應關系是什么?

2021-07-08 07:22:08

最近在做ddr2方面的東西,需要仿真ddr2,可是一直沒有頭緒。xx_example_top_tb仿真不知道是對是錯,網上說的外掛美光ddr2 模型的仿真方法,沒有具體講解。哪位大蝦能夠指點一二哇,不甚感激!

2016-06-29 15:50:28

DAP仿真器 BURNER

2023-03-28 13:06:20

DDR Memory Interface IP 參考設計可在高云官網下載,參考設計已配置一例特定參數,可用于仿真,實例化加插用戶設計后的總綜合,總布局布線。Gowin DDR Memory

2022-10-08 07:17:32

IBIS Models for DDR2 Analysis 仿真

2012-03-16 16:52:07

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

modelsim仿真DDR3時,出現下面錯誤。Instantiation of 'B_MCB' failed. The design unit was not found.并沒有用ISE聯合仿真

2016-01-21 10:12:40

仿真的經典教程 愿大家學好軟件

2013-01-18 22:58:10

xilinx平臺DDR3設計教程之仿真篇

2020-03-12 08:54:20

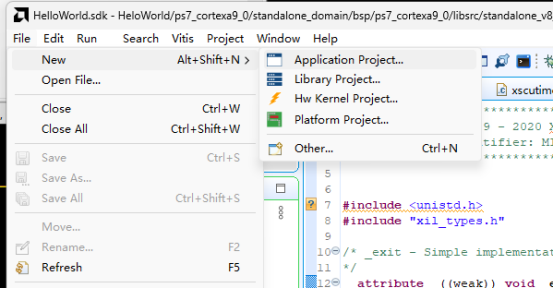

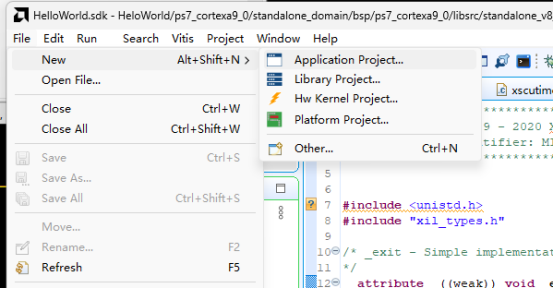

上過程吧》》》》首先接著在前一節的工程里面添加DDR3的配置,這過程很簡單,直接選好最后一一個型號的DDR3即可。。。這是配置好后的工程Diagram視圖下面是對memory的測試在SDK中新建存儲器

2015-05-25 16:23:21

什么情況,我們需要DDR信號仿真分析呢?

2021-03-17 07:38:51

的設計使得比以往任何產品的DDR難度都要大一點,當然我們也就會有很多測試和仿真的案例了。這里關于DDR調試的案例,我們再給大家分享一個從fail到pass的經歷哈。 在一個安靜祥和的午后,高速先生剛剛還略帶

2020-07-10 17:11:30

1.項目的板子上要用到兩顆DDR3芯片,板子打樣回來可能要進行測試,對示波器的采樣率可能會有比較高的要求,不知道大家在設計中用的是什么示波器,最好有具體型號2.既然說到DDR3了,有好些個問題都想

2017-10-26 09:54:13

單片機仿真軟件Proteus 7.4完美破解版

2013-03-01 22:49:57

hello,各位大俠,請問如何測試嵌入式系統linux下的CPU及DDR性能,或者類似跑分軟件。

2016-07-11 17:11:46

自建Spartan6 DDR3仿真平臺

2019-08-01 06:08:47

我們仿真DDR究竟是仿真什么?

2021-03-04 07:32:07

和技術的升級推陳出新。目前,用于主存的DDR SDRAM系列的芯片已經演進到了DDR5了,但市場上對經典的DDR3 SDRAM的需求仍然比較旺盛。測試痛點:測試和驗證電子設備中的DDR內存,客戶一般面臨

2020-12-01 10:29:08

請問電機測試系統如何完美軸對中?

2021-05-08 07:23:20

并沒有一個完全確定的概念,需要我們通過仿真和測試的手段去判斷和驗證。而此時,往往我們拿到的就是一個波形,測試波形或者仿真波形,該如何去判斷其信號質量,參照的標準又是怎樣的,就是我們需要去考慮的重點

2016-09-28 19:00:54

高速DAP仿真器 BURNER

2023-03-28 13:06:20

很經典的仿真器自制資料

2009-02-11 09:08:55 5

5 DDR 1&2&3的“讀”和“寫”眼圖分析:現在不論做主板設計或測試的工程師,還是做內存或DDR芯片設計或測試的工程師都會面臨這樣一個問題:如何能夠分離出“讀”和“寫”

2009-09-14 08:05:25 35

35 經典軟件測試計劃模版:<項目名稱>的這一“測試計劃”文檔有助于實現以下目標:[確定現有項目的信息和應測試的軟件構件。列出推薦的測試需求(高級需求)。推薦

2009-10-19 18:58:50 0

0 經典測試計劃模版:<項目名稱>的這一“測試計劃”文檔有助于實現以下目標:

[確定現有項目的信息和應測試的軟件構件。列出推薦的測試需求(高級需求)。推薦

2009-11-19 17:23:58 0

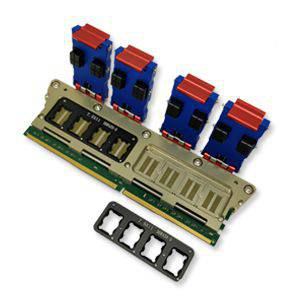

0 DDR內存插槽及測試點

一、實物圖上圖就是DDR內存插槽實物圖

2009-04-26 15:36:51 5390

5390

泰克為DDR測試和驗證解決方案增加兩項新功能

泰克公司日前宣布增強和升級其業界領先的DDR測試和驗證解決方案系列。用于泰克TLA7000系列邏輯分析儀的新型內插器為工

2009-12-08 09:47:00 930

930 什么是DDR傳輸標準

標準的DDR SDRAM分為DDR 200,DDR 266,DDR 333以及DDR 400,其標準工作頻率分別100MHz,133MHz,166MHz和200MHz,對應的內存傳輸帶寬分別為1.6GB/sec,2.12GB

2009-12-24 14:51:34 595

595 Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4257

4257

通過Cadence軟件建立DDRⅡ信號拓撲結構、仿真信號的串擾、碼間干擾、過沖等與信號質量相關的參數,從仿真波形中可以測量出與信號時序相關的參數,從而計算出信號的時序裕量,并為DDRⅡ

2012-02-13 15:16:22 52

52 基于Xilinx的DDR2 SDRAM存儲控制器的用戶接口設計與仿真,本設計通過采用多路高速率數據讀寫操作仿真驗證,可知其完全可以滿足時序要求,由綜合結果可知其使用邏輯資源很少,運行速

2013-01-10 14:12:45 2990

2990 研究了MPC8379E處理器的相關資料和DDR2的特性,以及它們之間PCB布線的規則和仿真設計。由于MPC8379E和DDR2都具有相當高的工作頻率,所以他們之間的走線必須滿足高速PCB布線規則,還要結

2013-03-12 15:22:26 80

80 電子發燒友網站提供《電工實訓深入經典仿真軟件.rar》資料免費下載

2014-05-27 00:53:41 24

24 安捷倫科技公司(NYSE: A)日前推出ADS先進設計系統DDR4 一致性測試平臺,為工程師提供從仿真設計到測量原型產品的完整工作流程。無論是開發DDR 控制器IP 的半導體公司、開發DRAM 芯片

2017-12-05 09:52:02 552

552

對于Layout人員來說,對于DDR這一塊,可能主要關注的是信號線之間的等長。下面我們也來復習一下,DDR各組信號需要滿足的時序關系:地址/命令,控制和時鐘之間等長;DQ與之對應的DQS組內等長;DQS與CLK之間有一個相對寬松的等長關系。

2018-09-15 10:58:00 5805

5805 本文介紹了DDR4技術的特點,并簡單介紹了ANSYS工具用來仿真DDR4的過程。文章中主要介紹的對象為DDR4 3200MHz內存,因為硬件極客對DDR4性能的不斷深挖,目前已經有接近5000MHz的量產內存。

2018-10-14 10:37:28 23341

23341 電源等組成。實時仿真模型系統模型基于AMESim或者MATLAB/SIMULINK進行搭建,提供與FCU控制器硬件IO信號相對應的資源及與FCU控制器控制策略相對應的燃料電池模型等。意昂神州FCU硬件在環(HiL)仿真測試系統http://www.eontronix.cn/FCU/FCU-HiL.html

2019-04-28 22:19:56 1065

1065 DDR驗證是任何SoC中最關鍵和最復雜的任務之一,因為它涉及位于DUT內部的控制器和位于DUT外部的外部DDR存儲器。 DDR系統由控制器,I/O,封裝,插座,電源,時鐘和外部存儲器組成,它們共同

2019-08-12 11:29:17 3917

3917

DDR3 SDRAM是DDR3的全稱,它針對Intel新型芯片的一代內存技術(但目前主要用于顯卡內存),頻率在800M以上。DDR3是在DDR2基礎上采用的新型設計,與DDR2 SDRAM相比具有功耗和發熱量較小、工作頻率更高、降低顯卡整體成本、通用性好的優勢。

2019-10-29 08:00:00 0

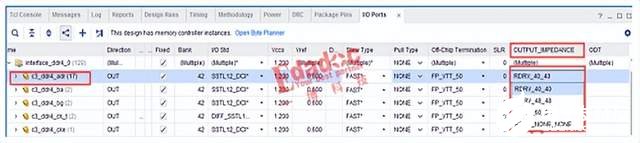

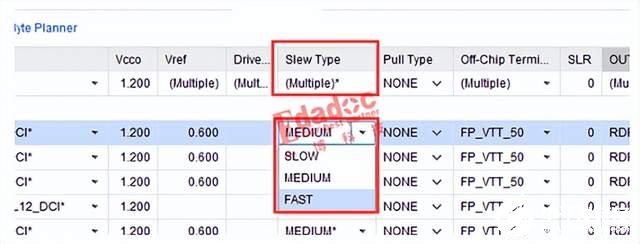

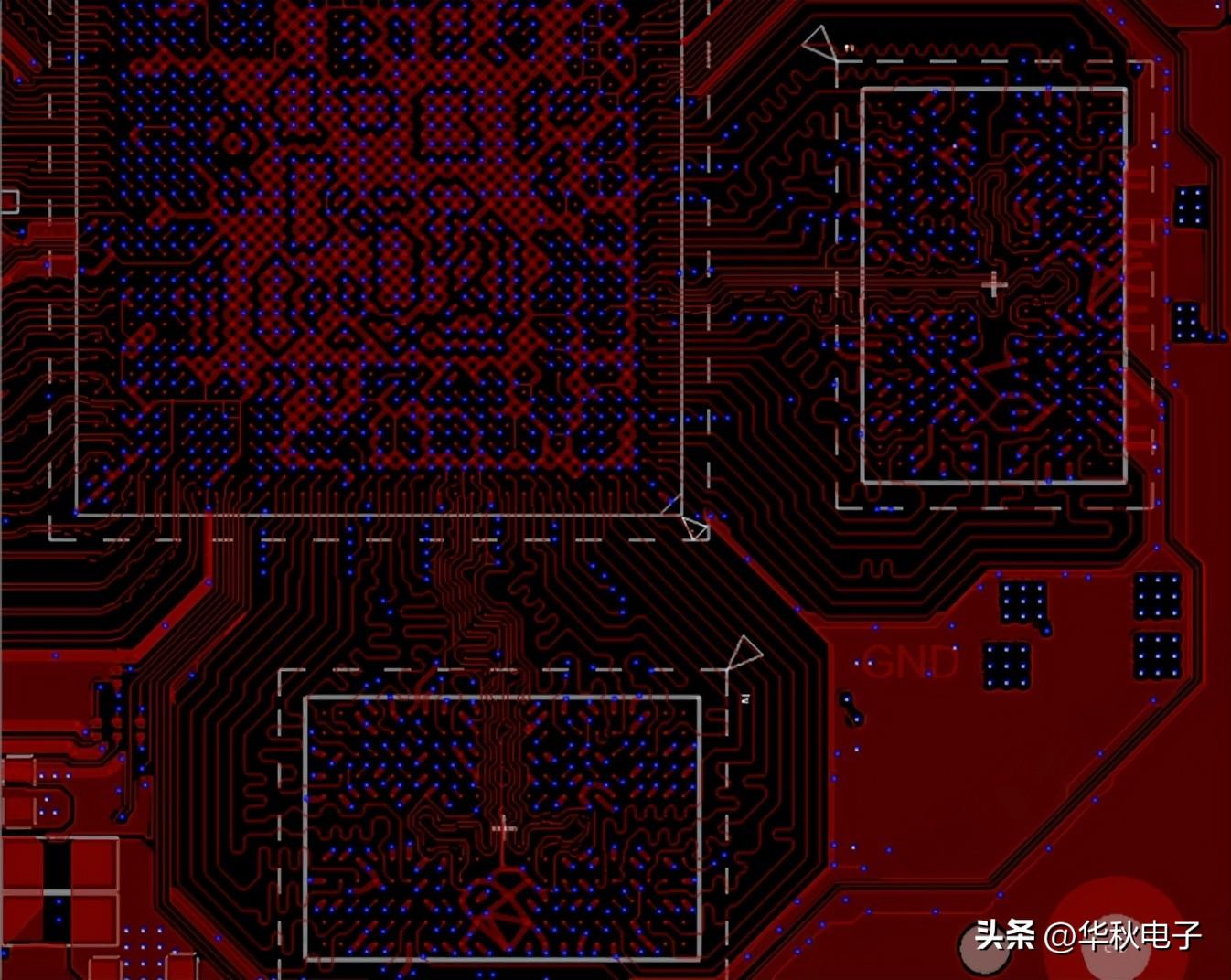

0 首先按PowerSI提取s參數仿真指導書步驟將DDR的PORT點設置好(如下圖所示)并提取出s參數

2020-04-14 08:00:00 0

0 本文檔的主要內容詳細介紹的是DDR和DDR2與DDR3的設計資料總結包括了:一、DDR的布線分析與設計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 容易引起電路的 SI 問題,信號測試驗證也變得越來越困難。一般 DDR 信號測試、仿真驗證,大多數用 SPEED2000,大家在學習 DDR 仿真前,可以先補充 SPEED2000 的時域波形仿真

2023-02-07 16:37:34 896

896 DDR仿真作為一個非常普遍的仿真模塊,基本上入門SI行業的人都會首先接觸到。記得本人剛接觸這個行業的時候,也是先接觸DDR模塊的仿真。從DDR2到DDR4,可能很多同行都一直使用同一套的仿真方法

2021-03-31 14:01:18 2449

2449 大家好,又到了每日學習的時間了,今天我們來聊一聊FPGA中測試文件編寫的相關知識,聊一聊激勵仿真。 ? 1. 激勵的產生 對于testbench而言,端口應當和被測試的module一一對應。端口分為

2021-04-02 18:27:02 6010

6010 這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2021-05-02 09:05:00 2979

2979

前言 上文中,我們介紹了DDR芯片的物理層及協議測試,本文我們繼續給大家揭秘如何利用是德科技的ADS仿真軟件輔助進行DDR的電路仿真,驗證和分析。 是德科技ADS簡介 是德科技PathWave

2021-05-17 09:28:05 10208

10208

現在DDR應用越來越普遍,很多同事不清楚DDR的壓力測試都要進行哪些測試;現對DDR的壓力測試項進行了總結,供大家參考。

2021-06-24 16:28:06 15

15 現在DDR應用越來越普遍,很多同事不清楚DDR都要進行哪些測試;本文對DDR的測試項進行了總結,供大家參考。

2021-06-26 15:45:39 26

26 ??這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2022-08-16 10:28:58 1241

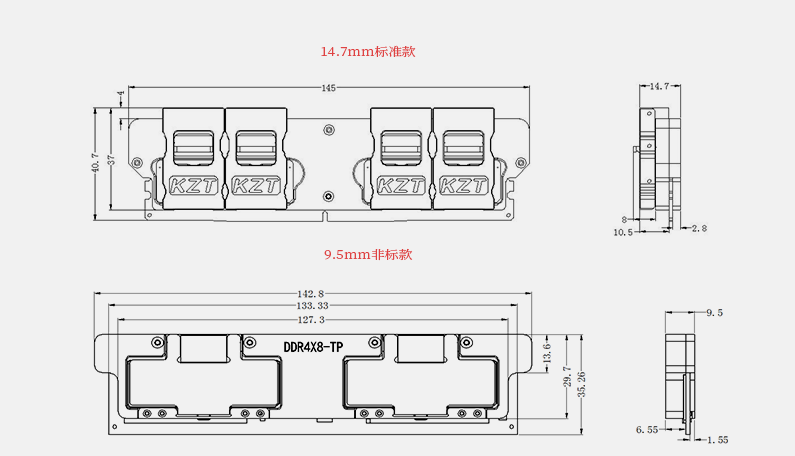

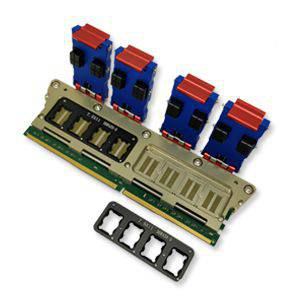

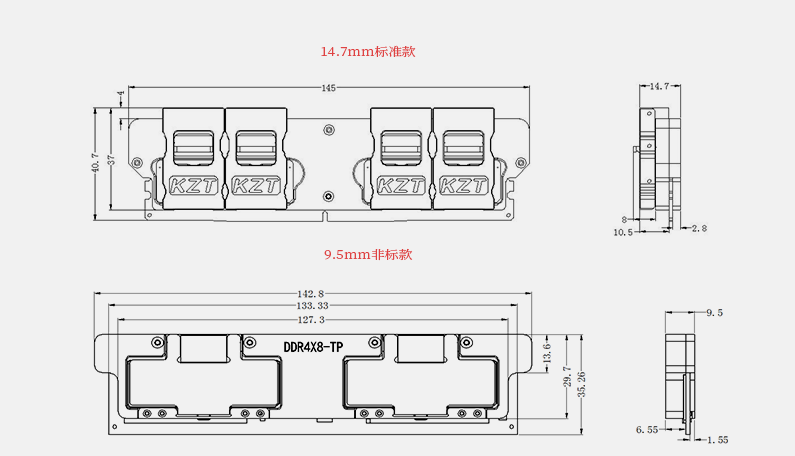

1241 高速度,高頻率的測試座,凱智通經過多年潛心研發,重磅推出了擁有自主設計專利知識產權的DDR DIMM 雙面彈測試治具,對應市場最新需求!!

2022-09-08 14:57:21 1223

1223

凱智通最新發布DDR DIMM雙面彈測試治具適用于DDR?/5測試的,與之前常用的導電膠,從材質還是工作原理都各不相同,我們今天就來比較一下這兩款的區別。

2022-09-09 09:55:06 1415

1415

迪賽康DDR4/DDR5 Interposr測試板專門為內存顆粒測試設計,阻抗一致性優異,極低延遲,最高速率支持6.4Gbps,可以用于78pin和96pin/102pin封裝的DDR4和DDR5顆粒測試。

2022-10-10 09:33:48 3592

3592 DDR2總線的仿真方法,基于Agree公司最新的網絡處理器APP300和HY的

DDR2 SDRAM HY5PS121621。

2022-10-21 16:09:58 0

0 DDR2設計和仿真技術詳解。

2022-10-24 15:10:18 2

2 第一次接觸DDR的仿真我也是比較茫然的,首先各種仿真軟件基本沒有使用過,研究生階段雖然使用過ADS、HFSS等仿真軟件,但主要還是進行無源鏈路的仿真。

2023-02-11 09:59:44 1011

1011 DDR3的速度較高,如果控制芯片封裝較大,則不同pin腳對應的時延差異較大,必須進行pin delay時序補償。

2023-07-04 09:25:38 313

313

復制Vivado工程路徑vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夾。粘貼到仿真路徑testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夾)下。

2023-08-12 11:08:27 735

735 RK3588 DDR接口速率最高達4266Mbps,PCB設計難度大,所以強烈建議使用瑞芯微原廠提供的DDR模板和對應的DDR固件,DDR模板是經過嚴格的仿真和測試驗證后發布的。 在單板PCB設計空間足夠的情況下,優先考慮留出DDR電路模塊所需要的布局布線空間,拷貝瑞芯微原廠提供的DDR模

2023-08-17 18:15:02 325

325

RK3588DDR接口速率最高達4266Mbps,PCB設計難度大,所以強烈建議使用瑞芯微原廠提供的DDR模板和對應的DDR固件,DDR模板是經過嚴格的仿真和測試驗證后發布

2023-08-18 08:09:43 385

385

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1896

1896

Chipown經典多模式ACDC芯片PN8715H/PN8712H系列,可完美替代進口工業級芯片5ARxx系列 。

2023-09-14 14:33:42 709

709

DDR一致性測試的操作步驟? DDR(雙數據率)一致性測試是對DDR內存模塊進行測試以確保其性能和可靠性。在進行DDR一致性測試時,需要遵循一系列的操作步驟,以保證測試的準確性和完整性。下面將詳細

2024-02-01 16:24:52 212

212

電子發燒友App

電子發燒友App

評論