最近semiengineering與業(yè)內(nèi)專家就日益異構(gòu)的系統(tǒng)中內(nèi)存的發(fā)展之路進行了討論。以下是對話的摘錄。

Q

當我們與AI/ML和功率需求作斗爭時,需要重新考慮哪些配置?我們會看到馮·諾伊曼架構(gòu)的轉(zhuǎn)變嗎?

Steven Woo,Rambus的杰出發(fā)明家:就系統(tǒng)架構(gòu)而言,行業(yè)中出現(xiàn)了分歧。我們在基于x86的云服務(wù)器上運行的占主導地位的傳統(tǒng)應(yīng)用程序不會消失。已經(jīng)建立和發(fā)展了幾十年的軟件,它們將依賴于這種架構(gòu)來運行良好。相比之下,AI/ML是一個新類別。人們重新考慮了體系結(jié)構(gòu),并構(gòu)建了非常特定于領(lǐng)域的處理器。我們看到,大約三分之二的能量花在處理器和HBM設(shè)備之間的數(shù)據(jù)移動上,而只有大約三分之一的能量花在實際訪問DRAM核心中的比特上。數(shù)據(jù)移動現(xiàn)在更具挑戰(zhàn)性,成本也高得多。我們不會消除記憶。我們需要它是因為數(shù)據(jù)集越來越大。所以問題是,‘什么才是正確的前進道路?“有很多關(guān)于堆疊的討論。如果我們把內(nèi)存直接放在處理器上,它會為你做兩件事。首先,今天的帶寬是由岸邊或芯片的周長限制。這就是I/ o的去向。但是如果你把它直接堆疊在處理器上,現(xiàn)在你可以利用芯片的整個面積來進行分布式互連,你可以在內(nèi)存本身獲得更多的帶寬,它可以直接向處理器提供信息。鏈路變得更短,電源效率可能會提高5到6倍。其次,由于更多的區(qū)域陣列與內(nèi)存互連,您可以獲得的帶寬量也增加了幾個整數(shù)倍。同時做這兩件事可以提供更多的帶寬,并使其更節(jié)能。行業(yè)的發(fā)展?jié)M足了各種需求,這絕對是我們看到存儲系統(tǒng)在未來開始發(fā)展的一種方式,它將變得更加節(jié)能,并提供更多的帶寬。

Cadence 產(chǎn)品管理組總監(jiān)Frank Ferro :當我在2016年開始研究HBM時,一些更高級的客戶問它是否可以堆疊。他們一直在研究如何將DRAM堆疊在上面,因為有明顯的優(yōu)勢。從物理層來看,PHY基本上可以忽略不計,這節(jié)省了大量的功率和效率。但現(xiàn)在你有了一個100w的處理器,上面還有一個內(nèi)存。記憶承受不了熱量。這可能是熱量鏈中最薄弱的一環(huán),這就帶來了另一個挑戰(zhàn)。這是有好處的,但他們?nèi)匀恍枰宄绾螒?yīng)對熱氣流。現(xiàn)在有更多的動機推動這種類型的架構(gòu)向前發(fā)展,因為它確實在性能和功率方面節(jié)省了您的總體成本,并且它將提高您的計算效率。但也有一些物理設(shè)計上的挑戰(zhàn)需要解決。正如史蒂夫所說,我們看到各種各樣的架構(gòu)正在出現(xiàn)。我完全同意GPU/CPU架構(gòu)不會消失,它們?nèi)詫⒄紦?jù)主導地位。與此同時,地球上的每家公司都在努力開發(fā)更好的捕鼠器來實現(xiàn)他們的人工智能。我們看到片上SRAM和高帶寬存儲器的組合。在如何在數(shù)據(jù)中心中利用LPDDR的問題上,LPDDR近來一直備受關(guān)注。我們甚至看到GDDR被用于一些人工智能推理應(yīng)用程序,以及所有舊的內(nèi)存系統(tǒng)。他們現(xiàn)在正試圖在一個空間內(nèi)壓縮盡可能多的ddr5。我看過你能想到的所有架構(gòu),無論是DDR、HBM、GDDR還是其他。這取決于你的處理器核心,你的整體附加值是什么,然后你如何突破你的特定架構(gòu)。內(nèi)存系統(tǒng),所以你可以雕刻你的CPU和你的內(nèi)存架構(gòu),這取決于什么是可用的。

Jongsin Yun,西門子 EDA內(nèi)存技術(shù)專家:另一個問題是非波動性。例如,如果人工智能必須處理運行基于物聯(lián)網(wǎng)的人工智能之間的電源間隔,那么我們就需要大量的電源開關(guān),并且所有用于人工智能訓練的信息必須一次又一次地旋轉(zhuǎn)。如果我們有某種解決方案,可以將這些重量存儲到芯片中,這樣我們就不必總是為相同的重量來回移動,那么它將節(jié)省大量電力,特別是對于基于物聯(lián)網(wǎng)的人工智能。將會有另一種解決方案來滿足這些電力需求。

Frank Schirrmeister,Arteris解決方案和業(yè)務(wù)開發(fā)副總裁:從NoC的角度來看,我覺得有趣的是,你必須優(yōu)化這些路徑,從處理器到NoC,通過控制器訪問內(nèi)存接口,可能通過UCIe將一個芯片傳遞給另一個芯片,然后芯片中有內(nèi)存。這并不是說馮·諾伊曼架構(gòu)已經(jīng)死了。但是現(xiàn)在有很多變化,這取決于您想要計算的工作負載。它們需要在記憶的背景下考慮,而記憶只是一個方面。你從哪里得到數(shù)據(jù)的位置,它是如何安排在這個DRAM?我們正在研究所有這些東西,比如內(nèi)存的性能分析,然后在其上優(yōu)化系統(tǒng)架構(gòu)。它激發(fā)了許多新架構(gòu)的創(chuàng)新,這是我在大學學習馮·諾伊曼時從未想過的。在另一端,你有像網(wǎng)格這樣的東西。現(xiàn)在有更多的架構(gòu)需要考慮,這是由內(nèi)存帶寬、計算能力等驅(qū)動的,而不是以同樣的速度增長。

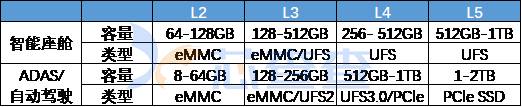

Randy White,是德科技內(nèi)存解決方案項目經(jīng)理:有一種趨勢涉及到分解計算或分布式計算,這意味著架構(gòu)師需要更多的工具。內(nèi)存層次結(jié)構(gòu)已經(jīng)擴展。包括語義,以及CXL和不同的混合存儲器,可用于閃存和DRAM。與數(shù)據(jù)中心并行的應(yīng)用程序是汽車。汽車總是有這種傳感器計算與ecu(電子控制單元)。我很著迷于它是如何演變成數(shù)據(jù)中心的。快進,今天我們有了分布式計算節(jié)點,稱為域控制器。這是一樣的。它試圖解決的問題是,也許功率不是一個大問題,因為計算機的規(guī)模沒有那么大,但延遲肯定是汽車的一個大問題。ADAS需要超高帶寬,你需要做出不同的權(quán)衡。然后你有更多的機械傳感器,但在數(shù)據(jù)中心有類似的限制。你有了不需要低延遲的冷存儲,然后你有了其他高帶寬應(yīng)用。看到架構(gòu)師的工具和選擇已經(jīng)發(fā)生了多大的變化是很有趣的。這個行業(yè)已經(jīng)做出了很好的回應(yīng),我們所有人都提供了各種各樣的解決方案,以滿足市場的需求。

Q

內(nèi)存設(shè)計工具是如何發(fā)展的?

Schirrmeister:當我在90年代開始制作我的第一批芯片時,最常用的系統(tǒng)工具是Excel。從那時起,我就一直希望它能在某一點上中斷,因為我們在系統(tǒng)級做的事情,內(nèi)存、帶寬分析等等。這對我的團隊影響很大。在當時,這是非常先進的東西。但蘭迪的觀點是,現(xiàn)在某些復雜的東西需要在一定的保真度上進行模擬,這在以前沒有計算機是不可能的。舉個例子,假設(shè)DRAM訪問的一定延遲可能導致糟糕的體系結(jié)構(gòu)決策,并可能錯誤地設(shè)計芯片上的數(shù)據(jù)傳輸體系結(jié)構(gòu)。另一面也是如此。如果您總是假設(shè)最壞的情況,那么您將過度設(shè)計體系結(jié)構(gòu)。讓工具執(zhí)行DRAM和性能分析,并為控制器提供適當?shù)哪P停辜軜?gòu)師可以模擬所有這些,這是一個令人著迷的環(huán)境。從90年代開始,我就希望Excel作為一個系統(tǒng)級工具可能會在某一點上崩潰,因為某些動態(tài)影響你不能再用Excel來做了,因為你需要模擬它們——尤其是當你扔進一個帶有PHY特性的死對死接口時,然后鏈接層特性,比如所有的檢查是否都是正確的,并可能重新發(fā)送數(shù)據(jù)。不進行這些模擬將導致次優(yōu)架構(gòu)。

Ferro:我們做大多數(shù)評估的第一步是給他們提供內(nèi)存測試平臺,開始觀察DRAM的效率。這是一個巨大的進步,即使是像運行本地工具來進行DRAM模擬這樣簡單的事情,也要進行全面的模擬。我們看到越來越多的客戶要求這種模擬。在任何評估中,確保您的DRAM效率在90%以上是非常重要的第一步。

Woo:你看到全系統(tǒng)模擬工具興起的部分原因是dram變得更加復雜了。對于一些復雜的工作負載,現(xiàn)在使用Excel這樣的簡單工具是很難做到的。如果你看一下90年代的DRAM數(shù)據(jù)表,那些數(shù)據(jù)表大概有40頁。現(xiàn)在已經(jīng)有幾百頁了。這只是說明了為了獲得高帶寬,設(shè)備的復雜性。再加上內(nèi)存是系統(tǒng)成本的驅(qū)動因素,以及與處理器性能相關(guān)的帶寬和延遲。它也是一個很大的動力驅(qū)動因素,所以你現(xiàn)在需要在更詳細的層面上進行模擬。就工具流而言,系統(tǒng)架構(gòu)師理解內(nèi)存是一個巨大的驅(qū)動因素。因此,這些工具需要更加復雜,并且它們需要與其他工具進行良好的接口,以便系統(tǒng)架構(gòu)師能夠獲得最佳的全局視圖,以了解正在發(fā)生的事情—特別是內(nèi)存如何影響系統(tǒng)。

Yun:隨著我們進入人工智能時代,使用了很多多核系統(tǒng),但我們不知道哪些數(shù)據(jù)去了哪里。它也更加平行于芯片。內(nèi)存的大小要大得多。如果我們使用chatgpt類型的AI,那么模型的數(shù)據(jù)處理需要大約350MB的數(shù)據(jù),這對于一個權(quán)重來說是一個巨大的數(shù)據(jù)量,實際的輸入/輸出要大得多。所需數(shù)據(jù)量的增加意味著有很多我們以前從未見過的概率效應(yīng)。要查看與這么大的內(nèi)存有關(guān)的所有錯誤,這是一項極具挑戰(zhàn)性的測試。ECC無處不在,甚至在SRAM中,它傳統(tǒng)上不使用ECC,但現(xiàn)在它在最大的系統(tǒng)中很常見。測試所有這些都是非常具有挑戰(zhàn)性的,需要EDA解決方案來支持測試所有這些不同的條件。

Q

工程團隊在日常工作中面臨哪些挑戰(zhàn)?

White:在任何一天,你都能在實驗室找到我。我卷起袖子,把手弄臟了,戳電線,焊接什么的。我想了很多關(guān)于后硅驗證的事情。我們談到了早期的模擬和芯片上的工具——BiST,以及類似的東西。在一天結(jié)束的時候,在我們發(fā)布之前,我們想要做一些系統(tǒng)驗證或設(shè)備級測試。我們討論了如何克服記憶墻。我們共同定位內(nèi)存,HBM等。如果我們看看包裝技術(shù)的發(fā)展,我們從含鉛包裝開始。它們對信號完整性不太好。幾十年后,我們轉(zhuǎn)向優(yōu)化信號完整性,如球柵陣列(bga)。我們無法訪問它,這意味著你無法測試它。因此,我們提出了這個概念,稱為設(shè)備插播器-一個BGA插播器-它使我們能夠夾在一個特殊的夾具中,將信號路由出去。然后我們可以把它連接到測試設(shè)備上。快進到今天,現(xiàn)在我們有HBM和小嬰兒。我如何夾夾我的夾具之間的硅中間層?我們做不到,這就是我們的掙扎。這是一個讓我夜不能寐的挑戰(zhàn)。在OEM或系統(tǒng)客戶無法獲得90%效率的情況下,我們?nèi)绾卧诂F(xiàn)場執(zhí)行故障分析?鏈接中有更多的錯誤,它們不能正確初始化,訓練也不能正常工作。是系統(tǒng)完整性問題嗎?

Schirrmeister:難道你不愿意在家里用虛擬界面來做這個,而不是走到實驗室去嗎?答案不就是你在芯片中內(nèi)置更多的分析嗎?通過小芯片,我們進一步整合了一切。讓你的烙鐵在那里不是一個真正的選擇,所以需要有一種方法,芯片上的分析。NoC也有同樣的問題。人們查看NoC,你發(fā)送數(shù)據(jù),然后它就消失了。我們需要把分析放到那里,這樣人們就可以進行調(diào)試,并擴展到制造層面,這樣你就可以在家工作,并基于芯片分析完成所有工作。

White:特別是在高帶寬內(nèi)存的情況下,你無法親自進入那里。當我們授權(quán)PHY時,我們也有一個與之配套的產(chǎn)品,這樣你就可以監(jiān)視這1024位中的每一個。您可以從該工具開始讀寫DRAM,因此您不必親自進入該工具。我喜歡中間人的想法。在測試期間,我們確實會從中間插腳中取出一些引腳,這在系統(tǒng)中是無法做到的。進入這些3D系統(tǒng)真的是一個挑戰(zhàn)。甚至從設(shè)計工具流程的角度來看,似乎大多數(shù)公司在這些2.5D工具上都有自己的流程。我們開始以一種更加標準化的方式來構(gòu)建一個2.5D系統(tǒng),從信號完整性,功率,整個流程。

White:隨著事情的發(fā)展,我希望我們?nèi)匀荒鼙3滞瑯拥木_度。我在UCIe外形尺寸合規(guī)小組。我在研究如何描述一個已知的好骰子,一個金骰子。最終,這將花費更多的時間,但我們將在我們需要的測試的性能和準確性,以及內(nèi)置的靈活性之間找到一個滿意的中間點。

Schirrmeister:如果我在更開放的生產(chǎn)環(huán)境中研究小芯片及其應(yīng)用,測試是使其正常工作的更大挑戰(zhàn)之一。如果我是一家大公司,我控制著它的所有方面,那么我可以適當?shù)丶s束事情,這樣測試等就變得可行。如果我想用UCIe的口號,UCI和PCI只有一個字母的距離,我想象未來UCIe的組裝,從制造的角度來看,就像今天PC上的PCI插槽一樣,那么測試方面真的很有挑戰(zhàn)性。我們需要找到解決辦法。有很多工作要做。

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論