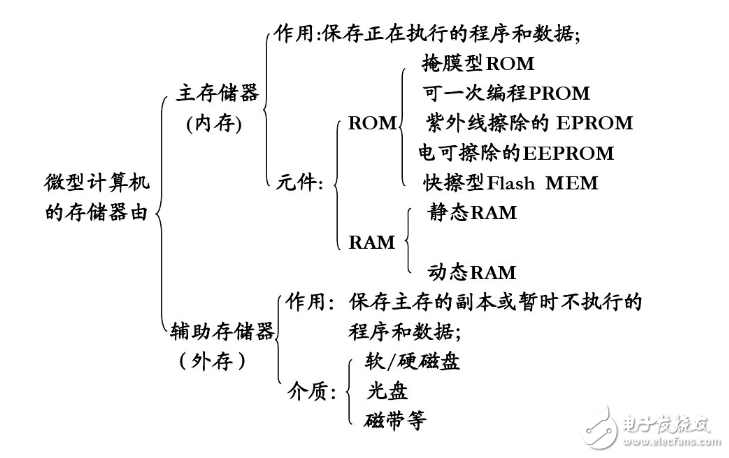

存儲器(Memory)是現(xiàn)代信息技術(shù)中用于保存信息的記憶設(shè)備。其概念很廣,有很多層次,在數(shù)字系統(tǒng)中,只要能保存二進制數(shù)據(jù)的都可以是存儲器;在集成電路中,一個沒有實物形式的具有存儲功能的電路也叫存儲器,如RAM、FIFO等;在系統(tǒng)中,具有實物形式的存儲設(shè)備也叫存儲器,如內(nèi)存條、TF卡等。計算機中全部信息,包括輸入的原始數(shù)據(jù)、計算機程序、中間運行結(jié)果和最終運行結(jié)果都保存在存儲器中。它根據(jù)控制器指定的位置存入和取出信息。有了存儲器,計算機才有記憶功能,才能保證正常工作。計算機中的存儲器按用途存儲器可分為主存儲器(內(nèi)存)和輔助存儲器(外存),也有分為外部存儲器和內(nèi)部存儲器的分類方法。外存通常是磁性介質(zhì)或光盤等,能長期保存信息。內(nèi)存指主板上的存儲部件,用來存放當(dāng)前正在執(zhí)行的數(shù)據(jù)和程序,但僅用于暫時存放程序和數(shù)據(jù),關(guān)閉電源或斷電,數(shù)據(jù)會丟失。

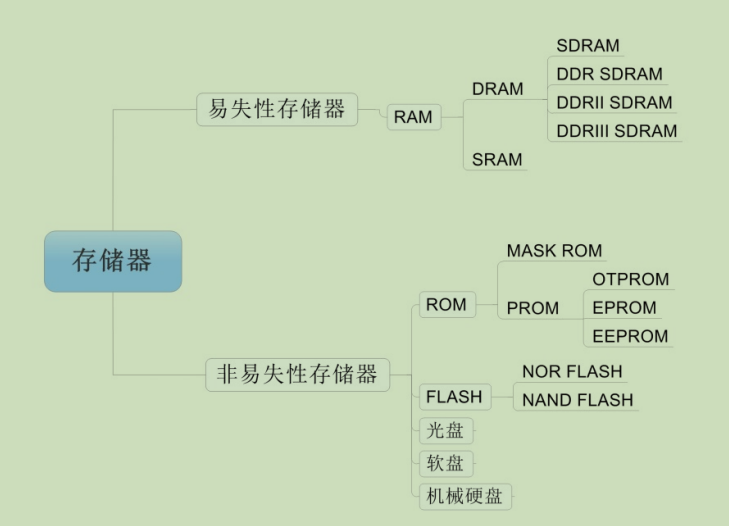

存儲器的分類

1.按存儲器與中央處理器關(guān)系分

內(nèi)部存儲器

外部存儲器

按存儲介質(zhì)

半導(dǎo)體存儲器:用半導(dǎo)體器件組成的存儲器。

磁表面存儲器:用磁性材料做成的存儲器。

按存儲方式

隨機存儲器:任何存儲單元的內(nèi)容都能被隨機存取,且存取時間和存儲單元的物理位置無關(guān)。

順序存儲器:只能按某種順序來存取,存取時間和存儲單元的物理位置有關(guān)。

按讀寫功能

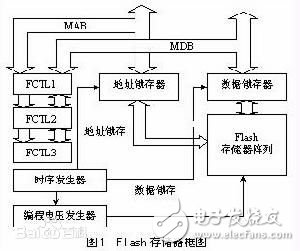

只讀存儲器(ROM):存儲的內(nèi)容是固定不變的,只能讀出而不能寫入的半導(dǎo)體存儲器。

隨機讀寫存儲器(RAM):既能讀出又能寫入的各存儲器之間的關(guān)系半導(dǎo)體存儲器。

按信息保存性

非永久記憶的存儲器:斷電后信息即消失的存儲器。

永久記憶性存儲器:斷電后仍能保存信息的存儲器。

按用途

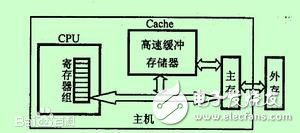

根據(jù)存儲器在計算機系統(tǒng)中所起的作用,可分為主存儲器、輔助存儲器、高速緩沖存儲器、控制存儲器等。

為了解決對存儲器要求容量大,速度快,成本低三者之間的矛盾,通常采用多級存儲器體系結(jié)構(gòu),即使用高速緩沖存儲器、主存儲器和外存儲器。

主存儲器的技術(shù)指標(biāo)

主存儲器的性能指標(biāo)主要是存儲容量、存取時間、存儲周期和存儲器帶寬。

字存儲單元即存放一個機器字的存儲單元,相應(yīng)的地址稱為字地址。一個機器字可以包含數(shù)個字節(jié),

所以一個存儲單元也可包含數(shù)個能夠單獨編址的字節(jié)地址。

下面列出主存儲器的主要幾項技術(shù)指標(biāo):

主存儲器的主要幾項技術(shù)指標(biāo) 指標(biāo)含義表現(xiàn)單位

存儲容量 在一個存儲器中可以容納的存儲單元總數(shù) 存儲空間的大小 字?jǐn)?shù),字節(jié)數(shù)

存取時間 啟動到完成一次存儲器操作所經(jīng)歷的時間 主存的速度 ns

存儲周期 連續(xù)啟動兩次操作所需間隔的最小時間 主存的速度 ns

存儲器帶寬 單位時間里存儲器所存取的信息量, 數(shù)據(jù)傳輸速率技術(shù)指標(biāo) 位/秒,字節(jié)/秒

主存儲器的性能指標(biāo)主要是存儲容量、存取時間和存儲周期。

存放一個機器字的存儲單元,通常稱為字存儲單元,相應(yīng)的單元地址叫字地址。而存放一個字節(jié)的單元,稱為字節(jié)存儲單元,相應(yīng)的地址稱為字節(jié)地址。如果計算機中可編址的最小單位是字存儲單元,則該計算機稱為按字編址的計算機。如果計算機中可編址的最小單位是字節(jié),則該計算機稱為按字節(jié)編址的計算機。一個機器字可以包含數(shù)個字節(jié),所以一個存儲單元也可以包含數(shù)個能夠單獨編址的字節(jié)地址。例如,PDP-11系列計算機,一個16位二進制的字存儲單元可存放兩個字節(jié),可以按字地址尋址,也可以按字節(jié)地址尋址。當(dāng)用字節(jié)地址尋址時,16位的存儲單元占兩個字節(jié)地址。

在一個存儲器中容納的存儲單元總數(shù)通常稱為該存儲器的存儲容量。存儲容量用字?jǐn)?shù)或字節(jié)數(shù)(B)來表示,如64K字,512KB,10MB。外存中為了表示更大的存儲容量,采用MB,GB,TB等單位。其中1KB=2B,1MB=2B,1GB=2B,1TB=2B。B表示字節(jié),一個字節(jié)定義為8個二進制位,所以計算機中一個字的字長通常為8的倍數(shù)。存儲容量這一概念反映了存儲空間的大小。

存儲時間有稱存儲器訪問時間,是指從啟動一次存儲器操作到完成該操作所經(jīng)歷的時間。具體講,從一次讀操作命令發(fā)出到該操作完成,將數(shù)據(jù)讀入數(shù)據(jù)緩沖寄存器為止所經(jīng)歷的時間,即為存儲器存取時間。

存儲周期是指連續(xù)啟動兩次獨立的存儲器操作(如連續(xù)兩次讀操作)所需間隔的最小時間。通常,存儲周期略大于存儲時間,其時間單位為ns

存儲器技術(shù)的發(fā)展使存儲器系統(tǒng)的性能得到提高,盡管峰值速率依然是存儲器技術(shù)最重要的參數(shù)之一,但其它結(jié)構(gòu)參數(shù)也極大地影響存儲器系統(tǒng)的性能。

存儲器技術(shù)大多數(shù)根據(jù)其運行速度來命名。例如,PC100 SDRAM器件是指數(shù)據(jù)速率為100MHz的存儲技術(shù),PC133則表示數(shù)據(jù)速率為133MHz,等等。盡管這種命名的習(xí)慣隨著時間發(fā)展而變化,但通常還是能給潛在買家提供關(guān)于存儲器運行速度的信息。事實上,今天的主流存儲技術(shù)都是按照其峰值數(shù)據(jù)速率來命名的,這將繼續(xù)成為評估存儲系統(tǒng)性能的要素之一。不過,在實際系統(tǒng)中,沒有存儲器能完全工作在其峰值速率下。

從寫命令轉(zhuǎn)換到讀命令,在某個時間訪問某個地址,以及刷新數(shù)據(jù)等操作都要求數(shù)據(jù)總線在一定時間內(nèi)保持休止?fàn)顟B(tài),這樣就不能充分利用存儲器通道。此外,寬并行總線和DRAM內(nèi)核預(yù)取都經(jīng)常導(dǎo)致不必要的大數(shù)據(jù)量存取。在指定的時間段內(nèi),存儲器控制器能存取的有用數(shù)據(jù)稱為有效數(shù)據(jù)速率,這很大程度上取決于系統(tǒng)的特定應(yīng)用。有效數(shù)據(jù)速率隨著時間而變化,常低于峰值數(shù)據(jù)速率。在某些系統(tǒng)中,有效數(shù)據(jù)速率可下降到峰值速率的10[%]以下。

表1:每百周期發(fā)生兩個總線轉(zhuǎn)換時的有效數(shù)據(jù)速率和峰值數(shù)據(jù)速率

通常,這些系統(tǒng)受益于那些能產(chǎn)生更高有效數(shù)據(jù)速率的存儲器技術(shù)的變化。在CPU方面存在類似的現(xiàn)象,最近幾年諸如AMD和 Transmeta等公司已經(jīng)指出,在測量基于CPU的系統(tǒng)的性能時,時鐘頻率不是唯一的要素。存儲器技術(shù)已經(jīng)很成熟,峰值速率和有效數(shù)據(jù)速率或許并不比以前匹配的更好。盡管峰值速率依然是存儲器技術(shù)最重要的參數(shù)之一,但其他結(jié)構(gòu)參數(shù)也可以極大地影響存儲器系統(tǒng)的性能。

影響有效數(shù)據(jù)速率的參數(shù)

有幾類影響有效數(shù)據(jù)速率的參數(shù),其一是導(dǎo)致數(shù)據(jù)總線進入若干周期的停止?fàn)顟B(tài)。在這類參數(shù)中,總線轉(zhuǎn)換、行周期時間、CAS延時以及RAS到CAS的延時(tRCD)引發(fā)系統(tǒng)結(jié)構(gòu)中的大部分延遲問題。

總線轉(zhuǎn)換本身會在數(shù)據(jù)通道上產(chǎn)生非常長的停止時間。以GDDR3系統(tǒng)為例,該系統(tǒng)對存儲器的開放頁不斷寫入數(shù)據(jù)。在這期間,存儲器系統(tǒng)的有效數(shù)據(jù)速率與其峰值速率相當(dāng)。不過,假設(shè)100個時鐘周期中,存儲器控制器從讀轉(zhuǎn)換到寫。由于這個轉(zhuǎn)換需要6個時鐘周期,有效的數(shù)據(jù)速率下降到峰值速率的 94[%]。在這100個時鐘周期中,如果存儲器控制器將總線從寫轉(zhuǎn)換到讀的話,將會丟失更多的時鐘周期。這種存儲器技術(shù)在從寫轉(zhuǎn)換到讀時需要15個空閑周期,這會將有效數(shù)據(jù)速率進一步降低到峰值速率的79[%]。表1顯示出針幾種高性能存儲器技術(shù)類似的計算結(jié)果。

顯然,所有的存儲器技術(shù)并不相同。需要很多總線轉(zhuǎn)換的系統(tǒng)設(shè)計師可以選用諸如XDR、RDRAM或者DDR2這些更高效的技術(shù)來提升性能。另一方面,如果系統(tǒng)能將處理事務(wù)分組成非常長的讀寫序列,那么總線轉(zhuǎn)換對有效帶寬的影響最小。不過,其他的增加延遲現(xiàn)象,例如庫(bank)沖突會降低有效帶寬,對性能產(chǎn)生負(fù)面影響。

DRAM技術(shù)要求庫的頁或行在存取之前開放。一旦開放,在一個最小周期時間,即行周期時間(tRC)結(jié)束之前,同一個庫中的不同頁不能開放。對存儲器開放庫的不同頁存取被稱為分頁遺漏,這會導(dǎo)致與任何tRC間隔未滿足部分相關(guān)的延遲。對于還沒有開放足夠周期以滿足tRC間隙的庫而言,分頁遺漏被稱為庫沖突。而tRC決定了庫沖突延遲時間的長短,在給定的DRAM上可用的庫數(shù)量直接影響庫沖突產(chǎn)生的頻率。

表2:不同存儲技術(shù)的總峰值帶寬以及控制器管腳數(shù)的總線帶寬。

大多數(shù)存儲器技術(shù)有4個或者8個庫,在數(shù)十個時鐘周期具有tRC值。在隨機負(fù)載情況下,那些具有8個庫的內(nèi)核比具有4個庫的內(nèi)核所發(fā)生的庫沖突更少。盡管tRC與庫數(shù)量之間的相互影響很復(fù)雜,但是其累計影響可用多種方法量化。

存儲器讀事務(wù)處理

考慮三種簡單的存儲器讀事務(wù)處理情況。第一種情況,存儲器控制器發(fā)出每個事務(wù)處理,該事務(wù)處理與前一個事務(wù)處理產(chǎn)生一個庫沖突。控制器必須在打開一個頁和打開后續(xù)頁之間等待一個tRC時間,這樣增加了與頁循環(huán)相關(guān)的最大延遲時間。在這種情況下的有效數(shù)據(jù)速率很大程度上決定于I/O,并主要受限于DRAM內(nèi)核電路。最大的庫沖突頻率將有效帶寬削減到當(dāng)前最高端存儲器技術(shù)峰值的20[%]到30[%]。

在第二種情況下,每個事務(wù)處理都以隨機產(chǎn)生的地址為目標(biāo)。此時,產(chǎn)生庫沖突的機會取決于很多因素,包括tRC和存儲器內(nèi)核中庫數(shù)量之間的相互作用。tRC值越小,開放頁循環(huán)地越快,導(dǎo)致庫沖突的損失越小。此外,存儲器技術(shù)具有的庫越多,隨機地址存取庫沖突的機率就越小。

第三種情況,每個事務(wù)處理就是一次頁命中,在開放頁中尋址不同的列地址。控制器不必訪問關(guān)閉頁,允許完全利用總線,這樣就得到一種理想的情況,即有效數(shù)據(jù)速率等于峰值速率。

第一種和第三種情況都涉及到簡單的計算,隨機情況受其他的特性影響,這些特性沒有包括在DRAM或者存儲器接口中。存儲器控制器仲裁和排隊會極大地改善庫沖突頻率,因為更有可能出現(xiàn)不產(chǎn)生沖突的事務(wù)處理,而不是那些導(dǎo)致庫沖突的事務(wù)處理。

然而,增加存儲器隊列深度未必增加不同存儲器技術(shù)之間的相對有效數(shù)據(jù)速率。例如,即使增加存儲器控制隊列深度,XDR的有效數(shù)據(jù)速率也比 GDDR3高20[%]。存在這種增量主要是因為XDR具有更高的庫數(shù)量以及更低的tRC值。一般而言,更短的tRC間隔、更多的庫數(shù)量以及更大的控制器隊列能產(chǎn)生更高的有效帶寬。

實際上,很多效率限制現(xiàn)象是與行存取粒度相關(guān)的問題。tRC約束本質(zhì)上要求存儲器控制器從新開放的行中存取一定量的數(shù)據(jù),以確保數(shù)據(jù)管線保持充滿。事實上,為保持?jǐn)?shù)據(jù)總線無中斷地運行,在開放一個行之后,只須讀取很少量的數(shù)據(jù),即使不需要額外的數(shù)據(jù)。

另外一種減少存儲器系統(tǒng)有效帶寬的主要特性被歸類到列存取粒度范疇,它規(guī)定了每次讀寫操作必須傳輸?shù)臄?shù)據(jù)量。與之相反,行存取粒度規(guī)定每個行激活(一般指每個RAS的CAS操作)需要多少單獨的讀寫操作。列存取粒度對有效數(shù)據(jù)速率具有不易于量化的巨大影響。因為它規(guī)定一個讀或?qū)懖僮髦行枰獋鬏數(shù)淖钚?shù)據(jù)量,列存取粒度給那些一次只需要很少數(shù)據(jù)量的系統(tǒng)帶來了問題。例如,一個需要來自兩列各8字節(jié)的16字節(jié)存取粒度系統(tǒng),必須讀取總共32字節(jié)以存取兩個位置。因為只需要32個字節(jié)中的16個字節(jié),系統(tǒng)的有效數(shù)據(jù)速率降低到峰值速率的50[%]。總線帶寬和脈沖時間長度這兩個結(jié)構(gòu)參數(shù)規(guī)定了存儲器系統(tǒng)的存取粒度。

表3:目前主流存儲技術(shù)的存取粒度和總線帶寬值。

總線帶寬是指連接存儲器控制器和存儲器件之間的數(shù)據(jù)線數(shù)量。它設(shè)定最小的存取粒度,因為對于一個指定的存儲器事務(wù)處理,每條數(shù)據(jù)線必須至少傳遞一個數(shù)據(jù)位。而脈沖時間長度則規(guī)定對于指定的事務(wù)處理,每條數(shù)據(jù)線必須傳遞的位數(shù)量。每個事務(wù)處理中的每條數(shù)據(jù)線只傳一個數(shù)據(jù)位的存儲技術(shù),其脈沖時間長度為1。總的列存取粒度很簡單:列存取粒度=總線寬度×脈沖時間長度。

很多系統(tǒng)架構(gòu)僅僅通過增加DRAM器件和存儲總線帶寬就能增加存儲系統(tǒng)的可用帶寬。畢竟,如果4個400MHz數(shù)據(jù)速率的連接可實現(xiàn) 1.6GHz的總峰值帶寬,那么8個連接將得到3.2GHz。增加一個DRAM器件,電路板上的連線以及ASIC的管腳就會增多,總峰值帶寬相應(yīng)地倍增。

首要的是,架構(gòu)師希望完全利用峰值帶寬,這已經(jīng)達到他們通過物理設(shè)計存儲器總線所能達到的最大值。具有256位甚或512位存儲總線的圖形控制器已并不鮮見,這種控制器需要1,000個,甚至更多的管腳。封裝設(shè)計師、ASIC底層規(guī)劃工程師以及電路板設(shè)計工程師不能找到采用便宜的、商業(yè)上可行的方法來對這么多信號進行布線的硅片區(qū)域。僅僅增加總線寬度來獲得更高的峰值數(shù)據(jù)速率,會導(dǎo)致因為列存取粒度限制而降低有效帶寬。

假設(shè)某個特定存儲技術(shù)的脈沖時間長度等于1,對于一個存儲器處理,512位寬系統(tǒng)的存取粒度為512位(或者64字節(jié))。如果控制器只需要一小段數(shù)據(jù),那么剩下的數(shù)據(jù)就被浪費掉,這就降低了系統(tǒng)的有效數(shù)據(jù)速率。例如,只需要存儲系統(tǒng)32字節(jié)數(shù)據(jù)的控制器將浪費剩余的32字節(jié),進而導(dǎo)致有效的數(shù)據(jù)速率等于50[%]的峰值速率。這些計算都假定脈沖時間長度為1。隨著存儲器接口數(shù)據(jù)速率增加的趨勢,大多數(shù)新技術(shù)的最低脈沖時間長度都大于1。

內(nèi)核預(yù)取

一種稱為內(nèi)核預(yù)取的功能主要負(fù)責(zé)增加最小的脈沖時間長度。DRAM內(nèi)核電路不能跟上I/O電路速度的速增。由于數(shù)據(jù)不能再連續(xù)地從內(nèi)核中取出以確保控制器需求,內(nèi)核通常為I/O提供比DRAM總線寬度更大的數(shù)據(jù)集。

本質(zhì)上,內(nèi)核傳輸足夠的數(shù)據(jù)到接口電路,或者從接口電路傳輸足夠的數(shù)據(jù),以使接口電路保持足夠長時間的繁忙狀態(tài),以便讓內(nèi)核準(zhǔn)備下一個操作。例如,假設(shè)DRAM內(nèi)核每個納秒才能對操作響應(yīng)一次。不過,接口可以支持每納秒兩位的數(shù)據(jù)速率。

DRAM內(nèi)核每次操作取兩個數(shù)據(jù)位,而不是一個數(shù)據(jù)位,因而不必浪費接口一半的容量。在接口傳輸數(shù)據(jù)之后,內(nèi)核已經(jīng)準(zhǔn)備好響應(yīng)下一個請求,而不需增加延時。增加的內(nèi)核預(yù)取導(dǎo)致最小脈沖時間長度增加為2,這將直接影響列存取粒度。

對于每個增加到總線寬度的額外信號,存儲器接口將傳輸兩個額外的數(shù)據(jù)位。因此具有最小脈沖時間長度為2的512位寬的存儲系統(tǒng),其取粒度為 1,024位(128字節(jié))。很多系統(tǒng)對最小存取粒度的問題并不敏感,因為它們存儲大量的數(shù)據(jù)。不過,某些系統(tǒng)依賴存儲器系統(tǒng)提供小的數(shù)據(jù)單元,并獲益于更窄、更有效的存儲器技術(shù)。

電子發(fā)燒友App

電子發(fā)燒友App

評論