高速緩沖存儲器

高速緩沖存儲器(Cache)其原始意義是指存取速度比一般隨機存取記憶體(RAM)來得快的一種RAM,一般而言它不像系統主記憶體那樣使用DRAM技術,而使用昂貴但較快速的SRAM技術,也有快取記憶體的名稱。

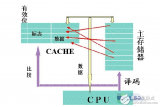

高速緩沖存儲器是存在于主存與CPU之間的一級存儲器, 由靜態存儲芯片(SRAM)組成,容量比較小但速度比主存高得多, 接近于CPU的速度。在計算機存儲系統的層次結構中,是介于中央處理器和主存儲器之間的高速小容量存儲器。它和主存儲器一起構成一級的存儲器。高速緩沖存儲器和主存儲器之間信息的調度和傳送是由硬件自動進行的。

高速緩沖存儲器最重要的技術指標是它的命中率。

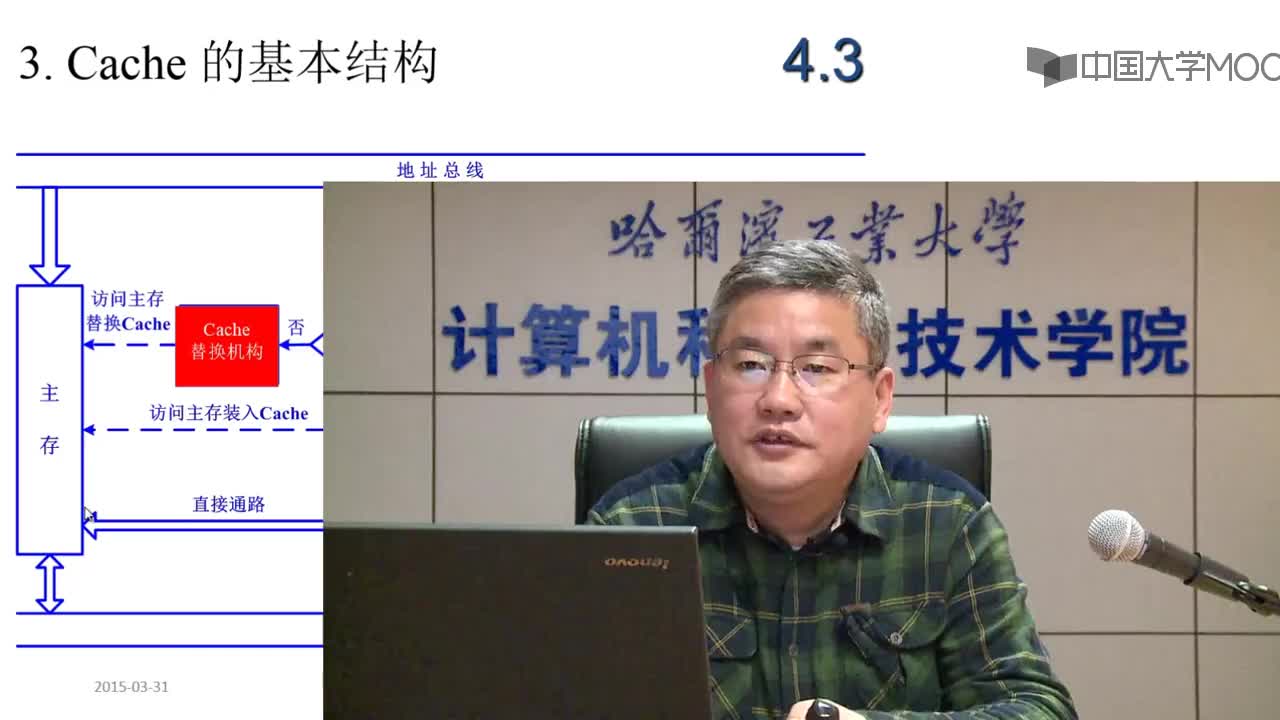

主要由三大部分組成:

Cache存儲體:存放由主存調入的指令與數據塊。

地址轉換部件:建立目錄表以實現主存地址到緩存地址的轉換。

替換部件:在緩存已滿時按一定策略進行數據塊替換,并修改地址轉換部件。

高速緩沖存儲器作用介紹

高速緩沖存儲器(Cache)實際上是為了把由DRAM組成的大容量內存儲器都看做是高速存儲器而設置的小容量局部存儲器,一般由高速SRAM構成。這種局部存儲器是面向CPU的,引入它是為減小或消除CPU與內存之間的速度差異對系統性能帶來的影響。Cache 通常保存著一份內存儲器中部分內容的副本(拷貝),該內容副本是最近曾被CPU使用過的數據和程序代碼。

在計算機技術發展過程中,主存儲器存取速度一直比中央處理器操作速度慢得多,使中央處理器的高速處理能力不能充分發揮,整個計算機系統的工作效率受到影響。有很多方法可用來緩和中央處理器和主存儲器之間速度不匹配的矛盾,如采用多個通用寄存器、多存儲體交叉存取等,在存儲層次上采用高速緩沖存儲器也是常用的方法之一。很多大、中型計算機以及新近的一些小型機、微型機也都采用高速緩沖存儲器。

高速緩沖存儲器的容量一般只有主存儲器的幾百分之一,但它的存取速度能與中央處理器相匹配。根據程序局部性原理,正在使用的主存儲器某一單元鄰近的那些單元將被用到的可能性很大。因而,當中央處理器存取主存儲器某一單元時,計算機硬件就自動地將包括該單元在內的那一組單元內容調入高速緩沖存儲器,中央處理器即將存取的主存儲器單元很可能就在剛剛調入到高速緩沖存儲器的那一組單元內。于是,中央處理器就可以直接對高速緩沖存儲器進行存取。在整個處理過程中,如果中央處理器絕大多數存取主存儲器的操作能為存取高速緩沖存儲器所代替,計算機系統處理速度就能顯著提高。

CPU中高速緩沖存儲器的作用

高速緩沖存儲器(Cache)其原始意義是指存取速度比一般隨機存取記憶體(RAM)來得快的一種RAM,一般而言它不像系統主記憶體那樣使用DRAM技術,而使用昂貴但較快速的SRAM技術,也有快取記憶體的名稱。

高速緩沖存儲器是存在于主存與CPU之間的一級存儲器, 由靜態存儲芯片(SRAM)組成,容量比較小但速度比主存高得多, 接近于CPU的速度。在計算機存儲系統的層次結構中,是介于中央處理器和主存儲器之間的高速小容量存儲器。它和主存儲器一起構成一級的存儲器。高速緩沖存儲器和主存儲器之間信息的調度和傳送是由硬件自動進行的。

高速緩沖存儲器最重要的技術指標是它的命中率。

高速緩沖存儲器工作原理

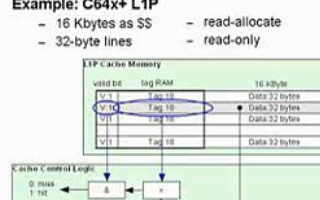

高速緩沖存儲器通常由高速存儲器、聯想存儲器、替換邏輯電路和相應的控制線路組成。在有高速緩沖存儲器的計算機系統中,中央處理器存取主存儲器的地址劃分為行號、列號和組內地址三個字段。于是,主存儲器就在邏輯上劃分為若干行;每行劃分為若干的存儲單元組;每組包含幾個或幾十個字。高速存儲器也相應地劃分為行和列的存儲單元組。二者的列數相同,組的大小也相同,但高速存儲器的行數卻比主存儲器的行數少得多。

聯想存儲器用于地址聯想,有與高速存儲器相同行數和列數的存儲單元。當主存儲器某一列某一行存儲單元組調入高速存儲器同一列某一空著的存儲單元組時,與聯想存儲器對應位置的存儲單元就記錄調入的存儲單元組在主存儲器中的行號。

當中央處理器存取主存儲器時,硬件首先自動對存取地址的列號字段進行譯碼,以便將聯想存儲器該列的全部行號與存取主存儲器地址的行號字段進行比較:若有相同的,表明要存取的主存儲器單元已在高速存儲器中,稱為命中,硬件就將存取主存儲器的地址映射為高速存儲器的地址并執行存取操作;若都不相同,表明該單元不在高速存儲器中,稱為脫靶,硬件將執行存取主存儲器操作并自動將該單元所在的那一主存儲器單元組調入高速存儲器相同列中空著的存儲單元組中,同時將該組在主存儲器中的行號存入聯想存儲器對應位置的單元內。

當出現脫靶而高速存儲器對應列中沒有空的位置時,便淘汰該列中的某一組以騰出位置存放新調入的組,這稱為替換。確定替換的規則叫替換算法,常用的替換算法有:最近最少使用算法(LRU)、先進先出法(FIFO)和隨機法(RAND)等。替換邏輯電路就是執行這個功能的。另外,當執行寫主存儲器操作時,為保持主存儲器和高速存儲器內容的一致性,對命中和脫靶須分別處理。

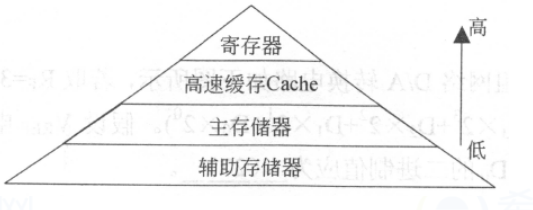

存儲層次

主-輔存存儲層次 由于計算機主存容量相對于程序員所需要的容量來說總是太小,程序與數據從輔存調入主存是由程序員自己安排的,程序員必須花費很大精力和時間把大程序預先分成塊,確定好這些程序塊在輔存中的位置和裝入主存的地址,而且還要預先安排好程序運行時各塊如何和何時調入調出,因此存在存儲空間的分配問題。操作系統的形成和發展使得程序員盡可能擺脫主、輔存之間的地址定位,同時形成了支持這些功能的“輔助硬件”,通過軟件、硬件的結合,把主存和輔存統一成了一個整體,如圖所示。這時,由主存、輔存形成了一個存儲層次,即存儲系統。從整體看,其速度接近于主存的速度,其容量則接近于輔存的容量,而每位的平均價格也接近于廉價的慢速的輔存平均價格。這種系統不斷發展和完善,就逐步形成了現在廣泛使用的虛擬存儲系統。在系統中,應用程序員可用機器指令地址碼對整個程序統一編址,如同程序員具有對應這個地址碼寬度的全部虛存空間一樣。該空間可以比主存實際空間大得多,以致可以存得下整個程序。這種指令地址碼稱為虛地址(虛存地址、虛擬地址)或邏輯地址,其對應的存儲容量稱為虛存容量或虛存空間;而把實際主存的地址稱為物理地址、實(存)地址,其對應的存儲容量稱為主存容量、實存容量或實(主)存空間

主-輔存存儲層次

CACHE-主存存儲層次

當用虛地址訪問主存時,機器自動地把它經輔助軟件、硬件變換成主存實地址。查看這個地址所對應的單元內容是否已經裝入主存,如果在主存就進行訪問,如果不在主存內就經輔助軟件、硬件把它所在的那塊程序和數據由輔存調入主存,而后進行訪問。這些操作都不必由程序員來安排,也就是說,對應用程員員是透明的。 主-輔存層次解決了存儲器大容量要求和低成本之間的矛盾。 在速度方面,計算機的主存和CPU直保持了大約一個數量級的差距。顯然這個差距限制了CPU速度潛力的發揮。為了彌合這個差距,僅采用一種工藝的單一存儲器是行不通的,必須進一步從計算機系統結構和組織上去研究。設置高速緩沖存儲器(Cache)是解決存取速度的重要方法。在CPU和主存中間設置高速緩沖存儲器,構成高速緩存(Cache)-主存層次,要求Cache在速度上能跟得上CPU的要求。Cache-主存間的地址映象和調度吸取了比它較早出現的主-輔存存儲層次的技術,不同的是因其速度要求高,不是由軟、硬件結合而完全由硬件來實現,如圖所示。

地址映象與轉換

地址映象是指某一數據在內存中的地址與在緩沖中的地址,兩者之間的對應關系。下面介紹三種地址映象的方式。

1.全相聯方式

地址映象規則:主存的任意一塊可以映象到Cache中的任意一塊

(1) 主存與緩存分成相同大小的數據塊。

(2) 主存的某一數據塊可以裝入緩存的任意一塊空間中。如果Cache的塊數為Cb,主存的塊數為Mb,則映象關系共有Cb×Mb種。

目錄表存放在相關(聯)存儲器中,其中包括三部分:數據塊在主存的塊地址、存入緩存后的塊地址、及有效位(也稱裝入位)。由于是全相聯方式,因此,目錄表的容量應當與緩存的塊數相同。

優點:命中率比較高,Cache存儲空間利用率高。

缺點:訪問相關存儲器時,每次都要與全部內容比較,速度低,成本高,因而應用少。

2.直接相聯方式

地址映象規則: 主存儲器中一塊只能映象到Cache的一個特定的塊中。

(1) 主存與緩存分成相同大小的數據塊。

(2) 主存容量應是緩存容量的整數倍,將主存空間按緩存的容量分成區,主存中每一區的塊數與緩存的總塊數相等。

(3) 主存中某區的一塊存入緩存時只能存入緩存中塊號相同的位置。

主存中各區內相同塊號的數據塊都可以分別調入緩存中塊號相同的地址中,但同時只能有一個區的塊存入緩存。由于主、緩存塊號相同,因此,目錄登記時,只記錄調入塊的區號即可。主、緩存塊號及塊內地址兩個字段完全相同。目錄表存放在高速小容量存儲器中,其中包括二部分:數據塊在主存的區號和有效位。目錄表的容量與緩存的塊數相同。

優點:地址映象方式簡單,數據訪問時,只需檢查區號是否相等即可,因而可以得到比較快的訪問速度,硬件設備簡單。

缺點:替換操作頻繁,命中率比較低。

3.組相聯映象方式

組相聯的映象規則:

(1) 主存和Cache按同樣大小劃分成塊。

(2) 主存和Cache按同樣大小劃分成組。

(3) 主存容量是緩存容量的整數倍,將主存空間按緩沖區的大小分成區,主存中每一區的組數與緩存的組數相同。

(4) 當主存的數據調入緩存時,主存與緩存的組號應相等,也就是各區中的某一塊只能存入緩存的同組號的空間內,但組內各塊地址之間則可以任意存放,即從主存的組到Cache的組之間采用直接映象方式;在兩個對應的組內部采用全相聯映象方式。

主存地址與緩存地址的轉換有兩部分,組地址是按直接映象方式,按地址進行訪問,而塊地址是采用全相聯方式,按內容訪問。組相聯的地址轉換部件也是采用相關存儲器實現。

優點:塊的沖突概率比較低,塊的利用率大幅度提高,塊失效率明顯降低。

缺點:實現難度和造價要比直接映象方式高。

電子發燒友App

電子發燒友App

評論