全球 3D NAND 價格近來快速崩跌,紫光集團旗下的長江存儲肩負打破國內“零”存儲自制率之重任,以”光速”的氣勢加入這場存儲世紀大戰。除了武漢 12 寸廠進入生產,南京廠也將于年內動工,加上成都廠,紫光將先后啟動三大基地生產 3D NAND 芯片,即使合計投資金額高達 1,800 億人民幣,花十年目標換來比肩巨人三星、東芝的機會,紫光此舉看來大膽但卻值得!

大陸占全球總存儲的消耗量 50 %,但芯片自制率幾乎是零,全數仰賴美國、日本、韓國進口,紫光集團旗下的長江存儲投入 3D NAND 研發近四年時間,今年 32 層芯片進入生產,紫光集團董事長趙偉國在南京舉行的“中國芯片發展高峰論壇 China IC Summit ”中驕傲指出,中國已有第一支采用自己自主研發芯片所生產的U盤。

紫光位于武漢的 12 寸晶圓廠今年投入32 層 3D NAND 芯片生產,目前以月產能2000 片小量生產,該生產基地規劃三座大型 12 寸晶圓廠,合計單月產能上看 30 萬片。

不僅如此,紫光位于南京的半導體項目也將投入 3D NAND 芯片生產,目前南京基地已進入整地階段,最快將于年底前動工,同時,成都的半導體項目也計劃投入 3D NAND 芯片,合計紫光在武漢、南京、成都三大生產基地將投入 1,800 億人民幣生產 3D NAND 芯片,以沖刺經濟規模的戰略,換取比肩國際大廠的契機。

看好 3D NAND 未來五年需求大好,技術瓶頸存在,紫光要用力趕上

由于全球存儲芯片價格崩跌之勢已現,對于紫光在此時大動作進行擴產,也讓外界不禁擔心,紫光若啟動三大生產基地生產 3D NAND 芯片,會不會演變成長期產業供過于求的危機?

甫從華為離職加入紫光集團擔任執行副總裁的楚慶獨家對 DT 君分析 3D NAND后續走勢看法 ,楚慶認為,無論是從供給面或是技術面來看,未來 NANDFlash 產業前景都非常樂觀,今年旗艦級智能手機的存儲容量是 256GB ,明年會成長到 512GB ,消耗的存儲芯片越來越可觀,但3D NAND技術會遇到不小瓶頸。

他表示,去年華為因為 NAND Flash 芯片缺貨造成銷售額短少 40 億美元,內部更因此成立戰略領導小組來分析因應供給短缺的情況。

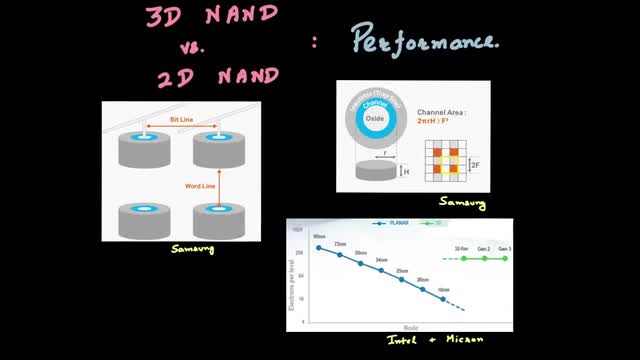

楚慶分析,雖然 3D NAND 技術不斷往上迭,從 32 層迭到 64 層,但到了 96 層技術,就不會是一年密度增長一倍的速度了,等堆迭到了 128 層,之后的發展可能是堆迭到 144 層左右,技術挑戰越來越艱難,供給不會一直順利產出,因此,紫光對于未來五年的存儲市場抱持樂觀態度。

對于眼前 3D NAND 產能過剩,楚慶反而認為這是短暫現象,因為現有的幾家半導體大廠包括三星、東芝都是同步發展 96 層技術,伴隨技術突破,一定會有不少產能增加,形成供過于求,但這些新產能很快就會被新增的需求吃掉。

再者,楚慶也認為未來 3D NAND 技術從 96 層堆迭到 128 層技術后,每一個世代的技術進展會從原本的 12 個月,拉長至 18 個月才能達到,而紫光在存儲領域也會有全新的戰略來因應,外界可以拭目以待。

長江存儲 Xtacking 驚艷背后的辛酸,楊士寧:選擇這條路要很大勇氣

今年國際存儲大廠三星、東芝、美光、西部數據、SK海力士已進入 64 層 3D NAND 技術的生產,并且完成 96 層 3D NAND 技術研發,寄希望于 2019 年投產,三星更要搶在今年第四季率先小幅量產 96 層芯片,除此之外,眾家大廠未來更要再往上朝 128 層 3D NAND 技術開發。

長江存儲身為后發者,為了要快速趕上國際大廠的腳步,計劃在 64 層技術之后,會跳過 96 層技術,直攻 128 層 3D NAND 芯片,就技術規劃來看,業界傳出紫光將會以兩顆 64 層芯片直接做堆迭的方式開發生產。

再者,長江存儲近期提出的 Xtacking 新架構引發全球存儲產業一陣騷動。長江存儲首席執行官楊士寧在 Flash Memory Summit 期間透露, Xtacking 架構有很多好處,但挑戰也不少,決定選擇走上這一條道路需要勇氣,因為要讓這個技術發揮作用并不容易,他和紫光集團全球執行副總裁高啟全來回討論多次才下此決定。

Xtacking 架構技術的基礎是來自于武漢新芯開發多年的 CMOS 成像器的打線封裝技術( Wafer Bonding ),長江存儲為了將該技術用于 3D NAND 開發,將其“幾微米的間距”縮小到僅約 100 nm。

當中,最為困難的一部分是存儲和邏輯元件的對淮技術,使用位于晶圓上方和下方的攝影機,透過等離子體活化被擠壓在一起的晶片表面,再以低溫退火做處理。然后,于 I/O 晶圓的背面進行加工,以便在晶片背面形成焊墊。

Xtacking 架構將邏輯和存儲元件上下相迭且分開加工,有效解除 I/O 傳輸瓶頸

而對于Xtacking技術細節,長江存儲聯席首席技術官湯強出席“中國芯片發展高峰論壇 China IC Summit ”時有非常詳盡的解說。

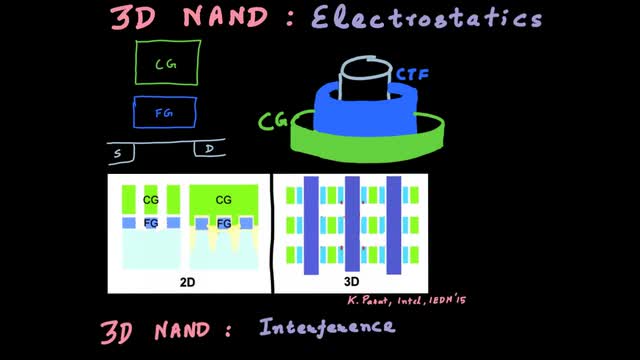

湯強表示, NAND Flash 是串連式的存儲,傳統的 2D NAND 技術是二維平面結構,隨著尺寸微縮越來越小,面臨的挑戰越來越多,這其中包括成本過高,以及越來越多的干擾信號等等問題,因此,大家開始想解決方案,把串連式的存儲從平面豎起來,發展成立體三維結構的 3D NAND,可大幅提高存儲密度,同時也避開光刻上成本的增加,也解決干擾技術。

不過, 3D NAND 技術也同樣面臨挑戰,主要面臨來自三大方面,包括 I/O 傳輸速度、存儲密度、產品上市周期,而這三大方面正是存儲技術的核心競爭力之所在。

湯強解釋,在進行半導體加工時,會先做外圍負責驅動、傳輸功能的邏輯電路元件,之后加工存儲陣列元件,但加工存儲陣列元件時所采用的高溫高壓工藝,會影響之前已經加工完成的邏輯元件,在邏輯電路上的工藝最多只能做到 0.18 微米制程,速度上無法提升,導致 I/O 的線性傳輸會卡住。

長江存儲Xtacking的解決方式,是把外圍邏輯電路和存儲陣列電路兩個模塊分開加工,之后兩個模塊從水平擺放,變成上下堆迭擺放在一起,如此一來可解除 I/O 傳輸瓶頸,有效提升速度,因為在加工外圍邏輯電路的時候,就不會被陣列電路加工時的高溫高壓所影響。

因此,邏輯電路可以采用更為先進的工藝,從 0.18 微米制程的加工技術,放寬到 90 納米、 55 納米、 28 納米,甚至是采用高端的 16 納米、 10 納米制程生產,完全貼緊邏輯電路往前進的步伐。

再者,現在的 I/O 傳輸速度瓶頸是0.8 Gb/秒,將來采用先進工藝后,可以放寬至 3 Gb/秒,這和 DRAM 的傳輸速度可以有效縮短。

為了解決體積問題,并且增加芯片密度,兩塊加工完畢的模組從水平擺放變成堆迭擺放,把外圍電路放在陣列電路之下,這使得 Xtacking 的面積利用率從傳統的 65 %提升至 90 %。

其實也有其他國外大廠采用類似技術,將外圍邏輯電路直接擺放在存儲陣列電路的下面為 PUA,然 Xtacking 技術不一樣之處在于,是分成個模塊同時做,可縮短研發周期,工藝不會受到干擾,然后再將模塊拼再一起,未來甚至可以把外圍邏輯電路交給外面做代工,靈活度提升。

長江存儲將從第二代 3D NAND 采用 Xtacking 架構,讓優勢盡情發揮

然而, Xtacking 技術也同樣面臨三大難題,第一是硅片的平整度,隨著存儲堆迭變高,平整度地挑戰是很大的。第二是對孔的對淮精度,要把整片硅片所有的孔都對淮,并且接通,這相當不容易。第三是接口材料的選擇,長江存儲甚至和合作供應商合作研發一款新的 CMP 研磨機臺。

在經過多時努力,現在 Xtacking 技術良率提升非常快,結構的可靠性也很好,在編程擦寫 3,000 次之后,可靠度仍是維持一樣。且針對可靠度測試上,包括溫度循環測試(Thermal Cycle )、高溫存儲測試( High Temp. Storage )、電子遷移測試( Electro-migration ),都通過考驗。

長江存儲將從第二代( 64 層技術)的3D NAND 采用 Xtacking 架構,未來各代技術也都會導入。未來 3D NAND 層數堆迭越來越高時,伴隨而來的是外圍電路的占比會變很大,這時,Xtacking 技術的優勢便可以越來越有得發揮。

長江存儲的 Xtacking 技術概念最令人驚艷的是傳輸速度可以達到 3Gbps ,比肩DRAM的傳輸水準,加上明年量產 64 層 3D NAND 后,要一舉直攻 128 層技術,剛好國際大廠在 128 層技術后會放緩腳步,因此有充裕時間可以追趕。

若 Xtacking 技術成功量產,會是國內存儲產業的重大里程碑,更為芯片自主開發的道路注入強心針,且紫光將以武漢、南京、成都三個生產基地投入 3D NAND 芯片生產,下一步要玩經濟規模之戰,以期快速追上國際大廠,快速打破國內“零”自制存儲芯片的現況,并且躋身國際大廠之林。

電子發燒友App

電子發燒友App

評論