首選我們來聊聊時序邏輯中最基礎的部分D觸發器的同步異步,同步復位即復位信號隨系統時鐘的邊沿觸發起作用,異步復位即復位信號不隨系統時鐘的邊沿觸發起作用,置數同理,rst_n表示低電平復位,我們都知道D觸發器是一個具有異步復位異步置數的器件,那么怎么樣Verilog來具體描述這個器件呢,接下來我們就來看一下,

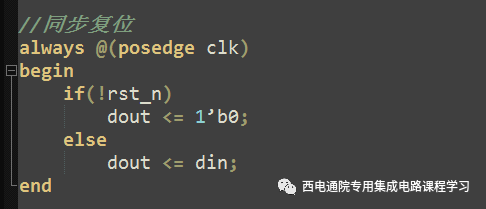

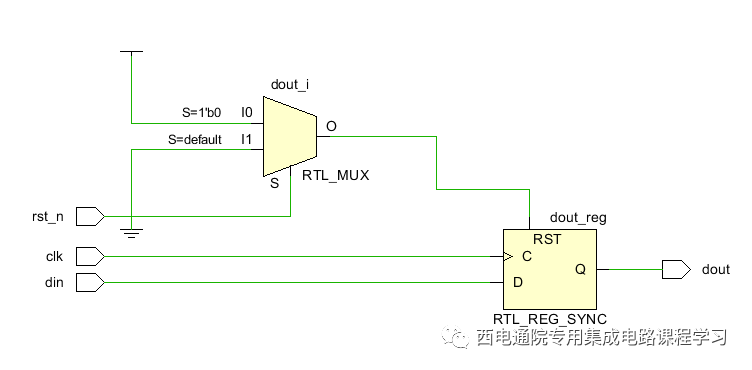

D觸發器的幾種表示形式同步復位

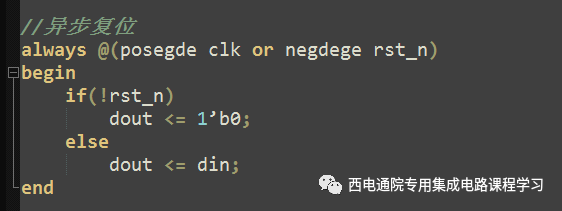

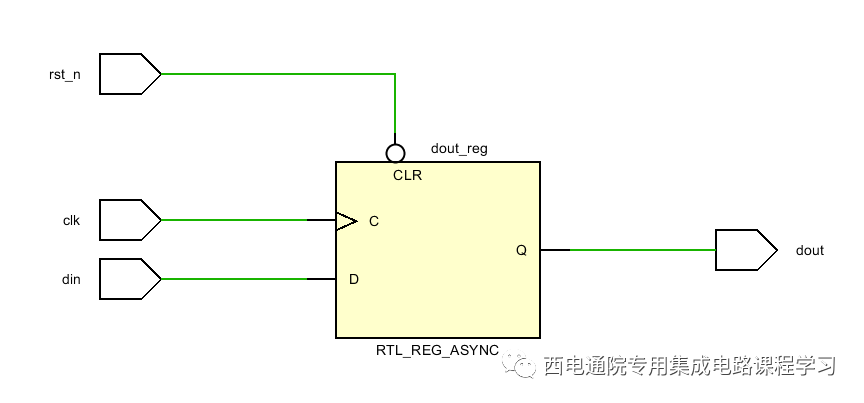

異步復位

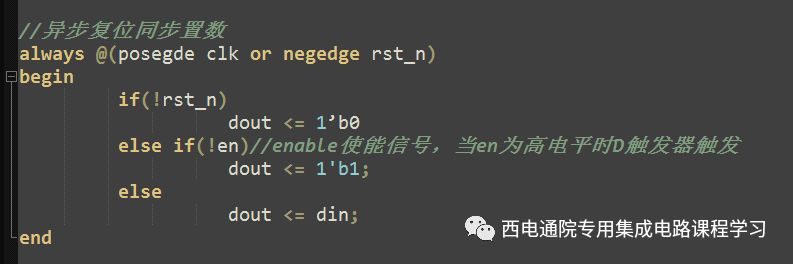

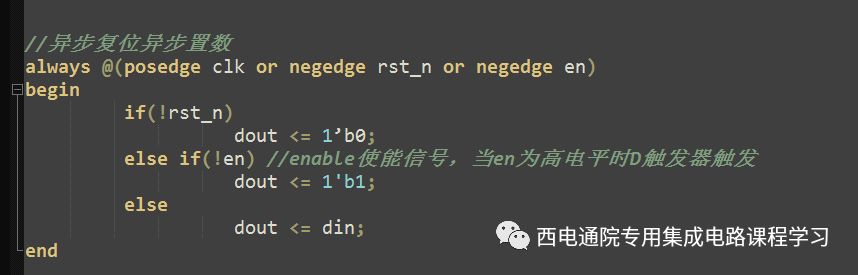

異步置數,同步置數。

異步復位,異步置數

同步異步無非就是一個是否受系統時鐘邊沿觸發,如果想要異步就直接加一個敏感信號就好了。不過一般工程中的書寫形式就是異步復位,不過這種設計方法也有弊端,原因就是時序邏輯的冒險與競爭的問題。

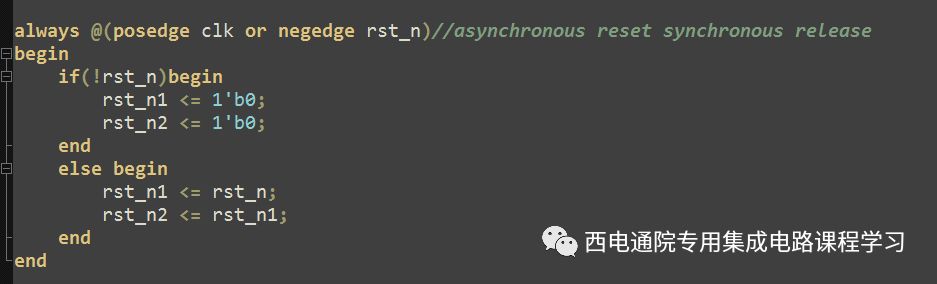

異步復位、同步釋放

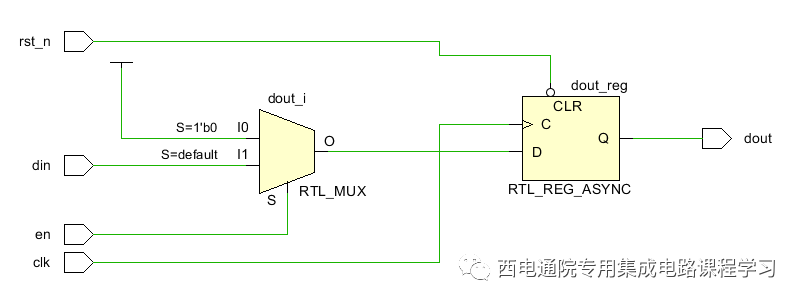

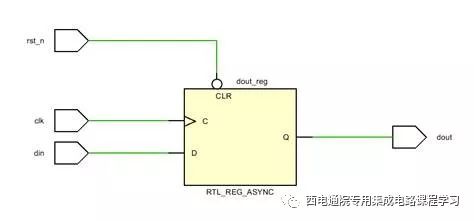

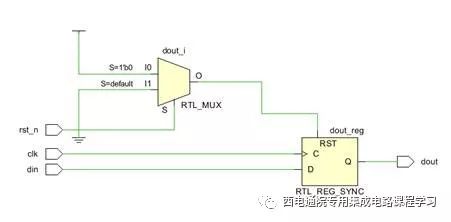

如下圖可以看到異步復位的結構圖,D觸發器是復位優先級高于clk優先級,所以采用通異步復位的方法,但是異步復位D觸發器存在競爭與冒險,比如當clk的上升沿和rst_n的下降沿同時來臨的時候這時候系統應該聽誰的,同樣當clk的上升沿和rst_n的上升沿同時來臨的時候容易使寄存器出現亞穩態。

亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態引時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器輸出一些中間級電平,或者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。這時系統是處于極不穩定的狀態,這也是我們需要考慮的。

有人說既然異步復位會出現冒險競爭那我們使用同步復位不就行了,我們來看看同步復位的邏輯結構圖,同步復位雖然解決了當clk的邊沿來臨的時候rst_n的邊沿也正好來臨所出現的冒險與競爭,但是從綜合的電路上可以看出,多了一個組合邏輯,選擇器(MUX),可想而知如果所有的寄存器復位都是這樣,那會多浪費多少資源。那么這樣就沒有辦法再解決了嗎?答案是有的,一位前輩曾經說過,從正確到完美的道路是十分艱辛的,我們為了追求完美,引入異步復位、同步釋放機制,即解決了同步復位浪費資源問題,又解決了異步復位帶來的亞穩態。

這是復位信號同步化代碼,系統時鐘不變化,還是采用異步復位的方法,但是當復位信號操作時會進入一個同步寄存器,使得復位信號同步化,這樣既避免了異步復位的冒險與競爭,又避免了同步復位耗費太多資源。只需要將復位信號同步化編寫成獨立模塊,然后頂層例化就好了。系統時鐘信號不變化。

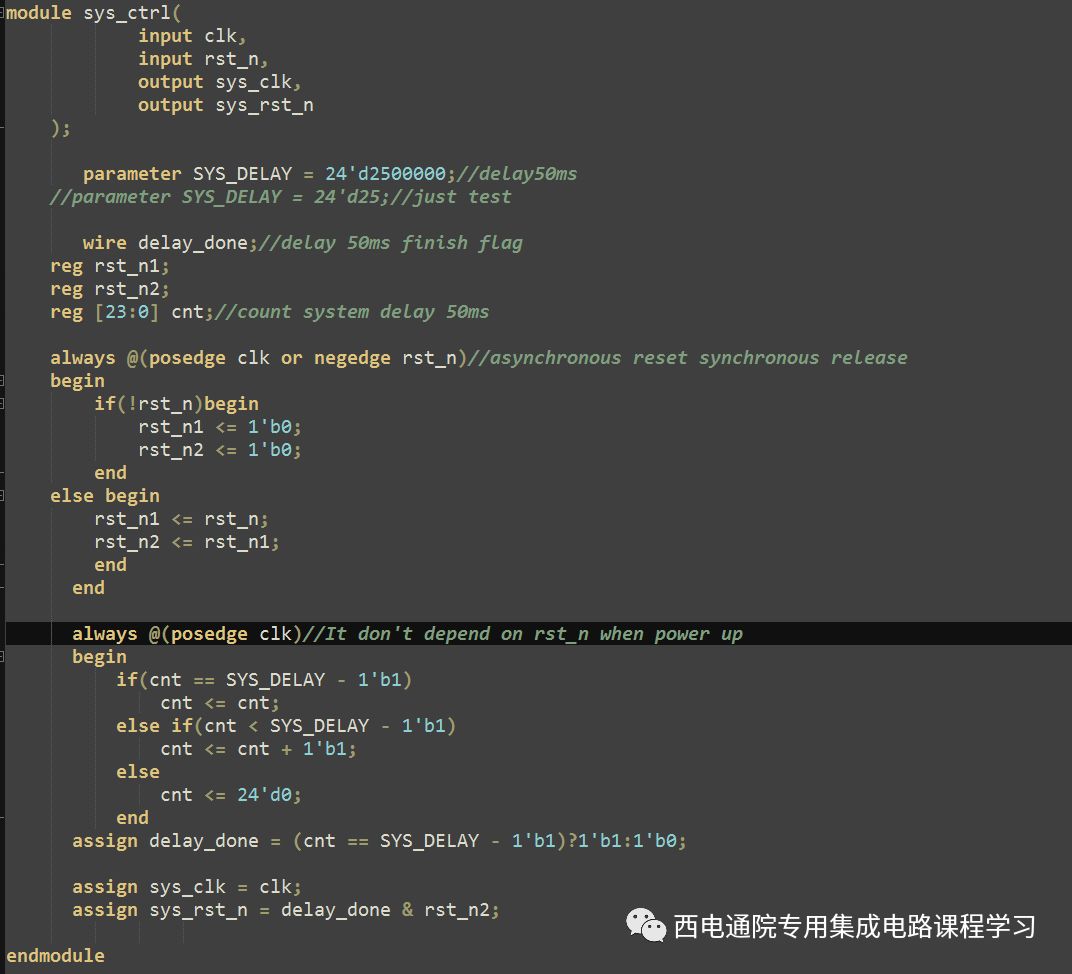

上電延時

開發板接通電源后會有一小段不穩定的狀態,在比較大的工程中,邏輯資源利用的比較多的情況下,如果加上電源后直接進行復位操作,同樣會使寄存器不穩定,所以,類似于按鍵消抖的方法,我們也給板子加電源后延時50ms,當系統穩定后在進行復位操作,再看bingo的書時,他是將這兩個個分成兩個模塊然后實例化到一起,但為了提高代碼的可移植性,我將異步復位同步釋放和上電延時50ms寫在一個模塊。具體實現如下。

對于較小的工程,進行這些操作與否也就無可厚非,如果對于一個項目,需要要求必須盡善盡美,FPGA的優勢便是數字信號處理,速度快,我們在保持速度的前提下,還需要使其準確率也提高,盡量占用少量的資源。這樣異步復位,同步釋放的機制就體現出來了。

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

D觸發器

+關注

關注

3文章

164瀏覽量

47867

原文標題:異步復位同步釋放機制-系統完美穩定

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

D觸發器,CLK突變時,輸入D也突變,觸發器的輸出應該如何判定?

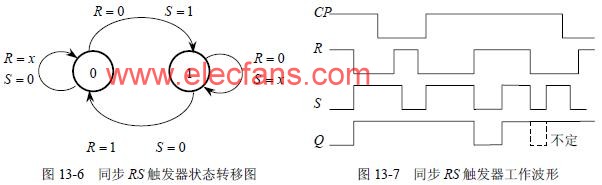

同步RS觸發器原理

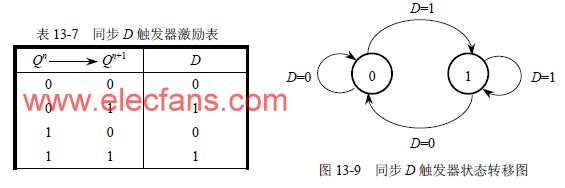

同步D觸發器原理

同步觸發器的觸發方式和空翻問題

D觸發器的幾種表示形式同步復位、同步釋放

D觸發器的幾種表示形式同步復位、同步釋放

評論