上個月在日本召開的VLSI 2019峰會上,臺積電(下稱TSMC)舉辦了一次小型的媒體會,會上他們公開了目前他們在先進制程工藝方面的進度。這篇文章就帶大家來梳理一下目前TSMC的先進工藝進度,對于未來兩到三年半導體代工業界的發展有個前瞻。

圖片來自于WikiChip,下同

注:這篇文章大部分內容翻譯自WikiChip對上述兩次會議中臺積電披露內容的一篇匯總文。由于小編不是學電路或者說電子科班出身,所以文中在電路知識相關內容的翻譯上可能有問題,請各位讀者見諒,如有問題敬請在評論指出。

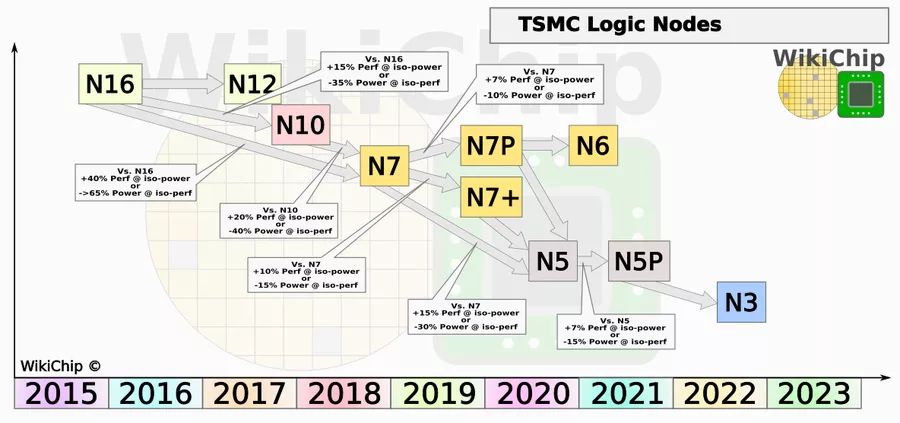

原版7nm工藝(N7)

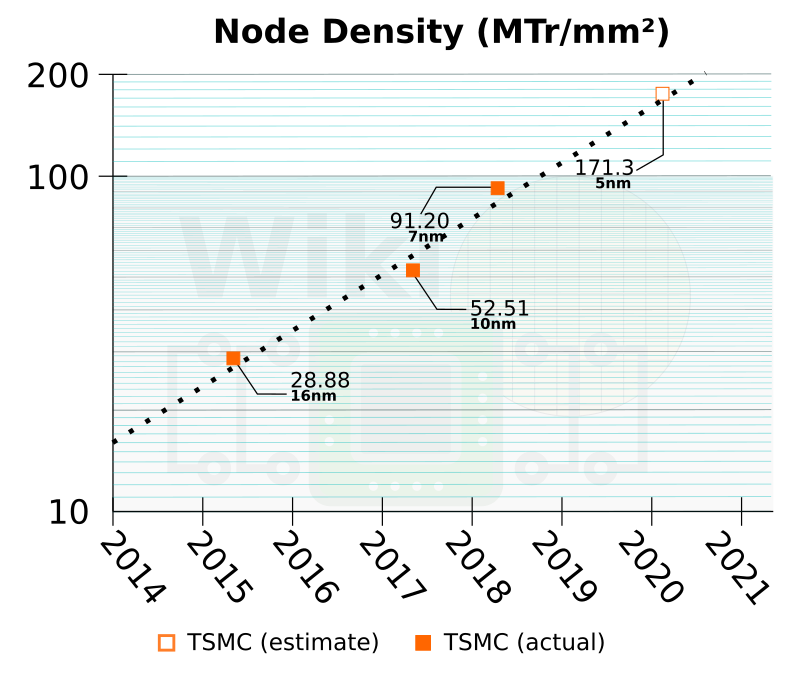

TSMC認為他們的7nm工藝(N7)是目前可用的半導體工藝中最為先進的。在VSLI峰會上面,TSMC披露了7nm工藝的一些技術細節。目前除了少部分主要客戶(小編:某VIDIA),大多數TSMC的客戶都表示將直接從TSMC 16nm節點工藝直接轉到7nm節點工藝。

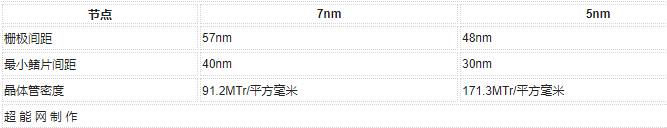

TSMC各節點工藝關鍵特征對比表

TSMC的10nm節點將是一代短命的工藝,看起來更像是一代用于過渡的工藝。相比起16nm節點工藝,7nm可以提供3.3倍的門電路密度,在同等功耗上提供35~40%的速度提升或者可以降低65%的功耗。

不過7nm技術的亮點更加在于TSMC對于良率的控制,根據TSMC給出的信息,得益于在10nm工藝上面的經驗,7nm工藝的成熟速度是有史以來最快的。隨著7nm工藝紛紛被高性能計算領域所使用,TSMC開始分別向移動端客戶和生產250mm^2^以上Die大小的HPC客戶報告不同的缺陷密度。

有趣的是,TSMC發現他們7nm節點工藝的需求在每季度以1%的速度下降著,同時他們利潤的主要來源還是成熟的16nm節點工藝,不過他們認為,7nm工藝將提供整個年度25%的利潤。

第二代7nm工藝(N7P)

TSMC已經開始提供優化版的7nm制程了,他們把這種工藝命名為"N7 Performance-enhanced version",簡寫為N7P,翻譯過來就是7nm性能增強版,一般稱之為“第二代7nm工藝”或者“7nm year 2”。

N7P是在原版基礎上對某些生產步驟(例如FEOL和MOL)進行了優化,從而得到了約7%的性能提升,或者10%的省電效果。

7nm EUV(N7+)

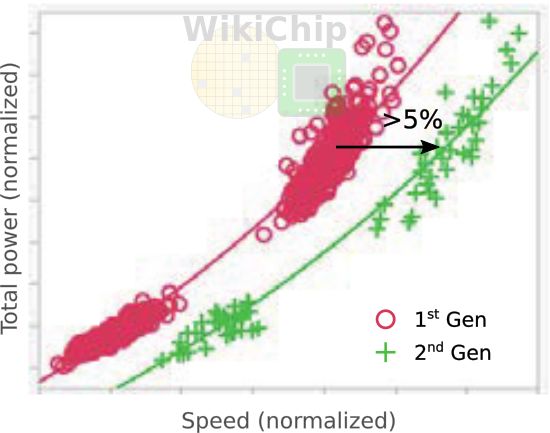

TSMC內部將首次引入EUV(極紫外線光刻)技術的7nm工藝稱之為"N7+",不要把它和上面的“第二代7nm工藝”給搞混了,那種仍然是采用目前常用的DUV(深紫外線光刻)。N7+已經在上個季度進入了量產環節,TSMC表明這種新工藝的產量已經可以達到原來7nm工藝的水平了。

相較于初代7nm工藝,N7+可以提供1.2倍的密度提升,同等功耗水平下提供10%的性能增幅,或者同性能節省15%的功耗。紙面數據上的表現當然是比上面的N7P還要強一些。當然,使用新的EUV技術也意味著需要在物理上重新實現一遍芯片,并且使用新的EUV掩膜。

6nm節點(N6)

6nm節點是N7(初代7nm工藝)的EUV等效工藝,計劃使用比N7+更多的EUV層,它兼容于N7工藝,目的是為大部分客戶提供制程的升級。在N6工藝上,有些N7節點的設計將會采用新的方式來實現,最終將提供約18%的密度提升。

比較特別的是,N6工藝進入實際生產的時間將會比N5還要晚,風險生產將會在明年早些時候開始,在2020末開始工藝爬坡。正因如此,TSMC稱他們將會把在N7+和N5這兩種工藝上學習到的經驗運用于N6上面。

5nm節點(N5)

TSMC 5nm工藝節點(N5)將會是7nm之后的下一個“完全節點(小編注:比如Intel的22nm到14nm為一個完全節點)”,在今年第一季度,它已經進入了風險生產,預計將于明年上半年開始工藝爬坡。N5會廣泛地使用EUV技術,TSMC表示N5節點工藝的發展工藝與N7相似,并且目前已經達到了一個非常高水平的產量。

相較于N7節點,TSMC宣稱N5將提供1.8倍的密度,同功耗15%的性能提升或者同性能30%的節能。同樣地,N5也會像N7那樣為移動端和HPC用途提供兩種額外選項。相比起N7工藝,N5的HPC選項將提供最高達25%的性能提升。

TSMC 5nm節點技術特征預測

在WikiChip的預計中,TSMC 5nm將比Intel和三星的下一個完全節點工藝成熟時間更早。

第二代5nm工藝(N5P)

如同7nm節點時候的情況,TSMC計劃將提供一種5nm工藝的優化版,名稱也類似:N5 Performance-enhanced version,代號N5P。與N7P類似,N5P也在某些生產步驟(例如FEOL和MOL)進行了優化,相比起N5工藝,N5P可以提供同功耗下7%的性能提升或是同性能下15%的省電。

不過目前N5P的具體時間線仍然是未知的,但有跡象表明TSMC會在2020年末或2021年初將其推出。

3nm節點(N3)

TSMC表示他們的3納米工藝進展順利,預計將于2022年左右正式引入。就像我們之前知道的那樣,目前的FinFET已經不能滿足于3nm節點時代的生產了,業界目前計劃引入新的GAA(閘極全環 Gate-all-around)技術。但不能排除TSMC和Intel會繼續使用生產更容易、成本更加低的FinFET,因為它尚有潛力可以被挖掘,而三星已經計劃在3nm上面引入GAA技術了。WikiChip更加傾向于TSMC會繼續在3nm節點上面使用FinFET,而會在隨后的工藝節點中引入GAA技術。目前還沒有更多關于TSMC 3nm工藝的信息。

總結

在成為世界上最大的半導體代工廠之后,TSMC并沒有停止他們的腳步,相反,他們保持著新工藝的研發速度,從目前披露出來的進度來看,他們已經領先于Intel和其他半導體生產商了。先不論這個工藝節點命名中有多少水分,但就目前7nm工藝的表現來看,TSMC確實是對得起“最先進”之名的。

所謂有競爭才有發展,在之前的時代中,TSMC、三星和GF都沒有對Intel構成過像樣的威脅,所以Intel才會在10nm工藝上制定如此激進的目標,導致其難產至今。不過10nm工藝的芯片已經開始出貨了,當然早期10nm的表現肯定是不如現在14nm++的。如果按照Intel以前的做法,他們肯定是會去吃透10nm再轉進下一代7nm節點工藝的,但是競爭對手的速度已經容不得他們慢慢吃透工藝了。前不久Intel的CEO在一場峰會中宣稱將于兩年內提供7nm工藝,那么他們究竟能不能做到呢?讓我們拭目以待。

-

半導體

+關注

關注

334文章

27063瀏覽量

216494 -

VLSI

+關注

關注

0文章

73瀏覽量

42895

原文標題:精華 | 一文梳理臺積電先進制程工藝進度

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

喆塔科技先進制程AI賦能中心&校企聯合實驗室落戶蘇州

英特爾向聯想交付首款18A工藝CPU樣品

晶圓微凸點技術在先進封裝中的應用

三星加速2nm及1.4nm制程投資

芯片微型化挑戰極限,成熟制程被反推向熱潮

臺積電回應先進制程漲價傳聞:定價以策略為導向

臺積電在歐洲技術研討會上展示HBM4的12FFC+和N5制造工藝

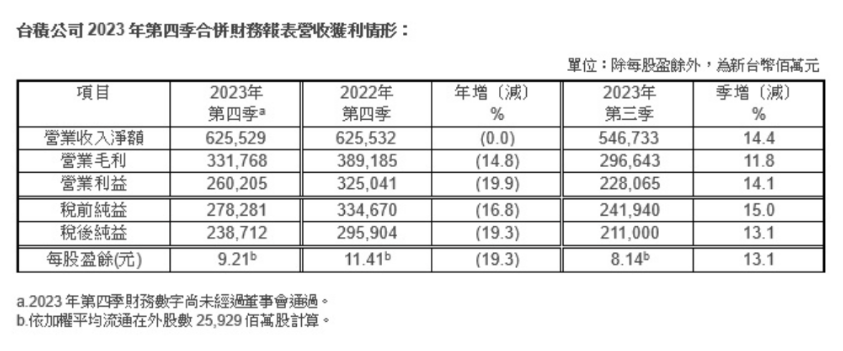

臺積電2023年報:先進制程與先進封裝業務成績

M31推出5納米先進制程高速接口IP,滿足AI與邊緣運算需求

臺積電日本晶圓廠開幕在即:預計2月24日舉行,量產時間確定

顯微測量的原理及其在先進制造業中的意義

臺積電2023年Q4營收穩健,先進制程營收占比高達67%

芯片先進制程之爭:2nm戰況激烈,1.8/1.4nm苗頭顯露

日本召開的VLSI 2019峰會上公開在先進制程工藝方面的進度

日本召開的VLSI 2019峰會上公開在先進制程工藝方面的進度

評論