來源:內(nèi)容來自由半導(dǎo)體行業(yè)觀察翻譯自「semiwiki」,作者:Tom Dillinger,謝謝。

編者按:每年,臺(tái)積電都會(huì)在全球舉辦兩場(chǎng)大型客戶活動(dòng)——春季臺(tái)積電技術(shù)研討會(huì)和秋季臺(tái)積電開放式創(chuàng)新平臺(tái)生態(tài)系統(tǒng)論壇。技術(shù)研討會(huì)最近在加州圣克拉拉舉行,廣泛介紹先進(jìn)半導(dǎo)體和封裝技術(shù)發(fā)展的最新情況。本文簡要回顧了半導(dǎo)體工藝演示的要點(diǎn),后續(xù)文章將回顧先進(jìn)封裝的內(nèi)容。

臺(tái)積電成立于1987年,自1994年以來一直舉辦年度技術(shù)研討會(huì),今年是臺(tái)積電成立25周年(圣克拉拉會(huì)議中心普遍強(qiáng)調(diào)這一點(diǎn))。臺(tái)積電北美總裁兼首席執(zhí)行官Dave Keller表示:“第一屆硅谷研討會(huì)的與會(huì)者不足100人,而現(xiàn)在,出席人數(shù)已超過2000人。”

供公司發(fā)展總監(jiān)Cheng-Ming Liu博士介紹了臺(tái)積電汽車客戶的獨(dú)特需求,特別是在更長的產(chǎn)品生命周期內(nèi)的持續(xù)供應(yīng)。他表示:

“我們對(duì)“舊”的工藝流程的承諾是堅(jiān)定不移的。我們從未關(guān)閉過一家工廠,也從未關(guān)閉過一項(xiàng)工藝技術(shù)。”

研究與開發(fā)/技術(shù)開發(fā)高級(jí)副總裁Y.-J.Mii博士著重介紹了工藝技術(shù)發(fā)展的三個(gè)時(shí)代,如下圖所示:

在第一階段,Dennard Scaling是指在后續(xù)的工藝節(jié)點(diǎn)中,將FEOL線性光刻尺寸按“s”(s < 1)的比率進(jìn)行微縮,實(shí)現(xiàn)電路密度(1 / s^2)的提高(量度為gates / mm^2),下一階段的重點(diǎn)是材料的改進(jìn),而當(dāng)前階段的重點(diǎn)是設(shè)計(jì)—技術(shù)的協(xié)同優(yōu)化(馬上有更多介紹)。

在隨后的研討會(huì)上,集成互連和封裝研發(fā)副總裁DougYu博士介紹了先進(jìn)封裝技術(shù)如何專注于微縮,盡管持續(xù)時(shí)間較短。 “十多年來,封裝還提供了再分布層(RDL)和凸點(diǎn)間距光刻的二維改進(jìn)。借助我們今天所描述的多芯片、3D垂直堆疊封裝技術(shù)——特別是臺(tái)積電的SoIC產(chǎn)品,我們?cè)陔娐访芏确矫嫒〉昧司薮蟮母纳啤等于零。或者換句話說,我們實(shí)現(xiàn)了無限微縮。(實(shí)際上,很容易預(yù)見到產(chǎn)品技術(shù)將開始使用gates / mm^3進(jìn)行度量。)

臺(tái)積電先進(jìn)工藝技術(shù)現(xiàn)狀的簡要介紹

(一)N7/N7+(7nm/7nm+)

臺(tái)積電在兩年前的研討會(huì)上宣布了N7和N7 +工藝節(jié)點(diǎn)。

N7是“基線”的FinFET工藝,而N7+通過引入EUV光刻技術(shù),為選定的FEOL層提供了更好的電路密度。設(shè)計(jì)IP從N7過渡到N7+需要重新部署,以實(shí)現(xiàn)1.2倍的邏輯門密度提高。主要亮點(diǎn)包括:

N7正在投產(chǎn),2019年預(yù)計(jì)將有100多種新的流片(NTO)。

關(guān)鍵IP介紹:112Gbps PAM4 SerDes。

N7+受益于持續(xù)的EUV輸出功率(~280W)和uptime(~85%)的改善。臺(tái)積電表示:“雖然我們預(yù)計(jì)功率和uptime會(huì)進(jìn)一步改善,但這些措施足以推動(dòng)N7 +容量增長。”

臺(tái)積電專注于減少N7的缺陷密度(D0)。根據(jù)臺(tái)積電的說法,“在初始產(chǎn)量增加后,D0改進(jìn)斜坡的速度比以前的節(jié)點(diǎn)快。”

臺(tái)積電展示了N7芯片尺寸的分裂:移動(dòng)客戶<100 mm^2,HPC客戶>300 mm^2。

據(jù)我所知,臺(tái)積電還首次表示他們正專門為“大型芯片”追蹤D0,并報(bào)告說與其他N7產(chǎn)品相比,大型設(shè)計(jì)相對(duì)減少了學(xué)習(xí)。

N7+將于2009年下半年產(chǎn)量上升,并表現(xiàn)出與N7相當(dāng)?shù)腄0缺陷率。

(二)讓5G成為現(xiàn)實(shí)

臺(tái)積電邀請(qǐng)高通首席技術(shù)官Jim Thompson介紹了他對(duì)N7的看法——這是一次非常有啟發(fā)性的演講:

“N7是5G的推動(dòng)者,如我們最新的SnapDragon855版本所示。”

“具有256個(gè)天線單元的5G MIMO支持64個(gè)同步數(shù)字流(simultaneous digital streams),即16個(gè)用戶每個(gè)用戶在一部電話上接收4個(gè)數(shù)據(jù)流。”

“天線設(shè)計(jì)對(duì)于5G來說確實(shí)非常關(guān)鍵,可以克服路徑損耗和信號(hào)阻塞。人們正在尋求新的、創(chuàng)新的天線實(shí)施方案——?dú)w根結(jié)底,這只是數(shù)學(xué)問題,盡管肯定是復(fù)雜的數(shù)學(xué)問題。”

“對(duì)于5G的采用率,肯定有很多人持懷疑態(tài)度。然而,5G的傳輸速度比4G快得多。在推出計(jì)劃中,只有5家運(yùn)營商和3臺(tái)OEM設(shè)備支持4G,大部分在美國和韓國。目前,有超過20家運(yùn)營商和20多家OEM設(shè)備專注于5G部署,包括歐洲、中國、日本和東南亞。”

“此外,不要忽視5G在消費(fèi)類手機(jī)以外的應(yīng)用中的部署,例如無線工廠自動(dòng)化。與工業(yè)機(jī)器人的通信需要高帶寬、低延遲和極高的可用性。考慮一下5G帶來的在無線環(huán)境下制造靈活性的機(jī)會(huì)。”

(三)N6(6nm)

臺(tái)積電推出了一款新節(jié)點(diǎn)產(chǎn)品,名為N6。此節(jié)點(diǎn)具有一些非常獨(dú)特的特性:

與N7兼容的設(shè)計(jì)規(guī)則(例如,57 mm M1 pitch,與N7相同)

與N7兼容的IP模型

為有限的FEOL層提供EUV光刻,“比N7+多1個(gè)EUV層,充分利用了N7+和N5的學(xué)習(xí)經(jīng)驗(yàn)”

更嚴(yán)格的工藝控制,比N7更快的cycle time

同樣的EDA參考流程、填充算法等,與N7相同

N7設(shè)計(jì)可以簡單地“重新流片”(re-tapeout,RTO)到N6,以提高EUV掩模光刻的產(chǎn)量

或者,N7設(shè)計(jì)可以通過使用N6標(biāo)準(zhǔn)單元庫(H240)重新部署邏輯塊來提交新的流片(NTO),該庫利用單元之間的“公共PODE”(CPODE)設(shè)備將邏輯塊密度提高~18%。

2020年第一季度開始風(fēng)險(xiǎn)生產(chǎn)(圖示為13級(jí)金屬互連堆棧)

盡管設(shè)計(jì)規(guī)則與N7兼容,但N6還引入了一個(gè)非常獨(dú)特的功能“M0路由”。

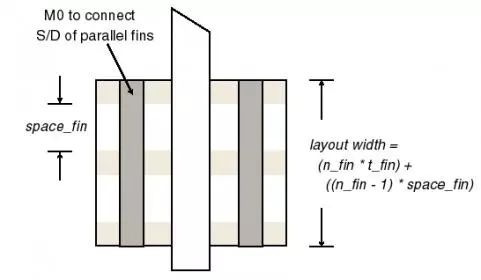

下圖說明了“典型”FinFET器件layout,其中M0僅用作局部互連,用于連接multi-fin器件的源極或漏極節(jié)點(diǎn),并在單元內(nèi)用于連接通用nFET和pFET原理圖節(jié)點(diǎn)。

我需要更多地思考使用M0作為路由層的機(jī)會(huì),臺(tái)積電表示EDA路由器對(duì)此功能的支持仍然是合格的。

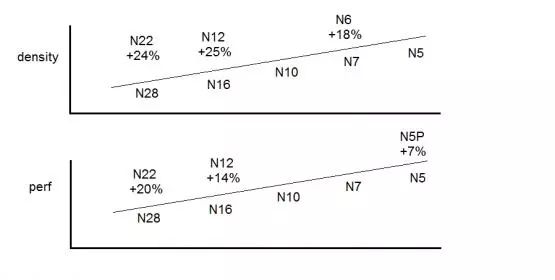

在我看來,N6是臺(tái)積電引入“半節(jié)點(diǎn)”流程路線圖的延續(xù),如下圖所示。

半節(jié)點(diǎn)工藝既是工程驅(qū)動(dòng)的決策,也是業(yè)務(wù)驅(qū)動(dòng)的決策,目的是提供低風(fēng)險(xiǎn)的設(shè)計(jì)遷移路徑,為現(xiàn)有N7設(shè)計(jì)提供一個(gè)降低成本的選項(xiàng),作為一個(gè)“mid-life kicker”。

N6的引入也凸顯了一個(gè)問題,這個(gè)問題將變得越來越棘手。集成外部IP的設(shè)計(jì)的遷移取決于IP提供商的工程和財(cái)政資源,以便按照適當(dāng)?shù)臅r(shí)間表在新節(jié)點(diǎn)上開發(fā)、發(fā)布(在測(cè)試站點(diǎn)上)、表征IP并對(duì)其進(jìn)行鑒定。N6提供了在不受外部IP釋放約束的情況下引入kicker的機(jī)會(huì)。

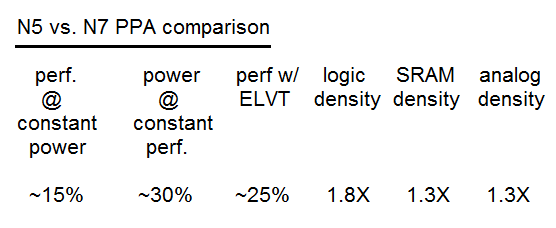

(四)N5(5nm)

工藝節(jié)點(diǎn)N5合并了額外的EUV光刻,以減少需要大量多重曝光處理的圖層的掩模數(shù)。

風(fēng)險(xiǎn)生產(chǎn)于19年3月開始,高產(chǎn)量增長將在2020年第二季度臺(tái)南Gigafab 18完成(19年3月完成的第1階段設(shè)備安裝)

旨在同時(shí)支持移動(dòng)和高性能計(jì)算“平臺(tái)”客戶;高性能應(yīng)用程序?qū)⑾M褂眯碌摹俺蚔t”(ELVT)器件

1.5V或1.2V I / O器件支持

計(jì)劃提供N5P(“PLUS”)產(chǎn)品,在恒定功率下可提高+7%的性能,或在恒定perf 下比N5降低約15%的功率(N5后一年)

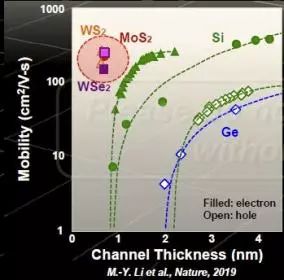

N5將使用高移動(dòng)性(Ge)器件溝道

先進(jìn)材料工程

除了N5推出高移動(dòng)性溝道外,臺(tái)積電還強(qiáng)調(diào)了其他材料和器件工程更新:

超高密度MIM產(chǎn)品(N5),具有2X ff/um*2和2X插入密度

新型低K介電材料

金屬反應(yīng)離子蝕刻(RIE),取代 Cu damascene,實(shí)現(xiàn)金屬間距<30um

石墨烯“cap”,降低Cu互連電阻率

改進(jìn)的局部MIM電容將有助于解決由于較高的柵極密度而增加的電流。臺(tái)積電指出,高性能(高開關(guān)活動(dòng))設(shè)計(jì)可實(shí)現(xiàn)預(yù)期的個(gè)位數(shù)性能提升。

節(jié)點(diǎn)16FFC和12FFC都得到了器件工程改進(jìn):

16FFC+ :與16FFC相比,+10% perf @恒功率,+20%POWER@恒定perf

12FFC+ :與12FFC相比,+7% perf @恒功率,+15% POWER@恒定 perf

這些節(jié)點(diǎn)的NTO將在2019年第三季度被接受。

臺(tái)積電還簡要介紹了正在進(jìn)行的未來節(jié)點(diǎn)材料研究的研發(fā)活動(dòng), 例如,Ge nanowire/nanoslab器件溝道,2D半導(dǎo)體材料(ZrSe2,MoSe2),請(qǐng)見下圖(來源:臺(tái)積電)。

Fab運(yùn)營高級(jí)副總裁j.k Wang博士詳細(xì)討論了正在進(jìn)行的降低DPPM和保持“卓越制造”的努力。特別值得注意的是為滿足汽車客戶苛刻的可靠性要求而采取的步驟。Wang博士演講的重點(diǎn)包括:

“自引入N16節(jié)點(diǎn)以來,我們?cè)陬^6個(gè)月加快了每個(gè)節(jié)點(diǎn)的產(chǎn)能提升速度。2019年N7的產(chǎn)能將超過每年100萬塊12英寸晶圓。自2017年以來,隨著Gigafab 15的第5至7階段已經(jīng)投產(chǎn),N10/N7產(chǎn)能增長了兩倍。”

“我們實(shí)施了積極的統(tǒng)計(jì)過程控制(在控制晶圓現(xiàn)場(chǎng)進(jìn)行測(cè)量),以便及早發(fā)現(xiàn)、停止和修復(fù)過程的變化,例如基線測(cè)量的向上/向下偏移、方差偏移、工具之間的不匹配。我們建立了二維晶圓剖面測(cè)量標(biāo)準(zhǔn),并對(duì)每個(gè)晶圓的‘驗(yàn)收’剖面進(jìn)行在線監(jiān)測(cè)和比較。”

“N7的DDM降低率是所有節(jié)點(diǎn)中最快的。”

“對(duì)于汽車客戶,我們實(shí)施了獨(dú)特的措施,以實(shí)現(xiàn)苛刻的DPPM要求。我們會(huì)把壞區(qū)域中的好芯片標(biāo)記出來。而且邊際批次會(huì)有SPC標(biāo)準(zhǔn),它們會(huì)被廢棄。”

“我們將支持特定于產(chǎn)品的規(guī)格上限和下限標(biāo)準(zhǔn)。我們將報(bào)廢超出規(guī)格限制的晶圓,或保留整批晶圓進(jìn)行客戶的風(fēng)險(xiǎn)評(píng)估。”(見下圖。資料來源:臺(tái)積電)

臺(tái)積電的不同技術(shù)平臺(tái)

臺(tái)積電開發(fā)了一種針對(duì)流程開發(fā)和設(shè)計(jì)支持功能的方法,主要關(guān)注四個(gè)平臺(tái)——移動(dòng)、HPC、物聯(lián)網(wǎng)和汽車。汽車事業(yè)部總監(jiān)Cheng-Min Lin博士介紹了該平臺(tái)的最新情況,以及汽車客戶的獨(dú)特特點(diǎn)。

(一)汽車平臺(tái)

Lin博士指出:“汽車系統(tǒng)既需要先進(jìn)的ADAS邏輯技術(shù),如N16FFC,也需要先進(jìn)的V2X通信射頻技術(shù)。盡管從現(xiàn)在到2022年,汽車的復(fù)合年均增長率預(yù)計(jì)僅為1.8%,但半導(dǎo)體內(nèi)容的復(fù)合年均增長率將為6.9%。

他繼續(xù)說:“L1/L2功能的使用率將達(dá)到30%左右,額外的MCU應(yīng)用于安全、連接,以及電動(dòng)/混合電動(dòng)汽車功能。每輛車大約有30-40個(gè)單片機(jī)。”(在他的圖表中,預(yù)測(cè)L3/L4/L5的使用率在2020年約為0.3%,2025年為2.5%。)

“數(shù)字儀表板駕駛艙可視化系統(tǒng)的采用率也將提高,進(jìn)一步推動(dòng)半導(dǎo)體增長,2018年為0.2%,2025年達(dá)到11%。”

L2+

SAE International將自動(dòng)駕駛輔助和最終自動(dòng)駕駛的支持水平定義為“1級(jí)至5級(jí)”。也許是因?yàn)檎J(rèn)識(shí)到實(shí)現(xiàn)L3到L5的困難,因此提出了一個(gè)新的“L2+”級(jí)別(盡管在SAE之外),帶有附加的攝像機(jī)和決策支持功能。

“L2+型汽車通常會(huì)集成6個(gè)攝像頭、4個(gè)短程雷達(dá)系統(tǒng)和1個(gè)遠(yuǎn)程雷達(dá)單元,需要超過50GFLOPS圖形處理和>10K DMIPS導(dǎo)航處理吞吐量。”

N16FFC,然后是N7

16FFC平臺(tái)已通過汽車環(huán)境應(yīng)用認(rèn)證,例如SPICE和老化模型,基礎(chǔ)IP特性,非易失性存儲(chǔ)器,接口IP。N7平臺(tái)將于2020年通過(AEC-Q100和ASIL-B)認(rèn)證。Lin博士表示:“汽車客戶往往落后消費(fèi)者采用約2~3年來利用DPPM學(xué)習(xí),盡管這一間隔正在縮短。我們預(yù)計(jì)N7汽車將在2021年被廣泛采用。”

“臺(tái)積電射頻CMOS產(chǎn)品將用于SRR、LRR和LIDAR。16FFC-RF增強(qiáng)型工藝將在2020年2季度符合合汽車平臺(tái)的要求。”

(二)物聯(lián)網(wǎng)平臺(tái)

臺(tái)積電物聯(lián)網(wǎng)平臺(tái)專注于低成本,低(有源)功耗和低泄漏(待機(jī))功耗。物聯(lián)網(wǎng)業(yè)務(wù)開發(fā)總監(jiān)Simon Wang博士提供了以下最新信息:

工藝流程路線圖

55ULP, 40ULP (w/RRAM): 0.75V/0.7V

22ULP, 22ULL: 0.6V

12FFC+_ULL: 0.5V (目標(biāo))

為22ULL節(jié)點(diǎn)引入新器件:EHVT器件,超低泄漏SRAM

22ULL SRAM是一種“雙VDD rail”設(shè)計(jì),具有獨(dú)立的邏輯(0.6V,SVT+HVT)和bitcell VDD_min(0.8V)值,可實(shí)現(xiàn)最佳待機(jī)功耗。

22ULL節(jié)點(diǎn)還獲得非易失性存儲(chǔ)器的MRAM選項(xiàng)。

請(qǐng)注意,一種新的方法將被應(yīng)用于低VDD設(shè)計(jì)的靜態(tài)時(shí)序分析。基于階段的OCV(降階乘法器,derating multiplier)單元延遲計(jì)算將使用自由變異格式(LVF)過渡到sign-off。

下一代物聯(lián)網(wǎng)節(jié)點(diǎn)將是12FFC+_ULL,風(fēng)險(xiǎn)生產(chǎn)將在2020年第二季度開始。(具有SVT低VDD標(biāo)準(zhǔn)單元, 0.5V VDD)

(三)射頻

臺(tái)積電強(qiáng)調(diào)了RF技術(shù)的過程開發(fā)重點(diǎn),作為5G和汽車應(yīng)用增長的一部分。RF和模擬業(yè)務(wù)開發(fā)總監(jiān)Jay Sun博士重點(diǎn)介紹了以下要點(diǎn):

對(duì)于RF系統(tǒng)收發(fā)器,22ULP / ULL-RF是主流節(jié)點(diǎn)。對(duì)于更高端的應(yīng)用,16FFC-RF是合適的,其次是2020年下半年的N7-RF。

重要的器件研發(fā)正在研發(fā),以增強(qiáng)這些節(jié)點(diǎn)的器件ft和fmax,期待2020年的16FFC-RF-Enhanced(fmax> 380GHz)和2021年的N7-RF-Enhanced。

新的頂級(jí)BEOL堆疊選項(xiàng)可用于“升高”的超厚金屬,用于電感器,使之具有更高的Q值。

對(duì)于低于6GHz的RF前端設(shè)計(jì),臺(tái)積電將于2019年推出N40SOI——從0.18微米SOI過渡到0.13微米SOI,再過渡到N40SOI,以此提供ft和fmax大幅改進(jìn)的器件。

先進(jìn)封裝方面的表現(xiàn)

從研討會(huì)我們可以看得出,臺(tái)積電顯然已從一家“純”晶圓級(jí)代工廠轉(zhuǎn)型為復(fù)雜集成系統(tǒng)模塊的供應(yīng)商——或者根據(jù)臺(tái)積電CEO C.C.Wei的說法,臺(tái)積電是“大規(guī)模納米生產(chǎn)創(chuàng)新”的領(lǐng)先供應(yīng)商。這是多年研發(fā)投資的成果,例如,請(qǐng)參閱下文“SoIC”部分中關(guān)于3D堆疊的討論。

集成互連和封裝研發(fā)副總裁Doug Yu博士提供了詳細(xì)的最新信息。Yu博士將封裝技術(shù)分為獨(dú)特的類別——“前端”3D芯片集成(SoIC)和“后端”封裝進(jìn)展(CoWoS, InFO)。此外,他還介紹了焊盤間距和 Cu pillar/ SnAg凸點(diǎn)光刻技術(shù)的進(jìn)展,特別提到了汽車級(jí)可靠性要求。

(1)凸點(diǎn)(Bumping)技術(shù)

臺(tái)積電繼續(xù)推進(jìn)凸點(diǎn)技術(shù),可實(shí)現(xiàn)60-80um的凸點(diǎn)間距(適用于較小的芯片)。

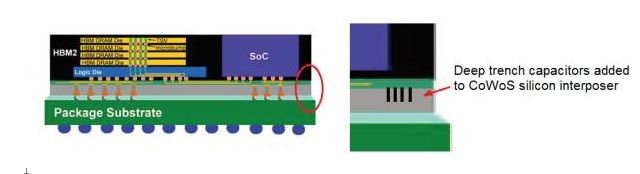

(2)CoWos

臺(tái)積電最初的2.5D封裝產(chǎn)品是chip-on-wafer-on-substrate(CoWoS),它通過使內(nèi)存“更接近處理器”,實(shí)現(xiàn)了非常高性能的系統(tǒng)集成。

?> 50種客戶產(chǎn)品

?臺(tái)積電正在開發(fā)“標(biāo)準(zhǔn)化”配置,例如,從具有2個(gè)或4個(gè)HBM的1個(gè)SoC,演變?yōu)榫哂?個(gè)HBM2E的2個(gè)以上SoC(96GB @ 2.5TB /秒)

相應(yīng)地,臺(tái)積電將把最大2.5D中介層占用空間從1X光罩(~50x50)擴(kuò)展到3X(~85x85),具有150um的凸點(diǎn)間距。

?硅中介層支持5個(gè)金屬層和(新)深溝道電容——請(qǐng)參見下圖。

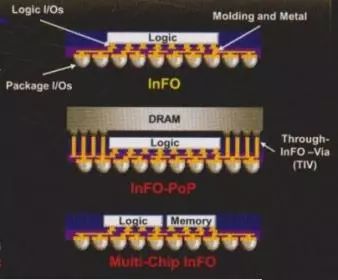

(3)InFo

臺(tái)積電繼續(xù)發(fā)展集成FanOut(InFO)封裝產(chǎn)品。回想一下,InFO是使用“重組晶圓”成型化合物集成(多個(gè))芯片的手段,以提供用于RDL圖案化的封裝襯底。InFO以傳統(tǒng)的小封裝WLCSP技術(shù)為基礎(chǔ),以實(shí)現(xiàn)(大面積)重分布互連和高凸點(diǎn)數(shù)——請(qǐng)參見下圖。

InFO-PoP支持在基極頂部堆疊邏輯芯片和DRAM芯片,使用through-InFO-vias(TIV)將DRAM連接到金屬層。InFO-PoP開發(fā)的重點(diǎn)是改善TIV的間距和縱橫比(垂直面與直徑)。

InFO-on-Substrate產(chǎn)品將(多芯片)InFO模塊連接到(大面積)基板,充分利用為CoWoS開發(fā)的多光罩綁結(jié)技術(shù)(multiple reticle stitching technology)。

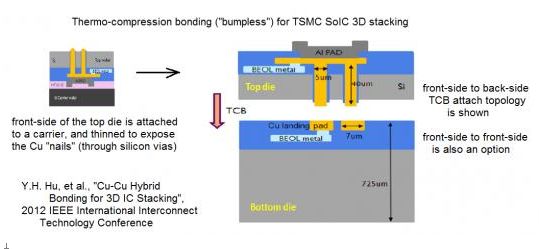

(4)SoIC(“前端”3D集成)

研討會(huì)關(guān)于封裝的重要公告是介紹了“前端”3D芯片堆疊拓?fù)洌Q為SoIC(System-on-Integrated Chips集成系統(tǒng)芯片)。

SoIC是一種多芯片之間的“無凸點(diǎn)”互連方法。如下圖所示(來自臺(tái)積電早期的一篇研發(fā)論文),來自基模的Cu焊盤和來自(變薄的)頂部芯片的裸露的Cu“nails”利用熱壓結(jié)合來提供電氣連接。(在 die-to-die接口也存在合適的底部填充材料。)

?芯片中的硅通孔提供連接,間距非常緊湊。

?支持face-to-face和face-to-back芯片連接。 “已知良好”的堆疊芯片可以是不同的尺寸,在堆疊層上具有多個(gè)芯片。

?臺(tái)積電展示了一個(gè)3高垂直SoIC 堆疊(3-high vertical SoIC stack)實(shí)體模型。

?EDA支持可用:物理設(shè)計(jì)(DRC、網(wǎng)絡(luò)列表/LVS)、寄生提取、時(shí)序、IR/EM分析、信號(hào)完整性/功率完整性分析、熱/材料應(yīng)力分析。

?SOIC封裝產(chǎn)品的資格目標(biāo)是2019年。(我從單獨(dú)的臺(tái)積電公告中了解到,SoIC的將在2021年量產(chǎn)。)

總結(jié)

幾年前,有人半猜測(cè)半開玩笑說,“只有7個(gè)客戶能負(fù)擔(dān)得起7nm設(shè)計(jì),只有5個(gè)客戶能負(fù)擔(dān)得起5nm”。

顯然,N7/N6和N5在移動(dòng)通信、HPC和汽車(L1-L5)應(yīng)用中的發(fā)展勢(shì)頭打消了這種想法。臺(tái)積電正通過DTCO大力投資這些節(jié)點(diǎn),充分利用EUV光刻領(lǐng)域的重大進(jìn)展和新材料的引入。

另外,我們也看到,除了傳統(tǒng)的晶圓代工以外,臺(tái)積電的2.5D和InFO“后端”封裝產(chǎn)品都在不斷發(fā)展,重點(diǎn)是推出SoIC拓?fù)浣Y(jié)構(gòu)的緊密間距Cu壓接全3D堆疊芯片。可用的電路密度(mm ^3)將非常吸引人。然而,利用這項(xiàng)技術(shù)的挑戰(zhàn)相當(dāng)大,從系統(tǒng)架構(gòu)分區(qū)到堆疊芯片接口的復(fù)雜電氣/熱/機(jī)械分析,全都包括在內(nèi)。

摩爾定律絕對(duì)具有活力,盡管需要戴上3D眼鏡才能看到。

-

芯片

+關(guān)注

關(guān)注

454文章

50460瀏覽量

421980 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27063瀏覽量

216504 -

機(jī)械

+關(guān)注

關(guān)注

8文章

1538瀏覽量

40472

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

日本羅姆半導(dǎo)體加強(qiáng)與臺(tái)積電氮化鎵合作,代工趨勢(shì)顯現(xiàn)

臺(tái)積電CoWoS產(chǎn)能將提升4倍

萬年芯解讀臺(tái)積電與ASML報(bào)告,中國大陸半導(dǎo)體需求強(qiáng)勁

臺(tái)積電布局FOPLP技術(shù),推動(dòng)芯片封裝新變革

臺(tái)積電SoIC技術(shù)助力蘋果M5芯片,預(yù)計(jì)2025年量產(chǎn)

臺(tái)積電股價(jià)大增,為全球半導(dǎo)體行業(yè)未來發(fā)展注入活力

三星加強(qiáng)半導(dǎo)體封裝技術(shù)聯(lián)盟,以縮小與臺(tái)積電差距

愛芯元智攜智駕芯片產(chǎn)品及解決方案亮相臺(tái)積電創(chuàng)新企業(yè)展

臺(tái)積電熊本三廠啟動(dòng)籌建,將打造半導(dǎo)體創(chuàng)新聚落

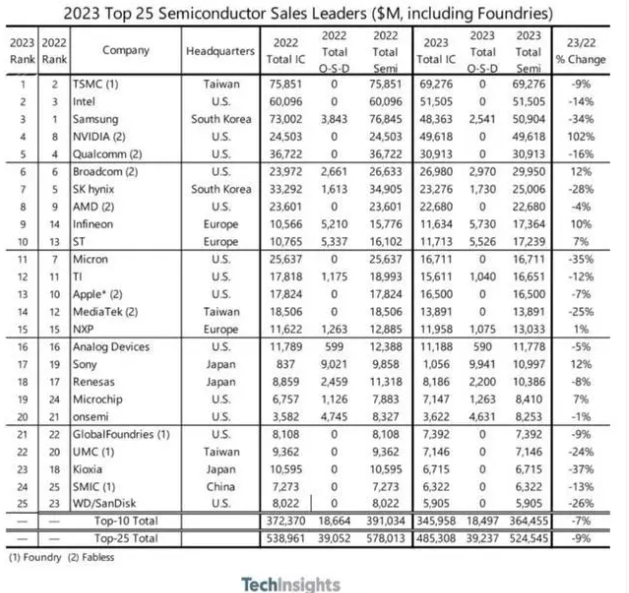

全球Top25半導(dǎo)體公司發(fā)布:臺(tái)積電領(lǐng)跑,英偉達(dá)異軍突起

關(guān)于臺(tái)積電半導(dǎo)體技術(shù)分享

關(guān)于臺(tái)積電半導(dǎo)體技術(shù)分享

評(píng)論