負偏壓溫度不穩定性[NBTI]是不希望的老化效應。每當PMOS晶體管被負偏置時,它表現為 V th 的幅度的增加。它主要在65nm以下的技術上展出。在亞20nm節點處,效應變得更加突出。

在PMOS晶體管的負偏壓下,這是PMOS的正常操作,發生Si-H鍵的解離。這種鍵的解離在高溫和施加的負偏壓的持續時間內加速。這種Si-H鍵的解離產生界面陷阱。這種接口陷阱的產生增加了PMOS的閾值電壓。閾值電壓的增加表現為PMOS開關周期的增加。

當PMOS用于AC模式(動態開啟和關閉)時,在應力狀態(PMOS ON狀態)期間產生的接口陷阱由于退火影響而減少。因此,與PMOS的靜態應力操作相比,PMOS的動態操作在 V th 中經歷相對較少的退化。在今天的時代,我們有數字電路,其中電路中的一些PMOS可能在一定時間開啟而其他PMOS關閉。因此,在整個芯片中發生不對稱NBTI退化,這可能導致各種塊中的定時故障。今天,由于缺乏有效的NBTI測量模型,設計工程師將NBTI邊緣作為基于經驗數據的軟糖因子。因此,他們最終可能會增加比實際NBTI要求更多的悲觀情緒。

NBTI對逆變器的影響

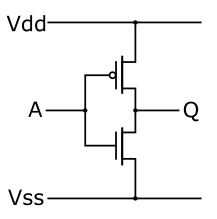

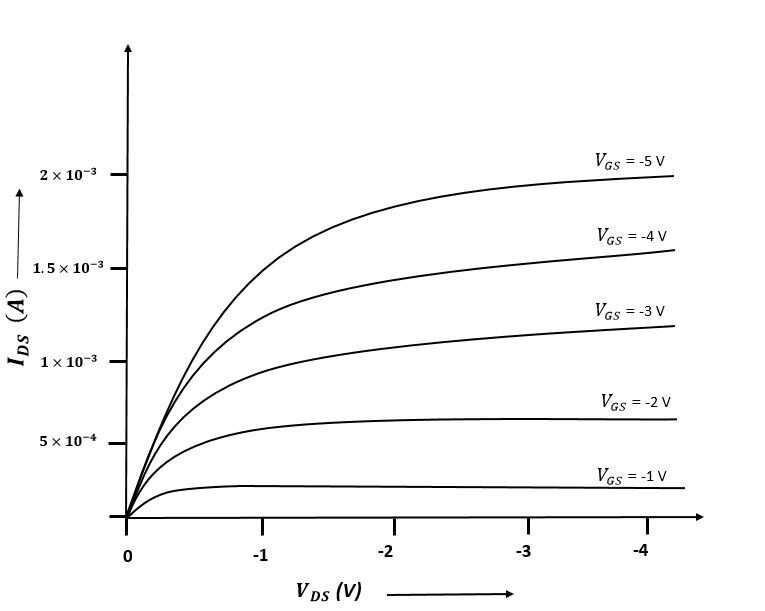

在這一部分中,我們將分析NBTI如何通過使用導致電路明顯延遲最簡單的開關CMOS電路,即逆變器。圖1顯示了CMOS反相器,圖2顯示了其PMOS特性。

圖1. CMOS逆變器

圖2. PMOS特性

輸出電流可通過以下2個方程式計算得出。等式1對于線性區域有效( V DS GS - V tp )和公式2對飽和度有效( V DS > V GS - V tp )。

其中 I D 是漏極電流,μ是空穴遷移率, ε ox 是介電常數, T ox 是氧化物厚度。 W 和 L 是晶體管的有效柵極寬度和長度。 V tp 是pmos的閾值電壓,并且 V GS & V DS 分別是柵極 - 源極和漏極 - 源極之間的電壓。

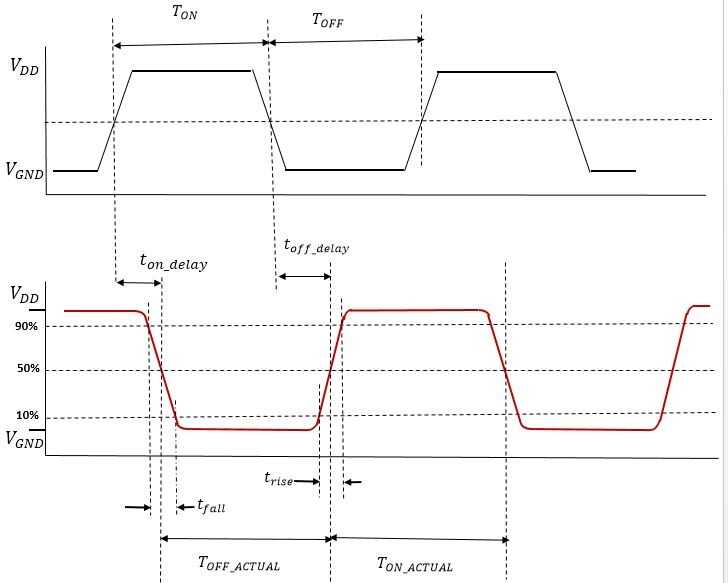

圖3.逆變器的輸入輸出波形

圖3顯示了逆變器的輸入及其輸出。在PMOS中,閾值電壓的改變將影響漏極電流。因為,在NBTI的情況下,閾值電壓變得更負,即,其絕對值增加,因此漏極電流減小,這將導致上升時間和下降時間的增加,這又將增加開啟延遲。 。當這樣的緩沖器/逆變器放置在數據路徑中時,NBTI通過增加額外的延遲來影響數據的到達,從而產生可能破壞我們設計的潛在設置故障。

分析

各種研究表明,FinFET中的NBTI會導致閾值電壓偏移50至100毫伏,具體取決于芯片的工作條件和工作壽命。圖4顯示了模擬設置。動機是計算NBTI對整體延遲的影響。我們將數據路徑命名為P1。它是從啟動觸發器的輸出(Q)到捕獲觸發器的數據輸入(D)的典型數據路徑。該路徑包括逆變器和緩沖器的組合。該路徑在相同定時路徑中的不同門之間展現出各種抵消效果,從而與路徑的預期延遲相比減小了總延遲。在邏輯深度較大的數據路徑中,此效果變得更為顯著。

圖4.模擬設置

下圖顯示了NBTI在16nm處引起的延遲變化以及Vdd對延遲的影響。我們在3個典型電源電壓(Vdd)下完成了模擬。 0.72V,0.8V和0.88V。這些電源電壓值通常用于這種低技術節點。

圖5顯示了帶電源(x軸)的逆變器新鮮和老化樣品的延遲變化(y軸)。從上述方程式來看,電源的影響是顯而易見的,電壓的增加會增加漏極電流,從而減少延遲。圖6顯示了緩沖區的類似行為。在這些數字中可以清楚地看到延遲的增加。

圖5.逆變器的延遲變化

圖6.緩沖區的延遲變化

圖7.數據路徑延遲

圖7顯示了數據的延遲變化路徑P1。 NBTI模擬的數據顯示在0.72V下的最大降級。如前所述,0.72電壓也表征比其他比較電壓更多的延遲,這種電路中的NBTI可能構成嚴重威脅。在我們的模擬中,由于NBTI導致的延遲增加在路徑P1中幾乎為11ps。

以下等式顯示了設置裕度和時鐘偏差對因老化而可能發生變化的各種因素的依賴性:

設置余量=時鐘周期 - 數據路徑延遲 - 時鐘偏移 - 設置時間

時鐘偏移=啟動路徑延遲 - 捕獲路徑延遲

如果啟動路徑的緩沖區多于捕獲路徑,則時間偏差將因NBTI而增加,并且設置余量將減小。由于NBTI,數據路徑也會提供更多延遲,這將進一步降低設置余量并可能導致設置違規。同樣,如果捕獲路徑具有更多緩沖區,則可能導致保持違規。這就是為什么必須在設計階段包括老化的影響,否則它會在使用幾年后導致芯片故障,這在汽車等應用中可能是災難性的。

減少NBTI影響的措施

時鐘門控檢查:時鐘門控后的路徑應盡可能小。如果大部分路徑相同,則兩條路徑的老化影響幾乎相似,對時鐘偏差的總影響將非常小。

增加邊距:設計師應該采取額外保持和設置邊距,具體取決于老化影響。應避免過度優化,因為它會降低工作頻率。

自適應體偏置:由于NBTI的主要影響是增加PMOS晶體管的閾值電壓幅度,因此正向偏置源體結可以補償變化。使用正向體偏置進行老化所涉及的折衷是未老化的PMOS晶體管的閾值電壓幅度減小,因為這會導致泄漏功率增加。

結論

在高功能頻率下,NBTI在數據路徑和時鐘路徑中引起的延遲會產生建立和保持違規。這種電路很可能在高應力老化操作期間或未來5到10年內失效。在汽車和醫療應用中,零DPM正在成為一項要求而不僅僅是一項成就,在計算時鐘路徑和數據路徑延遲時,計算NBTI的緊密匹配不確定性已變得絕對必要。這些計算有助于實現最大可能的工作頻率,而不會有任何失敗的風險。

-

電源電路

+關注

關注

48文章

990瀏覽量

65148 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21659 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27727 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42990

發布評論請先 登錄

相關推薦

請問零偏穩定性(bias stability)與零偏不穩定性(bias instability)指的是同一個指標嗎?

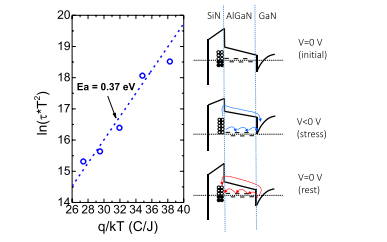

用直接隧道柵電流在線表征PMOSFET負偏壓溫度不穩定性

能量原理及其應用--理想磁流體(IMHD)不穩定性

不穩定性和燒錄不良率很高的改善方法

Gan-ON-SI中負偏壓引起的閾值電壓不穩定性的論文免費下載

機器視覺檢測系統的不穩定性因素有哪些

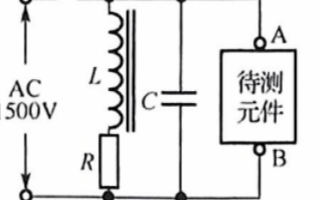

網絡變壓器耐壓檢測時的不穩定性現象

負偏壓溫度不穩定性對電路的影響

負偏壓溫度不穩定性對電路的影響

評論