數據中心設備制造商長期以來一直熱衷于利用FPGA可能實現的大規模并行性,以在高效的功率預算內實現與需求保持同步所需的處理性能和I/O帶寬。然而,傳統上,在FPGA中實現硬件計算平臺一直是一項復雜的挑戰,需要設計人員處理一些最低級別的硬件實現。

盡管一些最新的FPGA設計方法結合了高級綜合(HLS)工具和軟件編程語言(如OpenCL,C和C ++)簡化了任務,并沒有消除對專業FPGA設計專業知識的需求。需要一種高級工作流程,允許軟件工程師將FPGA用作軟件定義的計算平臺,而無需硬件設計的痛苦。為滿足這一需求,此類工作流應該能夠:

從純軟件代碼創建功能硬件

合并現有硬件IP塊,如果

支持使用商用,現成的電路板和自定義平臺

通過構造確保生成的硬件正確,從而消除硬件調試

僅支持使用標準軟件調試工具調試功能塊

考慮一個包含兩個基本功能的軟件算法:將數據處理成一個函數,然后發送到另一個函數進行進一步處理。從軟件的角度來看,這個實現就像調用Function1(),然后單獨調用Function2()一樣簡單,使用指向要處理的數據位置的指針。

圖1對數據執行的功能

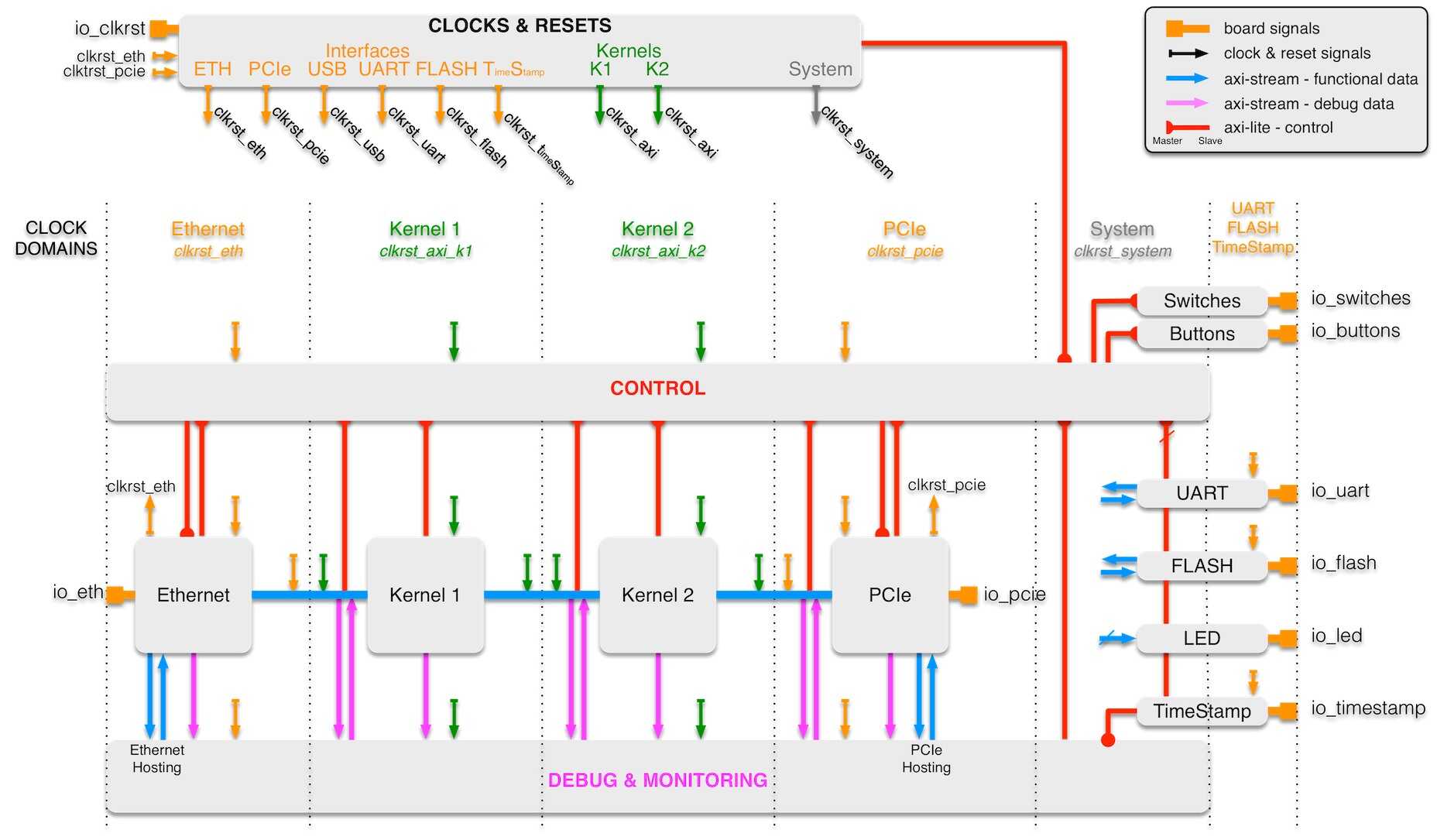

實施此類在沒有正確的硬件抽象工具流程的基于FPGA的硬件平臺上的算法將要求軟件開發人員提出類似于圖2中的硬件設計(其中內核1和內核2各自相應)功能1和功能2的硬件實現。

圖2使用雙功能算法的詳細硬件實現傳統的FPGA工具

硬件設計需要包括控制平面和數據平面。控制平面是執行引擎,它生成時鐘和重置,管理系統啟動,編排數據平面操作,并執行所有內務處理功能。數據平面實例化并連接處理元素,內核1和內核2,以及讀取數據和寫入處理數據所需的必要I/O接口。在圖2中所示的示例中,這些接口是以太網和PCI Express(PCIe)。

熟悉的挑戰

沒有特定硬件專業知識的軟件開發人員可以使用高級綜合工具(如 Vivado HLS )生成內核1和內核2,以編譯軟件函數Function1()和Function2( )用C或C ++編寫的VHDL或Verilog的FPGA硬件描述。但是,使用HLS工具無法生成設計的非算法元素,如接口,控制,時鐘和復位。需要硬件設計人員將其創建為自定義IP。獲取這些元素并連接它們的工作帶來了另一個挑戰,因為某些元素可能不容易獲得,或者可能具有不同類型或大小的接口以及不同的時鐘要求,特定的啟動順序等等。

實施設計同樣面臨嚴峻挑戰。這些包括將設計映射到所選FPGA平臺的資源,生成適當的約束,并確認在FPGA硬件上進行邏輯綜合和實現后滿足這些約束。即使是經驗豐富的硬件設計人員也可能需要數周才能在新的FPGA硬件上實現最簡單的設計。

新方法

PLDA集團是嵌入式電子系統和IP的開發商,它創建了QuickPlay,允許軟件開發人員完成這些任務,從而在FPGA硬件上部分或全部實現CPU的應用程序。在這種以軟件為中心的方法中,設計人員首先開發硬件引擎的C/C ++功能模型,然后使用標準C/C ++調試工具驗證功能模型。然后指定目標FPGA平臺和I/O接口(PCIe,以太網,DDR,QDR等),最后編譯和構建硬件引擎。

為了使這個過程無縫工作,必須保證生成的硬件引擎與原始軟件模型的功能相同。這意味著模型必須是確定性的,因此它將產生與硬件相同的結果,無論硬件實現運行得多快。不幸的是,大多數并行系統遭受不確定性執行。例如,多線程軟件執行取決于CPU,OS,以及在同一主機上運行的非相關進程。多次運行相同的多線程程序可能會有不同的行為。

硬件中的這種非確定性需要在電子波形級別調試硬件引擎本身。這將破壞針對軟件開發人員的工具的目的,但QuickPlay的數據流模型保證了確定性執行,而不管執行引擎如何。該模型由并發功能組成,稱為內核,與流通道通信,這與軟件開發人員如何在白板上繪制應用程序相關聯。任何內核的內容都可以是任意的C/C ++代碼,第三方IP,甚至是HDL代碼。

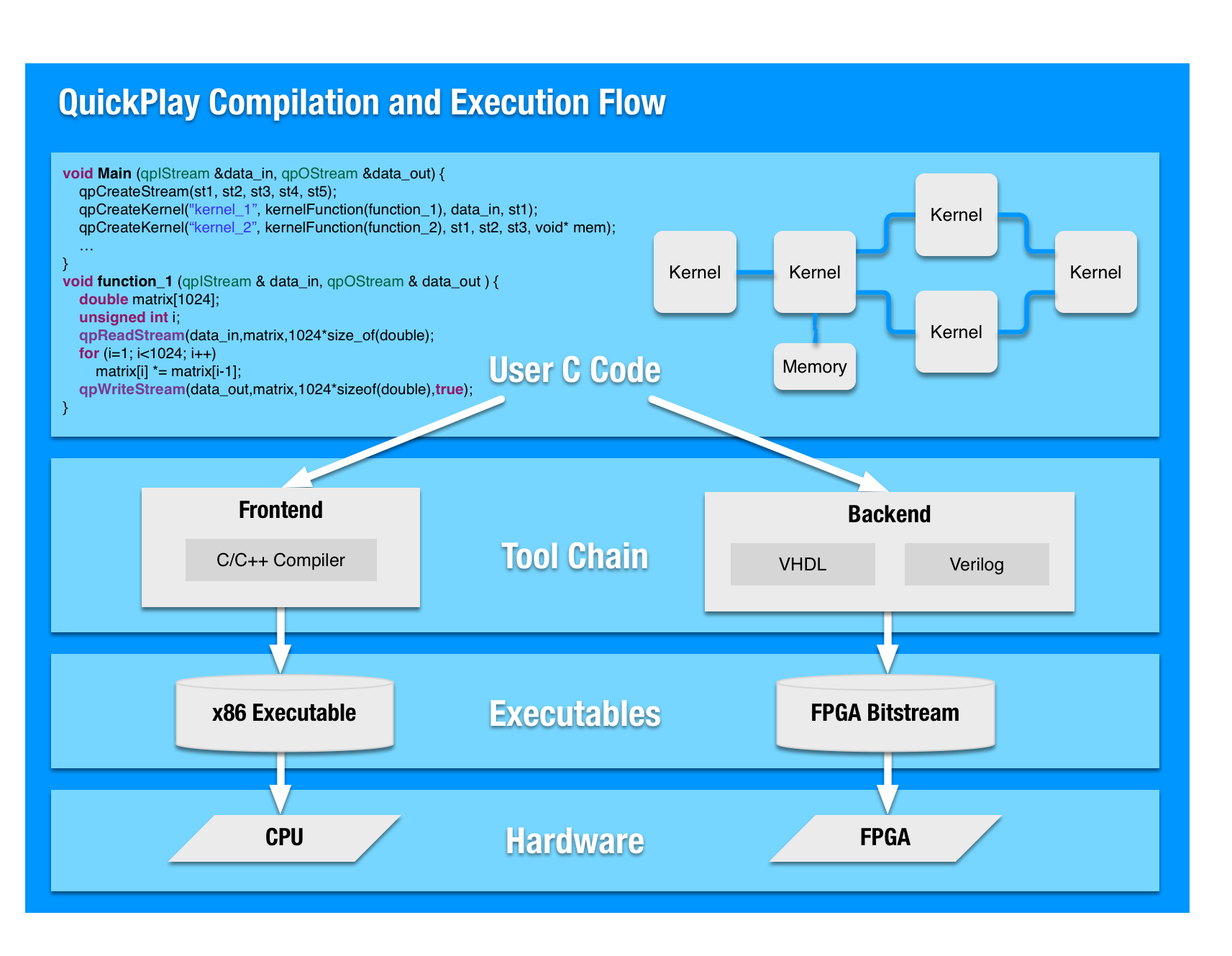

QuickPlay設計流程非常簡單,如圖3所示。

圖3QuickPlay編譯和執行流程

仔細研究設計流程

第1階段:純軟件設計。 FPGA設計是通過在C中添加和連接內核,并使用開發軟件指定通信通道來創建的。 QuickPlay IDE提供了一個C/C ++庫和API來創建內核,流,流端口和內存端口,以及讀取和寫入流端口和內存端口。

第2階段:功能驗證確保軟件模型正常工作。該模型在桌面上編譯并使用測試程序執行,該測試程序將數據發送到輸入,從而驗證輸出的正確性。

階段3:然后從軟件模型生成FPGA硬件。在此階段,使用簡單的下拉菜單選擇目標FPGA平臺和映射到設計輸入和輸出端口的物理接口。

階段4:系統執行類似于功能驗證,除了FPGA設計在選定的FPGA板上運行,而主機應用程序仍在軟件中運行。實際數據可以流入和流出FPGA板。在此階段可以運行比在功能驗證期間更多的測試。

階段5:系統調試。即使在硬件中執行功能后發現錯誤,也無需在硬件級別進行調試,因為QuickPlay可確保軟件模型與硬件實現之間的功能等效。軟件版本中也存在硬件版本中的任何錯誤。

階段6 :(可選)優化。雖然QuickPlay構建的整個基礎架構在性能和利用率方面都非常高效,但設計的整體質量將取決于用戶創建的內核的質量。由于通用C代碼不會產生最有效的硬件實現,因此軟件開發人員可以遵循一些技術和指南來大大提高HLS生成代碼的效率。進一步優化也可以通過使用Vivado HLS或在HDL中重新編碼某些內核來完成。

摘要

這種簡單的方法為大量軟件工程師開放了基于FPGA的計算,他們現在可以使用熟悉的技術在軟件中進行建模,然后構建系統和硬件測試。目前還沒有其他工具采用這種方法,也沒有提供軟件工程師可以在源級別專門設計和調試的框架。

生成的硬件效率也使QuickPlay成為硬件工程師尋找的好工具通過讓QuickPlay處理平凡的硬件設計任務來節省數周或數月的設計工作,同時他們專注于真正的增值:處理內核。

QuickPlay的數據流計算模型使其成為理想的選擇大量的FPGA應用,無論是純CPU協同處理,CPU采集數據的預處理還是后處理,還是僅涉及不涉及CPU的系統(網絡,廣播,視覺,醫療等應用)無線,HPC等。)

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601867 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21654 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27724 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42982

發布評論請先 登錄

相關推薦

基于直方圖算法進行FPGA架構設計

如何使用Verilog HDL進行FPGA設計

FPGA 是如何分類的?FPGA的使用方法

基于FPGA的軟件定義無線電參考設計

對FPGA進行系統設計的Xilinx軟件使用方法

FPGA 開發經驗與技巧—ORCAD 與 FPGA 軟件協同設計

QuickPlay迅速構建基于 FPGA 的高效應用

基于軟件測試技術的FPGA測試研究[圖]

FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法

來自Digilent設計大賽的FPGA上的軟件定義無線電

使用QuickPlay進行軟件定義的FPGA計算 最新的FPGA設計方法

使用QuickPlay進行軟件定義的FPGA計算 最新的FPGA設計方法

評論