由于制造技術的進步,存儲系統在過去幾年中發展了很多。高帶寬存儲器(HBM)是最新類型的存儲器芯片的一個例子,它可以支持低功耗,超寬通信通道和堆疊配置。 HBM子系統涉及不同類型的存儲器控制器(全速,半速),HBM PHY和HBM DRAM。 HBM子系統適用于涉及高性能圖形和計算,高端網絡和通信設備以及需要大量內存的處理器的應用。由于其關鍵的最終應用程序角色,驗證HBM子系統中涉及的所有設計組件至關重要。在這里,我們將討論HBM PHY的作用,以及主要的驗證方面/挑戰。

簡介

HBM PHY是整個HBM系統解決方案的關鍵要素。 HBM PHY通常通過DFI接口從存儲器控制器接收HBM DRAM row-col命令,數據,奇偶校驗等,并將它們與HBM DRAM接口一起傳遞給HBM存儲器。它處理兩種不同的接口,支持DFI接口的多種頻率比。理想情況下,HBM PHY需要支持所有HBM存儲器功能,如頻率比,數據速率,存儲器大小,偽通道模式,傳統模式,DBI,DM等.HBM PHY可以在子系統級別和塊級別進行驗證,具有不同的,供應商特定的內存控制器和HBM內存。

驗證策略

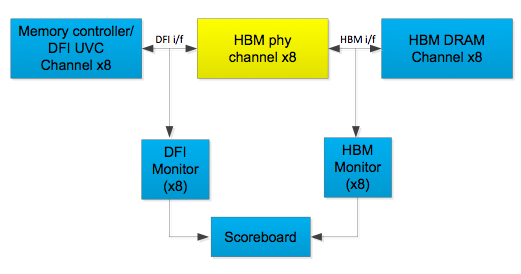

圖1驗證策略流程

要驗證HBM PHY設計,我們需要以下組件:HBM內存控制器或DFI驅動程序UVC(通用)驗證組件)用于驅動DFI接口:

DFI接口信號可能是特定于實現的,但它們應遵循所謂的DFI3.1協議。供應商特定的內存控制器可以是單端口或雙端口。 DFI接口涉及控制接口,寫數據接口,讀數據接口,更新接口,狀態接口和培訓接口的階段0和階段1信號。當選擇頻率比1時,控制器將僅以與HBM DRAM存儲器時鐘頻率相同的頻率驅動0相信號(* p0)。支持頻率比為2的控制器將在兩個階段上驅動:phase0(* p0)和phase1(* p1),占DRAM內存時鐘頻率的一半。

AMBA APB總線可用于配置和初始化用于HBM DRAM的存儲器控制器,如DM,DBI,延遲等。存儲器地址和數據可以使用AMBA AXI總線或任何供應商專用接口提供。一旦通過APB接口初始化和配置存儲器控制器,存儲器控制器將獲得讀寫地址并通過AXI總線或其他供應商特定接口寫入數據。 APB/AXI/供應商特定的UVC將用作存儲器控制器的配置和數據驅動程序。

完全隨機化,時序控制,無縫事務,row-col命令控制&但是,內存控制器不支持很少的模式操作。因此,功能驗證可能存在覆蓋漏洞。為了實現完全隨機化,時序控制,基于命令控制系統Verilog -UVM的DFI UVC用于驅動DFI信號。

用于接收DRAM寫入讀取的HBM內存

供應商特定的HBM內存可用于連接HBM PHY HBM JEDEC接口。該HBM存儲器將從HBM PHY接收HBM命令,數據,數據掩碼,奇偶校驗等。通常,所有內存模型都提供內置協議斷言。每個HBM設備都具有特定于供應商的功能,功能和時序。 HBM內存模型將在VCS/IUS/Questa工具中加密;因此,驗證環境應與所有工具兼容。應根據HBM內存的所有支持功能驗證HBM PHY。

DFI Monitor,HBM Monitor

DFI監視器將捕獲row-col地址;從DFI接口寫入數據,讀取數據,數據掩碼,數據總線反轉等信息。在寫入操作期間,它將基于DBI和DM值存儲寫入數據,并且在讀取操作期間,它將讀取的數據與先前存儲的寫入數據進行比較。類似地,HBM監視器將僅捕獲駐留在HBM DRAM接口中的row-col地址,寫入數據,讀取數據,數據掩碼,數據總線反轉等信息。由于DFI監視器正在執行相同操作,因此無需在HBM監視器中進行內存寫入讀取比較。 DFI監視器應支持頻率比為1和2。兩個監視器都是用UVM方法開發的,并為其他驗證組件提供HBM數據包。

DFI接口和DRAM接口之間的記分板

記分板將獲得HBM來自DFI監視器和HBM監視器的數據包。在寫入傳輸的情況下,將來自DFI監視器的HBM數據包與來自HBM監視器的HBM數據包進行比較。 HBM監測的HBM數據包與DFI監測的HBM數據包進行比較。

驗證挑戰

主要是行為內存模型已加密,因此調試仍然是一項挑戰。但是內存斷言會記錄任何HBM DRAM時序違規。 DFI,HBM監視器和記分板將幫助調試問題。

頻率比1:2在DFI驅動程序和DFI監視器中實現。 DFI接口需要以HBM時鐘頻率的一半頻率驅動2個不同相位(P0和P1)的信號。

存儲器控制器和其他存儲器設備的功能限制將無法完全驗證HBM PHY。 DFI UVC可以克服內存控制器的局限性,這意味著不同的內存模型可以集成到測試平臺中以覆蓋全部功能。

驗證環境應該是工具(VCS,IUS,Questa) - 獨立作為內存模型可以在任何工具中加密 - IUS,VCS,Questa。基于System Verilog-UVM的驗證環境將提供獨立于工具的平臺。

處理全速和半速模式的無縫寫入/讀取,在DFI驅動程序,DFI監視器,HBM監視器中需要系統架構。

使用APB接口初始化和配置所有內存控制器需要測試芯片級驗證,這需要大約10分鐘的模擬時間。因此,調試時間會增加。

常見問題

時間違規和寫入讀取內存模型的延遲限制將產生錯誤的讀取數據,主要是“x”。

門級仿真將為設計中的未初始化的觸發器產生“x”。工具&使用開關設計特定的初始化以初始化具有某些已知值的所有觸發器將有助于克服此問題

-

PCB打樣

+關注

關注

17文章

2968瀏覽量

21652 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27723 -

HBM

+關注

關注

0文章

373瀏覽量

14707 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42982

發布評論請先 登錄

相關推薦

HBM PHY的作用 以及驗證方面的一些難點介紹

HBM PHY的作用 以及驗證方面的一些難點介紹

評論