印刷電路板(PCB)布局審查會議期間的一個常見問題是,“50歐姆的痕跡是用于這種PCB布局中的數字信號?“這個問題的答案常常是”是“。然而,在做出平衡成本,性能和可制造性的決策時,正確答案也可能是“否”或“不適用于所有數字信號。”替代方法可包括關注PCB傳輸線的“受控阻抗”和/或使用其他跟蹤阻抗值。

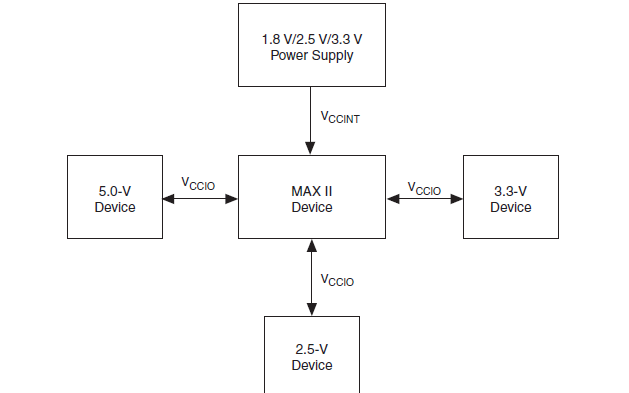

讓我們檢查一下層疊設計,看看PCB走線寬度如何影響層數(成本)和走線阻抗(性能)。在圖1中,相同寬度的布線通道顯示在三條PCB傳輸線的信號層上:100歐姆差分對,50歐姆和60歐姆單端。

圖1:相同寬度的路由通道顯示在三個信號層上用于100歐姆差分對,50歐姆和60歐姆單端的PCB傳輸線

100歐姆差分對通常在單個之前確定 - 應該安裝在路由通道(通孔之間)而沒有不連續性,因為它們通常用于更高速的數字信號。一旦設計了100歐姆差分對的走線寬度和間距,通常相應地確定同一層上50歐姆或60歐姆單端的走線寬度。單獨改變單端走線的走線寬度將導致不同的走線阻抗。每個通道的走線布線產量為:

右:一個100歐姆差分對,4mil走線/5.5mil空間。

中間:兩個60-單端有4mil走線/4mil空間的歐姆走線。

左:一個50歐姆走線,單端有6.5mil走線/7.4mil空間。

注意:此示例假設最小走線寬度和間距為4mils。

在這種情況下,工程師需要做出權衡決定,使用50歐姆的走線,這會占用更多的PCB空間和更多的層,或60歐姆的走線,這樣可以減少PCB空間,減少PCB層數。/p>

使用IC參考設計

IC制造商提供的文檔中的參考設計和建議通常用作原理圖的起點板級硬件設計中的PCB和PCB布局。

在這些文檔中設計高速數字互連所采用的技術很可能在特定終端產品的設計中重復使用。例如,由于參考示意圖中存儲器的大操作裕度,可能已經確定了使用沒有終止的存儲器接口的決定。但是,為了節省成本,設計工程師可以選擇具有與參考設計中使用的I/O緩沖特性不同的I/O緩沖特性的備用設備。然后,工程師需要確定未端接的存儲器接口是否應保留在新設計中。

-

pcb

+關注

關注

4317文章

23010瀏覽量

396341 -

走線

+關注

關注

3文章

113瀏覽量

23861 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21656 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27724 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42983

發布評論請先 登錄

相關推薦

印刷電路板布局中 仔細觀察PCB走線

印刷電路板布局中 仔細觀察PCB走線

評論