無線RF接收器在許多應用中都會用到,包括無線安全系統、工業監控、儀表讀數和家庭自動化等等。過去,半導體供應商主要使用模擬設計來構建這些接收器。如今,供應商正在轉換到數字和混合信號設計,以期降低功耗和簡化與其他組件的集成。

對于基于模型的設計,Semtech工程師擴展了對MathWorks工具的使用,目的是為了過渡至數字平臺。多年來,工程師使用MATLAB和Filter Design HDL Coder為濾波器建模和生成HDL代碼。在最近的項目中,他們使用了Simulink和HDL Coder為整個設計生成VHDL。

Semtech SX1231 無線收發器

挑戰

Semtech工程師需要使用低IF架構為頻移鍵控(FSK)和最小頻移鍵控(MSK)解調開發數字接收器鏈。他們希望在工程的先期研究階段,就針對性能、功耗和布局等性能,評估多種設計。為每個設計備選方案編寫VHDL較為費時,而且限制了團隊可以考慮的備選方案數量。

除了原型制作階段外,Semtech工程師希望改善傳統的產品代碼開發工作流程。“對系統進行建模,確保它們符合要求之后,我們以往是在VHDL中重新實現模型,然后在新工具中重新執行仿真”,Prianon說道。“這樣做隨時都有可能引入錯誤,并且我們永遠無法保證模型完全與新的VHDL代碼一致。”

解決方案

Semtech使用MathWorks工具進行基于模型的設計,來快速探索和評估各種設計思想,自動生成產品級VHDL代碼,改善工程師團隊之間的協作,從而加快用于FSK和MSK解調的數字接收器鏈開發。

在先期研究階段,Semtech工程師根據系統需求規范在Simulink中創建了浮點模型。他們使用來自Communications System Toolbox中的模塊對信道中的噪音進行建模,并實現FSK和MSK解調。

借助Signal Processing Toolbox以及DSP System Toolbox,一位工程師設計并分析了級聯積分梳狀(CIC)和有限脈沖響應(FIR)數字濾波器,而另一位工程師則使用Simulink分析設計sigma-delta模數轉換器(ADC)、鎖相環路(PLL)以及整個系統的其他部分。

一旦分別完成數字接收器鏈的各個部分的仿真,工程師就可以相互共享Simulink模型,從而在完成系統集成之前驗證自己的組件設計是否可以共同工作。

“手工編寫VHDL沒有任何優勢可言。編寫VHDL是一件非常枯燥的事情,還需要驗證手寫代碼。利用Simulink和HDL Coder,一旦完成對模型的仿真,就可以直接自動生成VHDL,并使用FPGA進行原型驗證。這樣可以節省大量時間,并且生成的代碼還包含一些我們未曾想到的優化。”

—— Frantz Prianon, Semtech

工程師運行仿真來驗證設計,并使用Communications System Toolbox中的誤碼率計算模塊來計算誤碼率。

借助Fixed-Point Designer,他們將設計從浮點轉變為固定點表示形式,從而進行比特位級的仿真。

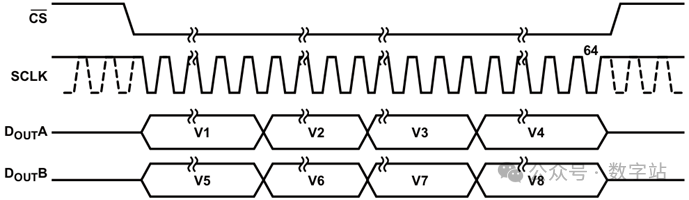

Semtech工程師使用HDL Coder從完整的接收器鏈的Simulink模型生成VHDL。為了驗證VHDL,他們使用了HDL Verifier來通過Mentor Graphics Questa仿真器聯合仿真以驗證其Simulink設計與生成VHDL代碼的一致性。

結果

創建原型的速度提高了50%。“在我們自行編寫VHDL時,通常需要兩個月才能創建FPGA原型”,Prianon說道。“借助Simulink和HDL Coder,我們無需再對每個模塊進行繁瑣的手動編碼,只需數周便可創建原型。

驗證時間從數周縮短為數天。“在之前的項目中,我們至少需要花兩周時間來編寫用于驗證VHDL的測試用例”,Prianon回想說。“借助HDL Verifier,我們可以進行聯合仿真,測試模型中的多個關鍵點,并驗證VHDL,通常不到一天就可以完成。”

最終交付經過優化、性能更佳的設計。基于模型的設計讓Semtech可以將從需求到下線的開發時間縮短 33%。“我們用節省下來的時間改善設計”,Prianon說。“MathWorks工具讓我們可以探索更多備選方案和新功能,最終提供優化更好、效果更佳的設計。”

-

收發器

+關注

關注

10文章

3399瀏覽量

105865 -

濾波器

+關注

關注

160文章

7731瀏覽量

177693 -

接收器

+關注

關注

14文章

2458瀏覽量

71800

發布評論請先 登錄

相關推薦

MATLAB基于FPGA和ASIC的數字收發器的開發和利用分析

MATLAB基于FPGA和ASIC的數字收發器的開發和利用分析

評論