HDL Verifier 發布新功能用來加快 FPGA 在環 (FIL) 驗證。利用新的 FIL 功能,可以更快地與 FPGA 板通信,實現更高的仿真時鐘頻率。現在,系統工程師和研究人員可以自信地快速確認和驗證 FPGA 設計在系統中按預期方式工作,從而節省開發時間。

隨著信號處理、視覺影像處理和控制系統算法的復雜度不斷增加,在 FPGA 板上對硬件實現進行仿真,可以幫助驗證設計在其系統環境中的工作情況。用于 FIL 驗證的 HDL Verifier 自動設置 MATLAB 和 Simulink 測試環境,并將其與運行于 FPGA 開發板上的設計相連接。這有助于實現在實際硬件上運行的 FPGA 設計的高逼真度協同仿真,同時復用開發階段使用的測試環境。

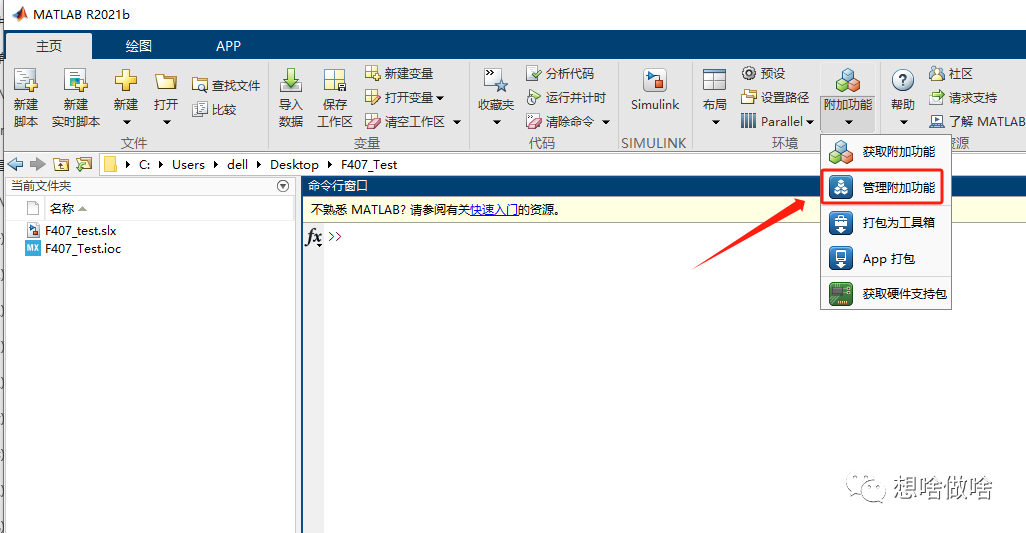

使用 HDL Verifier 在代碼生成前用測試工作臺對設計進行仿真,確保沒有運行時錯誤。

MATLAB R2016b允許工程師為其 FPGA 系統時鐘指定一個自定義頻率,時鐘頻率可比以前使用 FIL 的時候快五倍。對于在以 FPGA 為目標時使用超頻因子的設計,如控制應用程序,可以使用較大的數據輸出規模來提高吞吐量。工程師現在還可以利用 FIL(使用 PCI Express接口)來加快 MATLAB 和 Simulink 以及 Xilinx KC705/VC707 和 Intel Cyclone V GT/Stratix V DSP 開發板之間的通信,仿真速度比千兆以太網快 3-4 倍。

“隨著電子系統日益復雜,作為驗證步驟,精確地驗證設計原型變得至關重要。” MathWorks 的產品經理 Jack Erickson 說,“現在,HDL Verifier 允許工程師在真實硬件上以現實的時鐘頻率快速運行設計。能夠從 MATLAB/Simulink 這樣方便的算法開發環境進行 FPGA 在環仿真,使硬件設計驗證大幅簡化。”

MathWorks是數學計算軟件領域世界領先的開發商。它所推出的MATLAB是一種用于算法開發、數據分析、可視化和數值計算的程序設計環境,稱為“科學計算的語言”。Simulink是一種圖形環境,可用于對多域動態系統和嵌入式系統進行仿真和基于模型設計。全球的工程師和科學家們都依賴于MathWorks公司提供的產品系列,來加快在汽車、航空、電子、金融服務、生物醫藥以及其他行業的發明、創新及開發的步伐。

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601838 -

嵌入式系統

+關注

關注

41文章

3567瀏覽量

129227

發布評論請先 登錄

相關推薦

【干貨分享】硬件在環仿真(HiL)測試

EasyGo使用筆記丨分布式光伏集群并網控制硬件在環仿真應用

EasyGo使用筆記丨分布式光伏集群并網控制硬件在環仿真應用

EasyGo實時仿真丨飛輪儲能系統硬件在環仿真測試

Enclustra FPGA核心板在硬件在環(HiL)仿真測試系統中的應用

如何創建硬件在環工程

新增FPGA硬件在環測試的結果和過程分析

新增FPGA硬件在環測試的結果和過程分析

評論