設計人員總是在尋找減少不需要的功耗組件的方法,無論是通過以低功耗技術的方式設計設計,還是采用可以降低功耗的工藝。但是,其中一些解決方案的代價是性能,可靠性,芯片面積或其中的幾個。最終,人們必須在功率,性能和成本之間達成妥協。下面的文章旨在討論其中的一些技巧。這些技術分為建筑技術和基于過程的技術。

架構功耗降低技術:在RTL級別,可以采取幾個步驟來降低器件的總功耗。通常,基于RTL的技術最小化設備的動態功耗,然而,使用諸如功率門控之類的技術,還可以降低芯片的一部分的泄漏功率。各種常用的技術有:

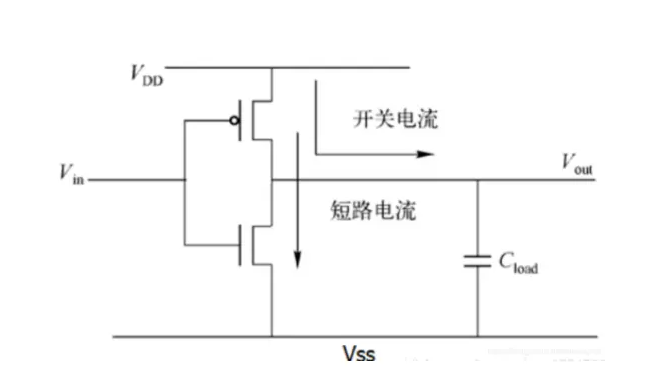

1.1。時鐘門控:這種技術是一種非常流行的動態功耗降低技術。動態功耗是瞬態功耗(P 瞬態)和容性負載功率(P cap )消耗的總和。 P transient 表示當設備改變邏輯狀態時消耗的功率量,即“0”比特到“1”比特,反之亦然。顧名思義,電容負載功耗代表用于為負載電容充電的功率。總動態功率如下:

P dynamic = P cap + P transient =(C L + C)V dd 2 f N 3

其中C L 是負載電容,C是芯片的內部電容,f是工作頻率,N是切換的位數。由于動態功耗與MOS單元的切換直接相關,因此在不需要時選通時鐘有助于降低動態電流。這種技術有助于保持設計狀態,同時僅限制瞬態電流。設計人員經常使用AND/NOR門來為時鐘門控,但是,基于鎖存器的時鐘門控是最受青睞的技術,因為它還可以節省設計的危險,否則會帶來額外的功耗,這是動態功耗所固有的。

1.2。可變頻率/頻率島:在大芯片中,并非所有模塊都需要以盡可能高的頻率進行時鐘控制,以達到所需的性能水平。可能存在很少的塊本身工作緩慢(例如,慢速通信塊,如I 2 C,UART等),因此,可以以比核心/處理器之類的塊更慢的時鐘計時。高頻時鐘,實現最大吞吐量。因此,通過向不同的塊提供不同的頻率時鐘,可以減少局部動態消耗。

圖1:頻率島

1.3。電源門控:可能存在某些低功耗模式下可能不需要芯片某些模塊運行的應用如睡眠,深度睡眠,待機模式等,只需要設備的一部分即可運行。在這種情況下,關閉非功能塊是有意義的,這樣設備就不必為未使用的塊供電。這不僅有助于降低動態消耗,而且還為這種電源門控塊節省了泄漏功率。然而,在處理這種技術時,設計必須確保來自電源門控模塊的信號在低功率工作時不會影響功能模塊。為此,隔離塊放置在路徑中,這樣就不會發生功能損壞,如圖2所示。請注意,從always-ON域到其他電源域的信號不需要隔離信號。因為他們永遠不應該是非確定性的。

圖2:電源門控

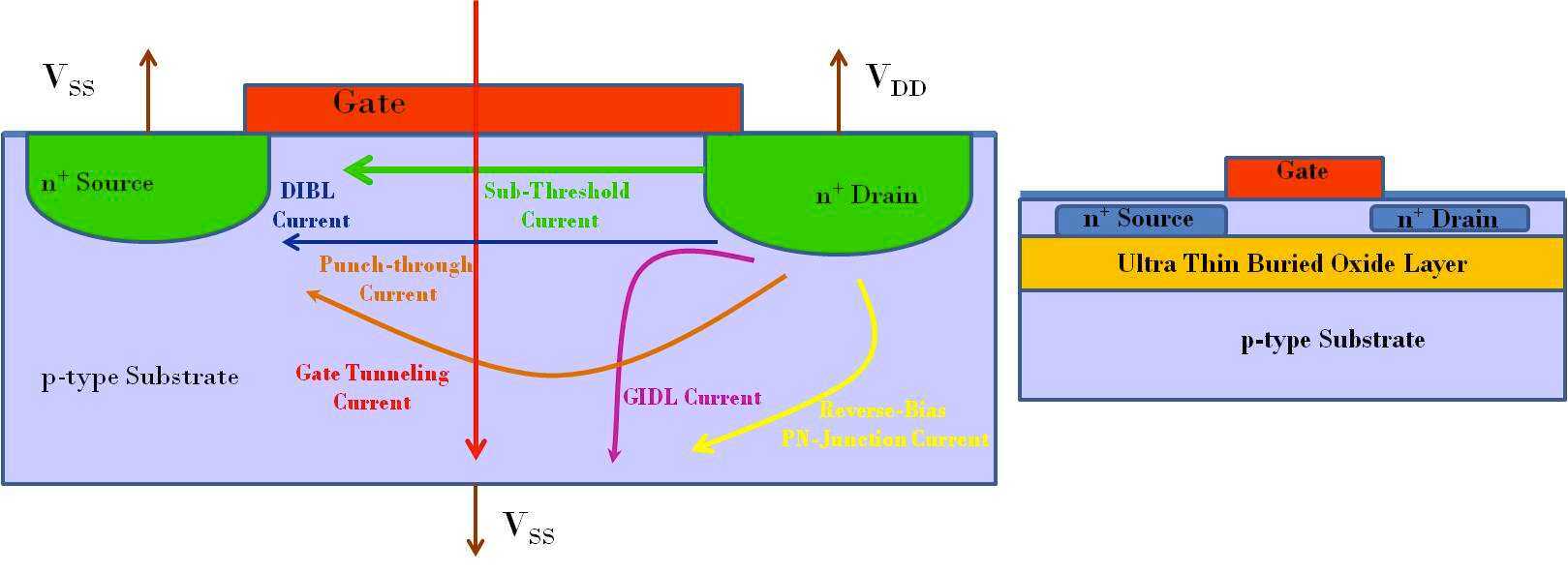

基于過程的電源減少技術:有很多功耗組件并不是所有組件都可以單獨使用建筑技術。使用基于工藝的技術可以最有效地控制由于漏極引起的勢壘降低,柵極引發的漏極泄漏,亞閾值泄漏等影響而導致的功耗。以下是一些最常用的基于過程的技術:

2.1多閾值電壓CMOS單元:許多MOS特性受閾值電壓的控制。細胞。亞閾值電流是柵極電壓低于閾值電壓時源極和漏極之間的電流。該電流近似值的數學表達式為:

可以看出,當閾值電壓V T 增加了。因此,可以放置更高的V T 細胞以減少該組分。然而,正如我們在上面的傳播延遲中所看到的,增加V T 對操作頻率具有負面影響。因此,設計人員必須采用一種策略來混合較低的V T 和較高的V T 單元,以減少漏電流,同時保持所需的工作頻率。為了實現這種策略,高V T 單元被用作休眠晶體管,當塊應該處于待機模式時,它將電源選通到更低的V T 設計。當器件處于工作模式時,這些睡眠晶體管導通,此睡眠晶體管下游的低V T 模塊可以獲得電源并照常工作。這有助于減少待機模式下的電流。或者,根據時序關鍵路徑與非時序關鍵路徑對各種數據路徑進行分類。定時關鍵路徑可以使用較低V T 的單元(稱為LVT(較低V T )單元)來實現,以便可以在更短的時間內實現相同的操作與用高V T 細胞(也簡稱為HVT細胞)實施的路徑相比。即使芯片處于運行模式,這種混合使用方法也可以平衡漏電流。

另一種解決方案是根據應用程序要求動態更改單元格的V T 。這可以通過使用控制電路改變阱/體偏置電壓來實現。這需要更復雜的MOS制造,因為它需要雙阱或三阱制造技術。這通常稱為可變閾值CMOS(VTCMOS)。然而,應該注意的是,降低V T 也會影響芯片的可靠性,因為即使更低的電壓擺幅也會導致邏輯以錯誤的方式開始工作。這些電壓擺動可能由于各種過程或環境變化而產生。因此,在降低細胞的V T 時必須非常謹慎,以免損害最終應用的神圣性。

2.2Mutli V DD 技術:從上面的等式可以看出,器件電壓V DD <之間存在二次關系/sub>和動態功耗。因此,可以通過降低電源電壓來顯著降低動態電壓。然而,電壓降低也有其缺點。細胞的傳播延遲如下:

從上面的等式可以看出,V DD 的減少增加了細胞的延遲。結果,當降低電源電壓時,電池的工作頻率降低。因此,必須在電壓供應和相關性能之間保持平衡。

圖3:電壓島 - 多V DD 操作

該挑戰的解決方案可以是在設計中創建電壓島,其中可以使用較低電源電壓為低性能慢速外設供電,并且可以使用更高電壓為性能關鍵模塊供電。但是,設計必須確保將適當的電壓電平轉換器放置在那些通過電壓域通信的信號上。

該技術還可以降低器件中的柵極感應漏極泄漏效應和相關的功耗。

2.3動態電壓和頻率調節:電壓島技術,也稱為靜態電壓調節,在操作器件時幾乎沒有限制。該技術不適應應用需求,并且一旦設計就不能改變對塊的電壓供應。然而,動態電壓調節技術使設計者和客戶擺脫了這些限制。該技術利用調節器,該調節器可被編程以根據需要提供電壓電平。因此,各種塊可以獲得可配置的電壓,并且客戶/用戶可以根據應用設置改變電壓設置。這有助于動態節省電力。還使用了各種解決方案,其中設計釋放了軟件以改變電壓縮放。設計本身可以檢測器件中的電流負載要求,并相應地進行電壓調整。該技術以更自適應的方式幫助降低功耗。

相同的電壓調整也可以通過動態頻率調整進行調整,其中可以根據需要通過軟件更改塊的頻率。因此,在較低的V DD 上運行的塊可以由較慢的時鐘計時,同時保持性能和功能要求。該技術有助于降低器件的動態功耗和漏電功耗。

圖4:差分電壓和頻率調節

2.4絕緣體上完全耗盡的硅(FDSOI):這是另一種有助于減少泄漏電流的各種成分的技術較低技術節點的威脅。使用這種技術可以非常有效地控制漏電元件,如GIDL,反向偏置電流和柵極隧道電流。在這種技術中,MOS位于超薄氧化膜上,使細胞與身體其他部分隔離。在該氧化膜的頂部,沉積非常薄的硅層,其用作溝道。由于其薄,可以在該層中建立通道而無需任何額外的摻雜。因此,它被稱為完全耗盡的SOI。

圖5:FDSOI單元(左)和CMOS單元中的各種漏電流(右)

在另一種技術中,在柵極下方的耗盡區中沉積小的中性區域。這里,溝道厚度不必像FDSOI中所要求的那么薄。這被稱為部分耗盡的SOI(PDSOI)。然而,與FDSOI相比,PDSOI傾向于具有更高的V T (因此操作更慢)和更大的柵極效應(因此,更大的漏電流)。因此,由于對V T 的更好控制和急劇減少的漏電流,FDSOI是小工藝節點(通常低于90nm)的首選。

-

低功耗

+關注

關注

10文章

2362瀏覽量

103607 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21659 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27727 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42990

發布評論請先 登錄

相關推薦

降低FPGA功耗的設計技術

微處理器的低功耗芯片設計技術詳解

怎么降低動態功耗?

實現降低FPGA設計的動態功耗的解決方案

淺析CMOS集成電路的動態功耗

通過動態開啟/關閉負載來降低功耗的參考設計

動態電壓與頻率調節在降低功耗中的作用

cmos動態功耗公式,cmos動態功耗和哪些電路參數有關

非常流行的動態功耗降低技術介紹

非常流行的動態功耗降低技術介紹

評論