今天的關鍵瓶頸設計團隊并不是設計芯片系統(tǒng)的復雜性,也不是設計時間短,而是設計的驗證。

驗證設計在整個過程中的功能是否正確設計流程是一種資源匱乏。一個設計團隊估計其CPU周期的90%用于模擬。對50%-70%的人力資源進行驗證的估計是常見的。只會變得更糟 - 驗證復雜性隨著設計規(guī)模的增加呈指數(shù)增長。除非驗證瓶頸得到解決,否則未來電子系統(tǒng)的成本將會上漲。

解決問題需要新的軟件工具和/或方法,就像過去一樣。例如,當物理設計成為瓶頸時,開發(fā)了自動布局和路徑工具來取代布局編輯器。當designentry成為問題時,開發(fā)了綜合工具,以便為每個設計師提供更多的功能。然而,驗證仍然是一項手動任務。這對于具有數(shù)千門的設計是可以接受的,但是對于當今復雜的,數(shù)百萬門的設計來說,手動驗證是非常有限的,這些設計太大而且復雜,無法在合理的數(shù)量內完全檢查時間。

公司正在努力解決這個問題,并投入大量資金投入人力和技術解決方案。此外,芯片上系統(tǒng)(SoC)將其自身的驗證問題融入其中。 SoC工程師面臨的一些問題涉及外部開發(fā)的知識產權(IP)的集成和驗證以及硬件與其嵌入式軟件之間的交互。隨著越來越多的設計包括外部開發(fā)的IP,公司將如何整合和驗證這些模塊作為其整個系統(tǒng)的一部分?而且,隨著更多的片上系統(tǒng)設計包括處理器,公司將如何解決硬件和嵌入式軟件之間復雜的相互依賴性?很明顯,驗證將繼續(xù)成為一個嚴重的問題,需要重新考慮驗證方法。

工程團隊必須采用新的驗證方法,才能具有競爭力。由于芯片中出現(xiàn)意外情況而錯過市場窗口可能是災難性的。想象一下,個人計算機制造商不得不重新設計芯片并延遲其PC的運輸,因為直到設計周期的后期才發(fā)現(xiàn)一個嚴重的錯誤。

驗證不完整或不充分是設計失敗和產品被迫的原因想念他們的市場窗口。但它不一定是這樣。復雜的芯片,系統(tǒng)和SoCdesigns迫使我們重新考慮我們的驗證方法。我們不得不更新和改善我們的環(huán)境。

解決這個瓶頸包括在設計流程中更早地移動驗證,以便盡可能少地保持當前流量的自動化手動任務。

一般來說,定義和討論驗證是值得的。驗證的良好工作定義是“證明設計符合您的要求。”具體來說,工程師根據(jù)設計編寫測試并檢查它是如何對這些測試做出反應的。但是,由于當今設計的復雜性,工程師如何知道設計已經過全面測試,發(fā)現(xiàn)了所有的錯誤?他們怎么知道他們有測試了芯片的每一種可能用途?一種常見的方法是繼續(xù)手動編寫新測試并運行模擬直到工程師停止發(fā)現(xiàn)錯誤,但這個過程很快就變得不可能了。

更好的方法是自動化驗證過程。自動生成功能測試,數(shù)據(jù),時間檢查和功能覆蓋分析有助于工程師發(fā)現(xiàn)他們沒有想到的錯誤 - 通常由目標系統(tǒng)的規(guī)范和/或意外使用中的模糊引起的錯誤。并且適當?shù)母采w率指標可以快速指出設計的哪些部分尚未經過測試。這些指標非常重要,因為它們提供了驗證進度和驗證效率的視圖。

驗證已成為電子設計中最關鍵的瓶頸。它必須立即解決,否則成本合計的電子系統(tǒng)將會飆升。這只能通過自動化驗證過程來實現(xiàn)。自動化將對設計進行更全面的測試,從而創(chuàng)建更高質量的產品,并且它可以比目前使用的任何手動過程更快地實現(xiàn)這一目標。

-

芯片

+關注

關注

453文章

50406瀏覽量

421840 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21653 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27724 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42982

發(fā)布評論請先 登錄

相關推薦

LED產業(yè)發(fā)展面臨六大瓶頸

智能家居發(fā)展的瓶頸是什么?如何才能突破瓶頸?

什么是SoC驗證平臺自動化電路仿真?zhèn)慑e功能?

物聯(lián)網發(fā)展有什么瓶頸?

各種驗證技術在SoC設計中的應用

通用微處理器功能驗證中的仿真加速

Mentor驗證解決方案在龍芯處理器設計中的應用

SOC設計驗證方法的探索

基于覆蓋率的功能驗證方法

基于OVM驗證平臺的IP芯片驗證

通過靜態(tài)時序分析驗證設計的正確性

如何解決大芯片的驗證痛點

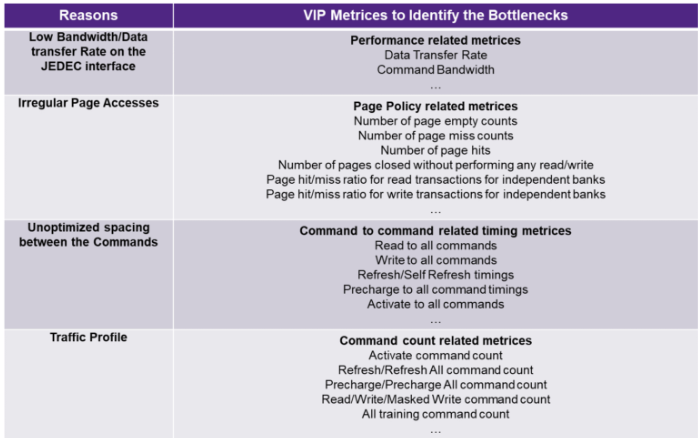

使用內存VIP檢測和避免內存瓶頸

如何解決電子元器件遭遇高溫環(huán)境使用效能大打折扣的技術瓶頸

如何解決驗證瓶頸問題

如何解決驗證瓶頸問題

評論