在線測(cè)試(ICT)系統(tǒng)一直是使用電子手段尋找PCB中結(jié)構(gòu)缺陷的領(lǐng)導(dǎo)者。他們使用釘床固定裝置同時(shí)提供多達(dá)7000個(gè)左右的電路節(jié)點(diǎn)的電氣訪問(wèn)。但隨著多層板和球柵陣列(BGA)封裝的普及,電路接入并不是雙列直插式封裝(DIP)和分立元件填充的單面PCB時(shí)代。為了彌補(bǔ)缺乏對(duì)電氣測(cè)試點(diǎn)的物理訪問(wèn),已經(jīng)出現(xiàn)了邊界掃描,以提供對(duì)夾具釘不可訪問(wèn)的節(jié)點(diǎn)的訪問(wèn)。此外,它提供了無(wú)夾具測(cè)試替代方案,即使在可以訪問(wèn)時(shí)也是如此。

邊界掃描最初是在1985年提出的,并于1990年成為IEEE 1149.1標(biāo)準(zhǔn)。但它一直很慢,因?yàn)樗枰狪C制造商生產(chǎn)的設(shè)備與邊界掃描規(guī)范兼容(參考文獻(xiàn)1)。每個(gè)器件必須物理上包括標(biāo)準(zhǔn)定義的4線測(cè)試訪問(wèn)端口(TAP),每個(gè)引腳的內(nèi)部邊界掃描單元,以及相關(guān)的內(nèi)部邊界掃描寄存器和其他電路。此外,設(shè)備供應(yīng)商必須提供描述芯片邊界掃描功能工作的邊界掃描描述語(yǔ)言(BSDL)文件。這曾經(jīng)意味著IC制造商不愿意制造的復(fù)雜性以及客戶不愿意支付的芯片成本。然而,逐漸地,PCB測(cè)試點(diǎn)訪問(wèn)問(wèn)題被證明比制造具有成本效益的邊界掃描兼容數(shù)字設(shè)備的問(wèn)題更加強(qiáng)大,并且電路板設(shè)計(jì)者現(xiàn)在可以從各種邊界掃描兼容設(shè)備中進(jìn)行選擇以填充他們的電路板(參考文獻(xiàn)2)。

即使設(shè)計(jì)人員開(kāi)始在PCB上安裝邊界掃描兼容設(shè)備,測(cè)試工程師也很少能夠充分利用邊界掃描的承諾。這是因?yàn)椋琂TAG Technologies的常務(wù)董事Harry Bleeker說(shuō),經(jīng)典ATE公司利用這項(xiàng)技術(shù)只是為了提高ICT的質(zhì)量,通過(guò)釘床提供邊界掃描矢量 - 一種稱為邊界在線測(cè)試的技術(shù)(BICT) - 但并沒(méi)有取代對(duì)釘床的訪問(wèn)要求。

BICT的目標(biāo)是加快測(cè)試程序的開(kāi)發(fā)。在20世紀(jì)90年代早期,ASSET InterTech的總裁,首席執(zhí)行官和創(chuàng)始人Glenn Woppman表示,測(cè)試工程師可能需要數(shù)周才能為像英特爾386微處理器這樣的復(fù)雜部件制定ICT戰(zhàn)略。對(duì)于同一設(shè)備的邊界掃描兼容版本,測(cè)試開(kāi)發(fā)時(shí)間可縮短至數(shù)小時(shí)。 Woppman說(shuō),當(dāng)時(shí),電路板設(shè)計(jì)人員和ATE供應(yīng)商都沒(méi)有推動(dòng)全面的基于邊界掃描的測(cè)試策略,因此設(shè)計(jì)人員沒(méi)有完成設(shè)備之間的掃描鏈。

采用這種方法, ATE供應(yīng)商將每個(gè)兼容組件或明智設(shè)計(jì)的兼容和非兼容組件集(參考文獻(xiàn)3)視為孤立的邊界掃描島。當(dāng)90%到100%的測(cè)試節(jié)點(diǎn)可以進(jìn)入釘床時(shí),這種方法很有效。但是,釘床的覆蓋面正在縮小 - 沃普曼估計(jì),今天平均有50%的電路板節(jié)點(diǎn)可通過(guò)釘子進(jìn)入,到2005年這個(gè)數(shù)字將縮小到10%。

處理有限的通過(guò)訪問(wèn),設(shè)計(jì)人員可以連接掃描鏈,并通過(guò)低成本連接器提供掃描信號(hào)。這些連接器通過(guò)包括Acculogic,ASSET InterTech,Corelis,Goepel Electronics,Intellitech和JTAG Technologies在內(nèi)的公司的低成本邊界掃描測(cè)試硬件和軟件進(jìn)行電路板測(cè)試。

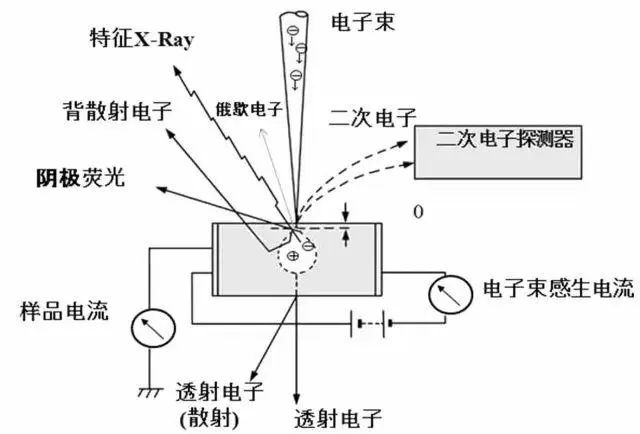

圖1 說(shuō)明了釘床和TAP連接器如何提供邊界掃描測(cè)試向量。 TAP本身包括四個(gè)信號(hào):測(cè)試數(shù)據(jù)輸入(TDI),測(cè)試模式選擇(TMS),時(shí)鐘(CLK)和測(cè)試數(shù)據(jù)輸出(TDO);一些實(shí)現(xiàn)方式也包括復(fù)位信號(hào)。這些信號(hào)控制邊界掃描單元的狀態(tài)(以黃色顯示),每個(gè)器件I/O引腳分配一個(gè)單元。在正常操作期間,這些單元將I/O引腳連接到器件內(nèi)部電路。

|

| 圖1。邊界掃描可以利用ICT釘子向安裝在PCB上的組件(如左側(cè)的組件)提供測(cè)試信號(hào)。球柵陣列封裝如右圖所示,需要通過(guò)PCB走線和測(cè)試訪問(wèn)端口連接器(底部)傳送信號(hào)。 |

置位TMS信號(hào)使得配置為串行移位寄存器的單元承載測(cè)試數(shù)據(jù),測(cè)試數(shù)據(jù)通過(guò)TDI和TDO線以每個(gè)時(shí)鐘周期一位移入和移出器件。多個(gè)互連設(shè)備的互連掃描單元寄存器形成掃描鏈;裝有邊界掃描設(shè)備的PCB可能有幾個(gè)掃描鏈,或者如Woppman所說(shuō),沒(méi)有。

如果PCB沒(méi)有掃描鏈,那么你必須使用BICT在邊界上進(jìn)行邊界掃描測(cè)試 - 掃描兼容設(shè)備。為了使用BICT測(cè)試圖1中的IC 1 ,釘子接觸每個(gè)器件焊盤(pán)(以灰色顯示)。選擇測(cè)試模式后,駐留在每個(gè)器件I/O引腳(藍(lán)色)上的測(cè)試數(shù)據(jù)值,使用TDI和TDO信號(hào)移入和移出器件,應(yīng)等于接觸相應(yīng)焊盤(pán)的釘子所測(cè)量的值。數(shù)據(jù)不匹配表明焊點(diǎn)不良。

BICT不適用于IC 2 ,但其焊球隱藏在其球下 - 網(wǎng)格數(shù)組包。但是,如果您的PCB設(shè)計(jì)人員將TAP信號(hào)路由到TAP,您可以通過(guò)TAP將測(cè)試信號(hào)傳輸?shù)絀C 2 的I/O引腳。外部連接器(圖1中的綠線)完成掃描鏈。在這種情況下,邊界掃描測(cè)試控制器可以將測(cè)試數(shù)據(jù)從TAP連接器轉(zhuǎn)移到IC 1 。連續(xù)測(cè)試數(shù)據(jù)將在九個(gè)時(shí)鐘周期后開(kāi)始出現(xiàn)在輸出A處。該模式應(yīng)同時(shí)出現(xiàn)在IC 2 輸入B及其關(guān)聯(lián)的掃描單元中。外部測(cè)試硬件可以驗(yàn)證該模式,該模式將在10個(gè)時(shí)鐘周期后的TDO開(kāi)始出現(xiàn)。如果未出現(xiàn)預(yù)期的圖案,則A處的焊點(diǎn),B處的焊點(diǎn),連接它們的走線或器件的內(nèi)部掃描電路都有缺陷。

符合邊界掃描的電路板因此,似乎為您提供了兩種測(cè)試方法:您可以使用價(jià)值數(shù)千美元的釘床固定裝置以及耗資數(shù)萬(wàn)美元的ICT ATE系統(tǒng),或者您可以使用邊界掃描控制器卡來(lái)計(jì)算成本幾百美元加一個(gè)TAP連接器可能花費(fèi)幾美分。

沒(méi)有明確的贏家

選擇不像你想象的那么明確。毫不奇怪,ICT ATE強(qiáng)國(guó)安捷倫科技和泰瑞達(dá)預(yù)測(cè)邊界掃描和信息通信技術(shù)的共生未來(lái),其技術(shù)在更密集的多氯聯(lián)苯中執(zhí)行互補(bǔ)功能。

邊界掃描公司的意見(jiàn)各不相同,其范圍從認(rèn)為邊界掃描測(cè)試將自主運(yùn)行ICT(如果不能取代它)到“如果你不能擊敗他們,加入他們”的方法預(yù)測(cè)ICT在執(zhí)行邊界掃描測(cè)試中的主要作用。后者以去年秋天安捷倫與邊界掃描供應(yīng)商ASSET InterTech宣布的聯(lián)盟以及邊界掃描系統(tǒng)制造商Acculogic的努力為例,總裁Saeed Taheri表示,通過(guò)開(kāi)發(fā)測(cè)試獲得30%至40%的收入第三方ICT系統(tǒng)戰(zhàn)略。自主邊界掃描測(cè)試的作用體現(xiàn)在Intellitech倡導(dǎo)的方法中,該方法采用嵌入式測(cè)試來(lái)執(zhí)行獨(dú)立于ICT平臺(tái)的數(shù)字測(cè)試,這將繼續(xù)提供簡(jiǎn)單的制造缺陷分析和模擬測(cè)試。除了由LogicVision和National Semiconductor(參考文獻(xiàn)4)開(kāi)發(fā)的IC之外,盡管IEEE已經(jīng)批準(zhǔn)1149.4模塊擴(kuò)展到原始的1149.1數(shù)字標(biāo)準(zhǔn),但模擬電路還不適合進(jìn)行邊界掃描測(cè)試。

Intellitech的總裁CJ Clark詳細(xì)闡述了他的公司的推理:“數(shù)字測(cè)試和邏輯配置時(shí)間正在增加,如果邊界掃描可測(cè)試PCB的數(shù)字測(cè)試和配置時(shí)間相對(duì)于其模擬測(cè)試和處理時(shí)間,對(duì)ICT進(jìn)行數(shù)字測(cè)試是沒(méi)有意義的。“他解釋說(shuō),如果包括FPGA,CPLD和閃存配置(參考文獻(xiàn)5)在內(nèi)的邊界掃描測(cè)試需要100秒,模擬測(cè)試需要5秒,那么僅采用ICT的方法將提供每105秒一個(gè)PCB的吞吐量。他說(shuō),更好的替代方案是在PCB本身內(nèi)嵌入邊界掃描測(cè)試功能,這樣邊界掃描測(cè)試的執(zhí)行只需要一個(gè)電源。通過(guò)這種方法,5-s模擬測(cè)試運(yùn)行在ICT上;然后將PCB從ICT夾具中取出,并通過(guò)邊界掃描自檢過(guò)程對(duì)其他PCB供電。

在前20個(gè)PCB經(jīng)過(guò)模擬測(cè)試(20 x 5 s)后,第一個(gè)PCB將完成其數(shù)字邊界掃描自檢和配置。在另外5秒內(nèi),進(jìn)行數(shù)字邊界掃描自檢的第二塊PCB將完成測(cè)試,依此類推。在對(duì)前20個(gè)PCB進(jìn)行測(cè)試后,嵌入式測(cè)試和配置取消了數(shù)字測(cè)試時(shí)間,PCB吞吐量變?yōu)槊?秒一個(gè)PCB,即模擬測(cè)試和處理所需的時(shí)間。

啟用實(shí)現(xiàn)在此替代方案中,Intellitech于6月推出了其正在申請(qǐng)專利的SystemBIST配置和測(cè)試處理器,該處理器在單個(gè)PCB或多PCB系統(tǒng)內(nèi)嵌入自測(cè)功能以及FPGA和CPLD的系統(tǒng)內(nèi)配置。 Clark解釋說(shuō),SystemBIST處理器提供的完全嵌入式測(cè)試功能可以在整個(gè)設(shè)備生命周期中使用,在原型設(shè)計(jì),加速生命周期測(cè)試期間以及大批量生產(chǎn)期間提供診斷信息。

SystemBIST處理器與符合IEEE 1149.1或IEEE 1532標(biāo)準(zhǔn)(參考文獻(xiàn)6)的任何設(shè)備兼容,并且可以取代通電時(shí)通常用于加載配置數(shù)據(jù)的電氣可變配置PROM。 Clark表示,封裝在144引腳TQFP IC中的SystemBIST處理器只需要基于PROM的替代PCB面積的一半。 SystemBIST功能也可用作VHDL或Verilog知識(shí)產(chǎn)權(quán)。

ICT提供掃描矢量

其他人認(rèn)為,在線測(cè)試儀仍然是提供邊界掃描信號(hào)的可行工具。為了利用ICT的優(yōu)勢(shì),ASSET InterTech和安捷倫科技去年秋天宣布達(dá)成協(xié)議。 ASSET InterTech的Woppman可能默認(rèn)同意Clark關(guān)于邊界掃描價(jià)值的信息,但是他開(kāi)玩笑說(shuō)他已經(jīng)等了十幾年才讓信息通信技術(shù)消失,他不打算再等十幾年。更嚴(yán)重的是,他將ICT用戶視為規(guī)避風(fēng)險(xiǎn)的類型,不太可能以主要的邊界掃描方式取代目前的測(cè)試策略。

漸進(jìn)式方法可能會(huì)減輕對(duì)此類類型的擔(dān)憂。 Acculogic的Taheri認(rèn)為邊界掃描在ICT中的重要性逐漸增加,而ICT的價(jià)值隨著時(shí)間的推移逐漸減少。最終,他看到邊界掃描上電測(cè)試結(jié)合飛針或功能測(cè)試(他將其定義為通過(guò)邊緣連接器或板連接器進(jìn)行測(cè)試訪問(wèn) - 而不是通過(guò)釘床)成為主流PCB測(cè)試技術(shù),提供現(xiàn)在可以從ICT獲得故障覆蓋和診斷解決方案。為了實(shí)現(xiàn)這些目標(biāo),Acculogic開(kāi)發(fā)了一種自適應(yīng)時(shí)鐘方案,允許在飛行探測(cè)器所需的幾米電纜上傳輸邊界掃描信號(hào),或者在環(huán)境室內(nèi)進(jìn)行功能測(cè)試。

Corelis總裁Menachem Blasberg已經(jīng)看到客戶放棄了ICT - 他說(shuō)他們會(huì)進(jìn)行邊界掃描測(cè)試,然后進(jìn)行全面的功能測(cè)試,以確保正確的實(shí)時(shí)數(shù)字和模擬性能。 Acculogic的Taheri更進(jìn)一步,將邊界掃描定義為測(cè)試執(zhí)行程序,建立適當(dāng)?shù)膬?nèi)部PCB邏輯狀態(tài),以促進(jìn)模擬功能測(cè)試。

隨著對(duì)合同制造商的日益依賴,對(duì)ICT的爭(zhēng)論變得更加復(fù)雜( CMs)用于測(cè)試服務(wù)。 Intellitech的Clark表示,他相信CM會(huì)抵制邊界掃描,因?yàn)樗麄兿M谝寻惭b的ICT系統(tǒng)上賣出時(shí)間。然而,JTAG Technologies的Bleeker指出,智能CM客戶開(kāi)始規(guī)定邊界掃描測(cè)試以降低成本,CM必須傾聽(tīng)。他說(shuō),全I(xiàn)CT方法專為沒(méi)有設(shè)計(jì)邊界掃描合規(guī)性的客戶使用。

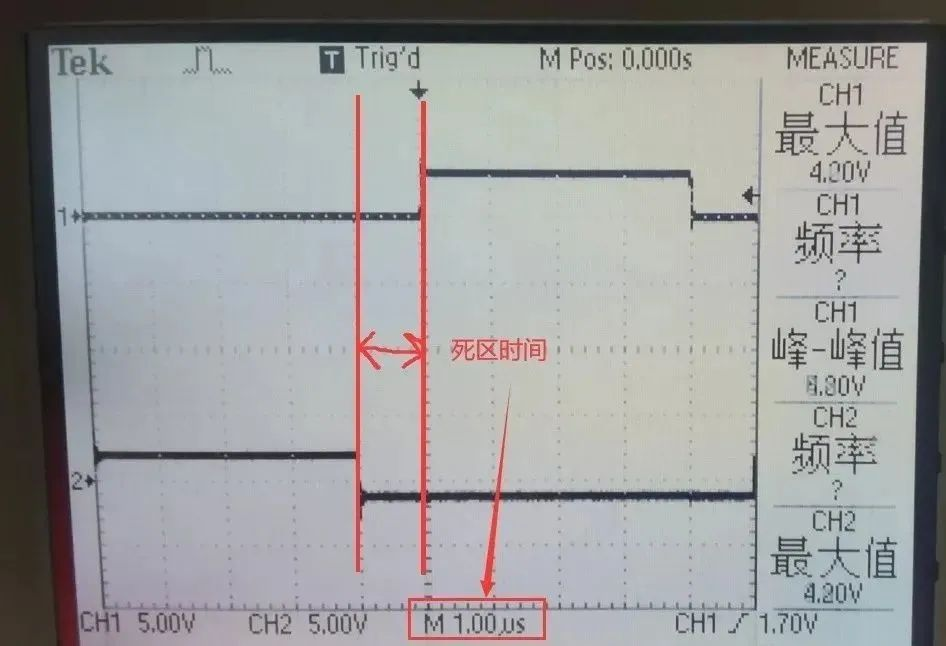

|

| 圖2. 邊界掃描和在線測(cè)試協(xié)同工作,融合了Agilent Technologies的3070在線測(cè)試儀和ASSET InterTech的ScanWorks邊界 - 掃描軟件。由ASSET InterTech提供。 |

但即使邊界掃描設(shè)計(jì)激增,ASSET InterTech的Woppman也看到了ICT硬件的持續(xù)作用。他認(rèn)為ICT制造商已經(jīng)掌握了大批量生產(chǎn)測(cè)試技能,如自動(dòng)化板處理和維修票生成。他認(rèn)為邊界掃描可以增強(qiáng)而不是取代當(dāng)前的ICT戰(zhàn)略,為此,他的公司已經(jīng)調(diào)整了其ScanWorks邊界掃描軟件,以便在安捷倫的3070系列在線測(cè)試儀中無(wú)縫工作(圖2 ”。

安捷倫科技制造測(cè)試部門的產(chǎn)品經(jīng)理巴里·奧德伯特指出,僅靠邊界掃描無(wú)法提供的ICT的一些好處。例如,他引用了無(wú)矢量測(cè)試技術(shù),例如安捷倫的TestJet技術(shù),該技術(shù)測(cè)量DUT金屬引線框架和外部板之間的電容。小于預(yù)期的電容值可能表明焊點(diǎn)不良。例如,如果掃描鏈在圖1中紅色X指示的位置處斷開(kāi),則邊界掃描測(cè)試儀只能告訴您鏈條斷裂,而策略性放置的指甲可以為您物理定位缺陷。

Teradyne的軟件產(chǎn)品經(jīng)理Alan Albee在去年的國(guó)際測(cè)試大會(huì)上引用了ICT和邊界掃描相結(jié)合的幾個(gè)好處(參考文獻(xiàn)7):ICT驅(qū)動(dòng)器/傳感器電路可以測(cè)試非掃描設(shè)備,然后調(diào)節(jié)它們不會(huì)干擾后續(xù)的邊界掃描測(cè)試;結(jié)合ICT和邊界掃描測(cè)試的測(cè)試比單獨(dú)的邊界掃描更能容忍BSDL錯(cuò)誤;和ICT驅(qū)動(dòng)器可以根據(jù)每個(gè)掃描鏈的阻抗特性控制邊界掃描TCK信號(hào)的轉(zhuǎn)換速率和電壓電平,以最大限度地減少反射。 Teradyne通過(guò)其GR TestStation系統(tǒng)和Scan Pathfinder軟件以及Spectrum ICT系統(tǒng)和Victory邊界掃描軟件提供ICT和邊界掃描相結(jié)合。

Albee說(shuō)Teradyne現(xiàn)在正在尋求結(jié)合Scan的功能Pathfinder繼去年收購(gòu)GenRad后,將Victory的功能整合到一個(gè)包中,與Teradyne的產(chǎn)品配合使用,提供集成的原理圖和電路板查看器,測(cè)試訪問(wèn)分析和分布式測(cè)試策略開(kāi)發(fā)。 Albee表示,該公司還計(jì)劃在其Pilot飛針測(cè)試儀中增加標(biāo)準(zhǔn)的邊界掃描功能。他說(shuō),目前,該公司將把Pilot與第三方邊界掃描工具集成在一起。

他說(shuō),該公司不打算做的是與一個(gè)邊界掃描建立獨(dú)家關(guān)系公司:“我們認(rèn)為與獨(dú)立的邊界掃描工具提供商建立關(guān)系很有價(jià)值,但與安捷倫不同,我們認(rèn)為只與一家供應(yīng)商合作符合我們的最佳利益。我們的大多數(shù)客戶已經(jīng)在工作他們?cè)诠こ虒?shí)驗(yàn)室中選擇了邊界掃描工具供應(yīng)商。他們希望使用他們已開(kāi)發(fā)的矢量,并且不想被迫購(gòu)買和學(xué)習(xí)不同的邊界掃描工具。“他說(shuō),Teradyne將與任何邊界掃描工具提供商合作,客戶要求將該公司的工具與其ICT系統(tǒng)集成。

從邊界掃描方面來(lái)看,Corelis的Blasberg對(duì)此表示贊同。與邊界掃描工具供應(yīng)商建立獨(dú)家關(guān)系的ICT供應(yīng)商如果試圖將這些客戶鎖定在針對(duì)特定客戶應(yīng)用程序的可能不是最佳的邊界掃描解決方案中,則會(huì)損害其自身和客戶。 Acculogic的Taheri表示,ICT供應(yīng)商不應(yīng)該與邊界掃描公司進(jìn)行一對(duì)一但一對(duì)多的合作努力,反之亦然。但緊密集成是一個(gè)關(guān)鍵,所有觀察者都認(rèn)同,以及可接受的整合水平是否需要排他性關(guān)系仍然存在爭(zhēng)議。

沒(méi)有人建議在線路測(cè)試儀旁邊加一個(gè)邊界掃描控制器并嘗試同時(shí)應(yīng)用單獨(dú)開(kāi)發(fā)的邊界掃描和在線測(cè)試程序。一個(gè)原因是這種方法會(huì)使測(cè)試開(kāi)發(fā)工作變得非常復(fù)雜 - 您將面臨兩個(gè)開(kāi)發(fā)任務(wù)而不是一個(gè)開(kāi)發(fā)任務(wù)。此外,您無(wú)法知道您的兩個(gè)測(cè)試程序是否提供完整的故障覆蓋,或者您是否浪費(fèi)寶貴的生產(chǎn)測(cè)試時(shí)間來(lái)尋找兩種測(cè)試方法相同的故障。

最后,Odbert指出,你可能會(huì)損壞被測(cè)電路板。這種損害可能是由于ICT與邊界掃描測(cè)試硬件電源之間的隔離問(wèn)題,或者是邊界掃描和ICT系統(tǒng)在一個(gè)節(jié)點(diǎn)上同時(shí)斷言相互沖突的邏輯信號(hào)電平所造成的。 Woppman說(shuō),協(xié)調(diào)的方法通過(guò)在邊界掃描測(cè)試期間將未使用的釘子驅(qū)動(dòng)到高阻抗?fàn)顟B(tài)來(lái)消除這個(gè)問(wèn)題。

盡管邊界掃描和ICT可以為測(cè)試家務(wù)帶來(lái)協(xié)同作用,但這種組合并不適用于所有應(yīng)用。 Woppman表示,對(duì)于小批量生產(chǎn),可能需要一個(gè)專門的邊界掃描測(cè)試儀,可能還有一個(gè)飛行探測(cè)器來(lái)測(cè)試電阻器和其他非掃描部件。 Odbert表示同意,邊界掃描測(cè)試加上一個(gè)簡(jiǎn)單的制造缺陷分析儀可能足以滿足消費(fèi)產(chǎn)品的大批量,低成本PCB,而ICT可能對(duì)于價(jià)值數(shù)千美元的網(wǎng)卡仍然最有效。 “我們不知道未來(lái)會(huì)怎樣,”Woppman總結(jié)說(shuō),成功的測(cè)試公司將提供靈活的硬件和軟件組合,您可以從中選擇。

-

邊界掃描

+關(guān)注

關(guān)注

1文章

32瀏覽量

14993 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

42795

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

盤(pán)點(diǎn)一下那些年你見(jiàn)過(guò)卻不了解的PCB天線

在Traveo T2G CYT2B73BADQ0AZSGS上運(yùn)行JTAG邊界掃描,為什么無(wú)法從設(shè)備的JTAG端口獲得任何響應(yīng)?

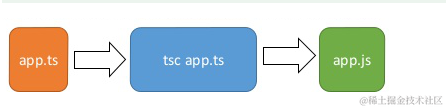

鴻蒙TypeScript入門學(xué)習(xí)第2天【TypeScript安裝】

分享一個(gè)調(diào)測(cè)電量計(jì)過(guò)程中發(fā)現(xiàn)的電阻問(wèn)題

邊界矢量數(shù)據(jù)是什么格式

關(guān)于JTAG口,你了解多少?

掃碼讀頭有哪些?嵌入自助設(shè)備專用的二維碼掃描器你知道嗎?

掃描電鏡的原理、優(yōu)勢(shì)、應(yīng)用領(lǐng)域你都知道嗎?

內(nèi)存尋址的具體設(shè)計(jì)

馬上2024年了你還不了解智慧燈桿嗎

你了解掃描電鏡的特點(diǎn)和結(jié)構(gòu)嗎

不了解EMC,怎么畫(huà)PCB?

你了不了解邊界掃描

你了不了解邊界掃描

評(píng)論