為了解決輸入信號之間的約束問題,避免輸入端r、s出現全1的情況,可將電路改進為主從型jk觸發器,簡稱為jk觸發器。

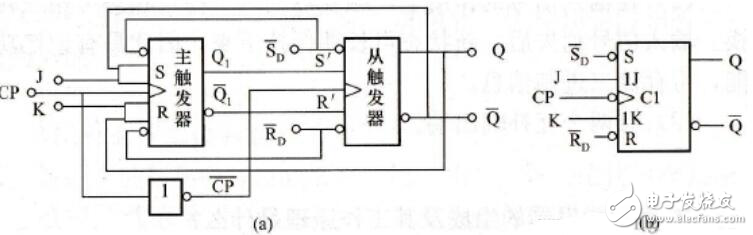

(1)電路結構。jk觸發器的邏輯圖,如圖(a)所示。由圖可見,是將主從rs觸發器和q端的狀態引回到兩個輸入端,形成jk觸發器的信號輸入端,分別稱為j端和k端。jk觸發器的邏輯符號,如圖(b)所示。

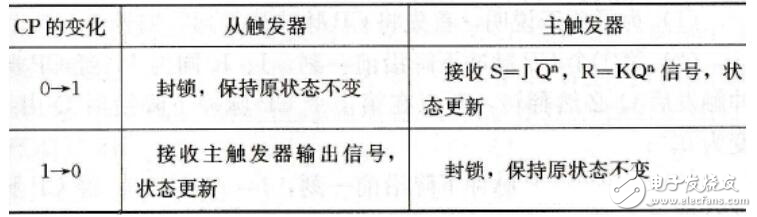

(2)工作原理。由邏輯圖分析,jk觸發器的觸發特點,可用表1說明。表1主從jk觸發器觸發特點:

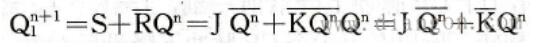

可見,主從式jk觸發器也是cp的下降沿觸發。根據jk觸發器的觸發特點,可知:當cp=1時,主觸發器工作,有:

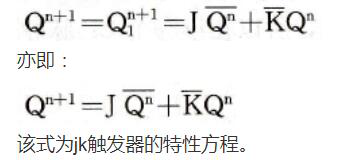

當cp=0時,從觸發器打開,則有:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

JK觸發器

+關注

關注

1文章

43瀏覽量

15875 -

觸發器

+關注

關注

14文章

1995瀏覽量

61049

發布評論請先 登錄

相關推薦

JK觸發器的原理和功能

JK觸發器,也被稱為通用可編程觸發器,是數字電路中的一種重要且功能強大的基本存儲器件。其名稱源自其兩個輸入端口J(置位)和K(復位),以及一個關鍵的控制端——時鐘信號控制端(CP)。JK

jk觸發器的功能有哪些

JK觸發器是一種具有兩個穩定狀態的雙穩態電路,廣泛應用于數字電路設計中。本文將詳細介紹JK觸發器的功能、工作原理、邏輯特性、應用場景以及與其

jk觸發器和t觸發器的工作原理、特點和應用

JK觸發器和T觸發器都是數字電路中常用的觸發器,它們在存儲和傳遞信息方面發揮著重要作用。然而,它們在功能和應用上存在一定的差異。 一、JK

主從jk觸發器和邊沿jk觸發器的區別

主從JK觸發器和邊沿JK觸發器是數字電路中常用的存儲元件,它們在功能和應用上既有相似之處,也存在顯著的區別。以下將從多個方面介紹這兩種

主從觸發器和同步觸發器的區別在哪里

Trigger)。主觸發器負責接收輸入信號,從觸發器負責輸出信號。同步觸發器(Synchronous Trigger)是一種觸發器結構,它在每個時鐘周期內對輸入信號進行采樣,并在時鐘

主從觸發器都是下降沿觸發嗎

主從觸發器(Master-Slave Flip-Flop)是一種常見的數字邏輯電路,用于存儲一位二進制信息。主從觸發器通常由兩個觸發器組成,一個作為主觸發器,另一個作為從

JK觸發器概述及工作原理

JK觸發器,也被稱為通用可編程觸發器,是數字電路中的一種基本存儲器件。它得名于其輸入端口J(置位)和K(復位),以及一個時鐘控制端。JK觸發器

jk觸發器上升沿和下降沿怎么判斷

是一種具有兩個穩定狀態的觸發器,它可以通過輸入信號的變化來改變其輸出狀態。JK觸發器的特點是具有兩個輸入端,分別標記為J和K,以及一個輸出端,標記為Q。JK

如何用jk觸發器構成t觸發器?t觸發器邏輯功能有哪些

如何用JK觸發器構成T觸發器 JK觸發器是一種基本的觸發器電路,由兩個輸入端J和K控制,以及兩個

t觸發器和jk觸發器的區別和聯系

穩態觸發器,具有一個觸發輸入(T輸入)和一個時鐘輸入,以及一個輸出。T觸發器的輸出狀態取決于其當前狀態、觸發輸入和時鐘輸入。 工作原理 T

主從jk觸發器工作原理

主從jk觸發器工作原理

評論