隨著智能安全、機器人或無人駕駛汽車等應(yīng)用越來越依靠嵌入式人工智能技術(shù)來提高性能,交付全新的用戶體驗,傳統(tǒng)計算平臺上的推斷引擎很難在有限的功耗、時延和物理尺寸限制下滿足實際要求。推斷引擎必須滿足嚴格定義的推斷精度,還受限于總線寬度,而且存儲器難以為最佳速度、效率和芯片面積進行調(diào)整優(yōu)化。我們需要靈活應(yīng)變的計算平臺來滿足運行一流卷積神經(jīng)網(wǎng)絡(luò) (CNN) 的嵌入式 AI 的要求。

放眼未來,適應(yīng)于更多前沿神經(jīng)網(wǎng)絡(luò)的靈活性是我們的主要關(guān)注點。今天廣受歡迎的 CNN 正加速被新型的先進架構(gòu)所取代。然而,傳統(tǒng)的 SoC 設(shè)計要使用當前的神經(jīng)網(wǎng)絡(luò)架構(gòu)知識,從開發(fā)開始到未來部署通常需要大約三年時間。RNN 或 Capsule Network 等新型神經(jīng)網(wǎng)絡(luò)可能會讓傳統(tǒng) SoC 變得低效,也難以提供保持競爭力所需的性能。

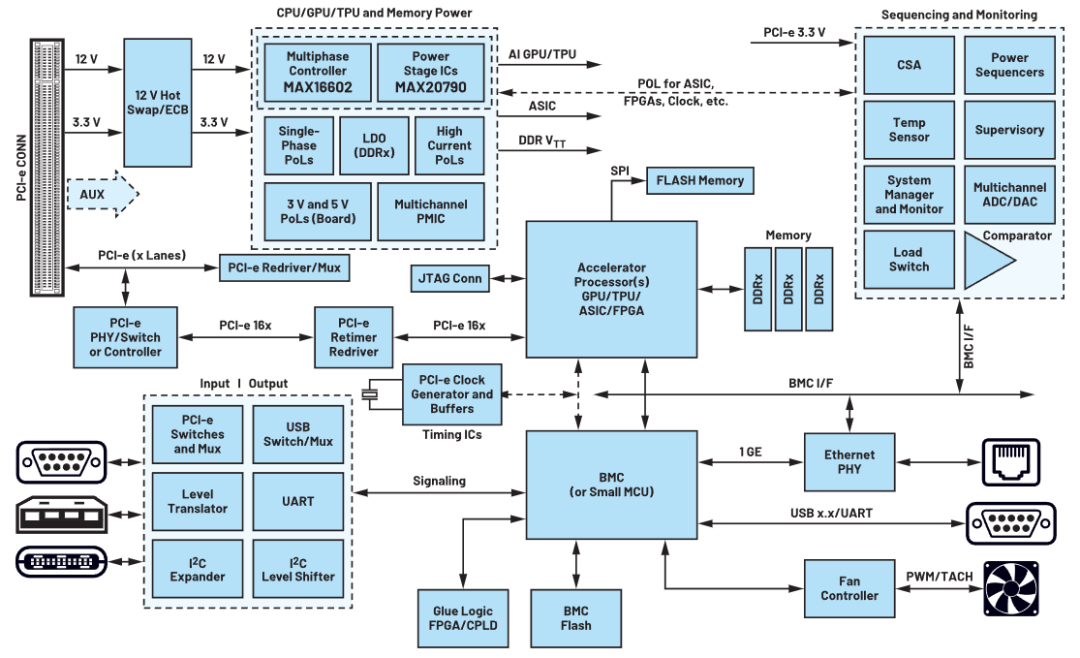

嵌入式 AI 要滿足最終用戶期望,特別是要跟上可預(yù)見的未來不斷提升的需求,就必須采用更加靈活的自適應(yīng)計算平臺。我們可利用用戶可配置的多核片上系統(tǒng) (MPSoC) 器件,整合主應(yīng)用處理器和可擴展的可編程邏輯結(jié)構(gòu),包含可配置的存儲器架構(gòu)和滿足可變精度推斷所需的信號處理技術(shù),從而滿足上述要求。

推斷精度

在傳統(tǒng)的 SoC 中,決定性能的特性如存儲器架構(gòu)和計算精確度等是固定的。最小值通常為 8 位,由核心 CPU 定義,不過就給定的算法而言最佳精度可能更低。MPSoC 支持可編程邏輯優(yōu)化至晶體管層面,這就能根據(jù)需要讓推斷精度降低到 1 位。此外,這類器件還包含成千上萬可配置的 DSP slice,能高效處理乘積累加 (MAC) 計算。

能自由優(yōu)化推斷精度,根據(jù)平方律提供剛好滿足需求的計算效率,也就是說單位的運算用 1 位核心執(zhí)行,相對于用 8 位核心完成相同計算而言,所需的邏輯僅為 1/64。此外,MPSoC 能讓推斷精度針對神經(jīng)網(wǎng)絡(luò)的每層做出不同優(yōu)化,從而以最大的效率提供所需的性能。

存儲器架構(gòu)

除了通過改變推斷精度來提高計算效率之外,配置可編程片上存儲器的帶寬和結(jié)構(gòu)能進一步提高嵌入式 AI 的性能和效率。定制 MPSoC 相對于運行相同推斷引擎的傳統(tǒng)計算平臺而言,片上存儲器可能達到 4 倍多,存儲器—接口帶寬可能達到 6 倍。存儲器的可配置性使得用戶能減少瓶頸,并優(yōu)化芯片資源的利用率。此外,典型的子系統(tǒng)只有有限的片上集成高速緩存,必須與片外存儲設(shè)備頻繁交互,這就會增加時延和功耗。在 MPSoC 中,大多數(shù)存儲器交換都在片上進行,這就會大幅提高速度,而且相對于片外存儲器交互而言功耗降低超過 99%。

芯片面積

解決方案的尺寸也越來越重要,特別就采用移動 AI 的無人機、機器人或無人/自動駕駛汽車而言尤其如此。MPSoC 的 FPGA 結(jié)構(gòu)上實現(xiàn)的推斷引擎可能僅占用傳統(tǒng) SoC 八分之一的芯片面積,這就能讓開發(fā)人員在更小的器件中構(gòu)建功能更強大的引擎。

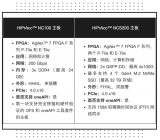

此外,MPSoC 器件系列為設(shè)計人員提供了實現(xiàn)推斷引擎的豐富選擇,能支持最節(jié)能、成本效率最高、面積占用最小的方案,從而滿足系統(tǒng)性能要求。一些通過汽車應(yīng)用認證的部件具備硬件功能安全特性,達到業(yè)界標準的 ISO 26262 ASIL-C 安全規(guī)范,這對自動駕駛應(yīng)用而言至關(guān)重要。比如賽靈思的 Automotive XA Zynq UltraScale+ 系列采用 64 位四核 ARM Cortex-A53 和雙核 ARM Cortex-R5 處理系統(tǒng)以及可擴展的可編程邏輯結(jié)構(gòu),這就能在單個芯片上整合控制處理、機器學(xué)習(xí)算法和安全電路,同時提供故障容錯功能。

今天,嵌入式推斷引擎可用單個 MPSoC 器件實現(xiàn),功耗低至 2 瓦,這對移動機器人或自動駕駛汽車而言都是比較合適的功耗水平。傳統(tǒng)計算平臺即便現(xiàn)在也無法用這么低的功耗運行實時 CNN 應(yīng)用,未來也不太可能在更嚴格的功耗限制條件下滿足更快響應(yīng)和更復(fù)雜功能的日益嚴格的要求。基于可編程 MPSoC 的平臺能夠提供更高的計算性能,更高的效率,也能在 15瓦以上的功率水平下減小面積和減輕重量。

如果開發(fā)人員不能在自己的項目中輕松地實現(xiàn)這些優(yōu)勢,那么這種可配置型多平行計算架構(gòu)的優(yōu)勢就僅限于學(xué)術(shù)領(lǐng)域。成功需要適當?shù)墓ぞ邅韼椭_發(fā)人員優(yōu)化目標推斷引擎的實現(xiàn)。為了滿足有關(guān)需求,賽靈思不斷擴展開發(fā)工具生態(tài)系統(tǒng)和機器學(xué)習(xí)軟件堆棧,并與專業(yè)合作伙伴合作,一起簡化和加速計算機視覺和視頻監(jiān)控等應(yīng)用的實現(xiàn)。

面向未來的靈活性

利用 SoC 的可配置性為手頭應(yīng)用創(chuàng)建最佳平臺,也使得 AI 開發(fā)人員能夠靈活地跟上神經(jīng)網(wǎng)絡(luò)架構(gòu)快速發(fā)展演進的要求。業(yè)界可能遷移到新型神經(jīng)網(wǎng)絡(luò)的可能性,對于平臺開發(fā)人員來說是一個巨大的風(fēng)險。可重配置的 MPSoC 通過重配置并用當前最先進的策略來構(gòu)建最高效的處理引擎,能夠讓開發(fā)人員靈活地響應(yīng)神經(jīng)網(wǎng)絡(luò)架構(gòu)方式的變化。

AI 越來越多地嵌入到各種設(shè)備中,包括工業(yè)控制、醫(yī)療設(shè)備、安全系統(tǒng)、機器人和自動駕駛汽車等。利用可編程邏輯結(jié)構(gòu)的 MPSoC 器件的靈活應(yīng)變加速技術(shù),是提供保持競爭力所需的快速響應(yīng)和高級功能的關(guān)鍵。

-

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131164 -

AI

+關(guān)注

關(guān)注

87文章

30136瀏覽量

268411

原文標題:靈活應(yīng)變的加速是將人工智能從云端帶到邊緣的關(guān)鍵

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

66AK2Hx片上系統(tǒng)(SoC)器件系列的功耗摘要

嚴格的性能測試確保連接器可滿足復(fù)雜環(huán)境的應(yīng)用需求

FPGA基礎(chǔ)知識學(xué)習(xí)

risc-v多核芯片在AI方面的應(yīng)用

片上系統(tǒng)代表芯片嗎

什么是可編程片上系統(tǒng)?PSOC和FPGA的區(qū)別

可編程片上系統(tǒng)是什么

片上系統(tǒng)的組成

片上系統(tǒng)是什么意思

Hitek Systems開發(fā)基于PCIe的高性能加速器以滿足行業(yè)需求

TPS650864可配置多軌PMU適用于多核處理器、FPGA和系統(tǒng)的TPS650861可配置多軌PMU數(shù)據(jù)表

臺積電大幅上調(diào)SoIC產(chǎn)能規(guī)劃,以滿足未來AI、HPC的強勁需求

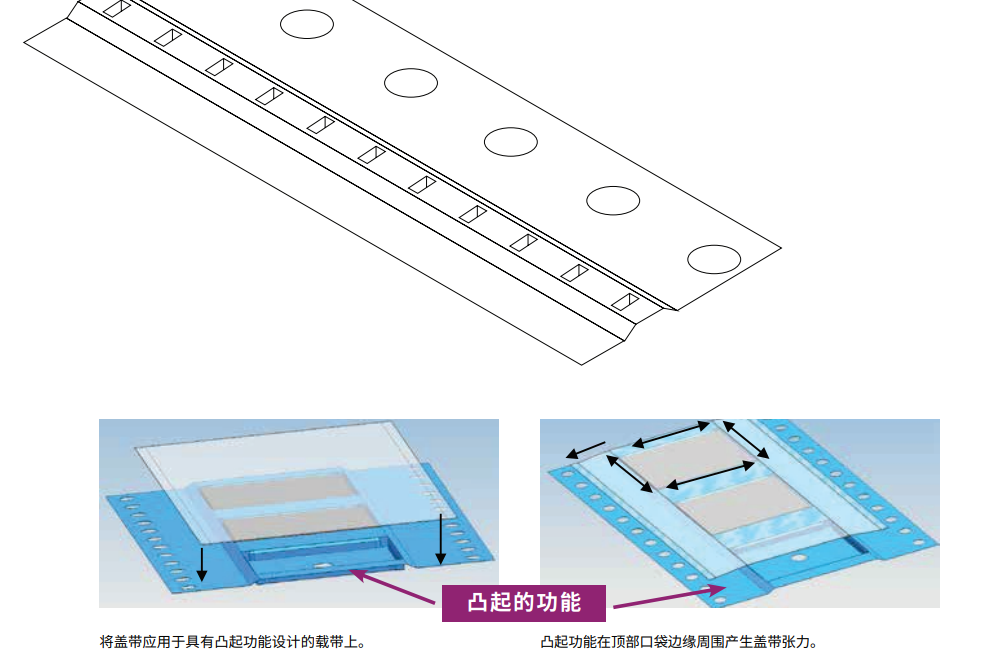

滿足特殊要求的定制化載帶設(shè)計

AI新興應(yīng)用通過帶可配置加速的片上系統(tǒng)器件來滿足嚴格性能、效率需求

AI新興應(yīng)用通過帶可配置加速的片上系統(tǒng)器件來滿足嚴格性能、效率需求

評論