概念:

Power/Ground Gating是集成電路中通過關(guān)掉那些不使用的模塊的電源或者地來降低電路漏電功耗的低功耗設(shè)計方法。該方法能降低電路在空閑狀態(tài)下的靜態(tài)功耗,還能測試Iddq。

理論:

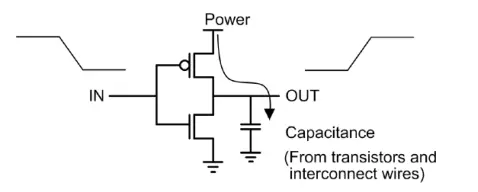

在電路中的某些模塊進(jìn)入休眠或者空閑模式時,我們可以使用之前講過的Clock Gating技術(shù)來降低它們的動態(tài)功耗,但是無法降低它們的靜態(tài)功耗。而Power/Ground Gating技術(shù)可以在它們休眠的時候完全關(guān)掉它們的電源從而消除它們的靜態(tài)功耗。

理想情況下,Power gating可以完全消除電路的靜態(tài)功耗,可實際電路中Power gating只能完全關(guān)掉dynamic的power消耗,而leakage卻只會減少,不會消失,因為power gating技術(shù)仍需要加入一些Always On的Cell(比如switching cell、isolate cell和retention cell,它們都是一直開啟的,它們的電源不能被關(guān)斷,會帶來leakage)。

如下圖所示為采用了Power gating的電路動態(tài)功耗與靜態(tài)功耗在active模式以及sleep模式下功耗的變化曲線。

Power gating中用到的幾種Cell

接下來將對幾種Cell分別介紹。

由于內(nèi)容非常多,非常詳細(xì),所以本推文先介紹第一個--Power Switching Cell。

Power Switching Cell

Power Gating或者Ground Gating相應(yīng)Switching Cell的選取:

Power Gating -> Header -> PMOS

Ground Gating -> Footer -> NMOS

由于Power Switching Cell是Always On Cell,因此為了降低它上面的功耗,一般采用高閾值MOS管實現(xiàn)。下面的圖中MOS管上面黑線加粗表示高閾值器件。

下面給出兩種方案各自的特點,優(yōu)缺點以及兩種門控方案在SLEEP模式下哪種功耗更低。

下圖是Power Gating方案:

特點:

用PMOS實現(xiàn)的Header,用來控制電源的接通與否。

優(yōu)點:

比Footer實現(xiàn)的Ground Gating功耗更低,因為Header下方的PMOS(在實際電路中會有很多)體端接Virtual VDD,在SLEEP模式下約為0V,不存在PN節(jié)反偏注入電流。

缺點:

PMOS驅(qū)動能力弱,與Footer相比需要占用更大的面積。

注意:該缺點在先進(jìn)工藝下已經(jīng)不存在,由于鍺硅工藝的引入,PMOS可能比NMOS驅(qū)動還要強(qiáng)一些。由于該缺點已經(jīng)不存在,因此先進(jìn)工藝下更多采用Header,也就是Power Gating。

Ground Gating方案:

特點:

用NMOS實現(xiàn)的Footer,用來控制GND的接通與否。

優(yōu)點:

在之前的老工藝中,相同尺寸的NMOS驅(qū)動能力比PMOS要強(qiáng),因此與Header相比采用Footer的Ground Gating更省面積。

但是在先進(jìn)工藝中,該優(yōu)點也逐漸喪失了,原因前面已經(jīng)解釋過了。

缺點:

在SLEEP模式下,漏電功耗比較大。

因為如下:Footer上方的NMOS(在實際電路中會有很多)體端是P襯底,在單阱工藝下只能接GND,在SLEEP模式下NMOS源漏兩端的電位都差不多是VDD,此時NMOS存在很大的PN節(jié)反偏注入電流。

Power Switching Cell的啟動與關(guān)閉

Power Switching Cell的個數(shù)、分布以及啟動、關(guān)閉上都有講究。

這對IR-drop、Timing、漏電流、啟動及關(guān)閉的速度等都有影響。

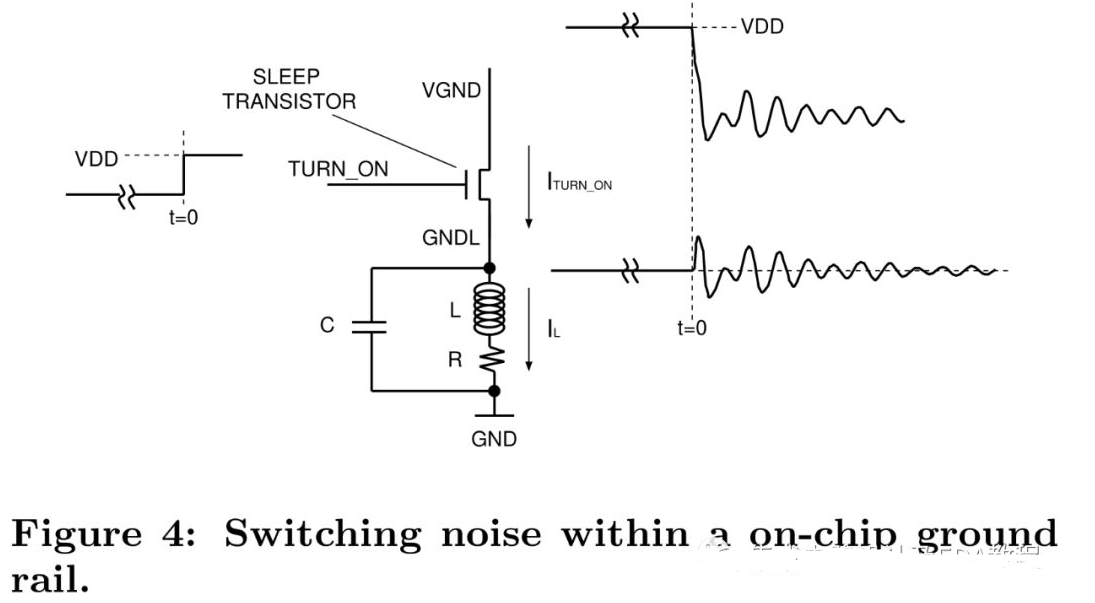

另外,所有的Header或者Footer也不能同時一起打開或者關(guān)閉,因為這樣在電源或者地上會有很大的開關(guān)噪聲,如下圖所示:

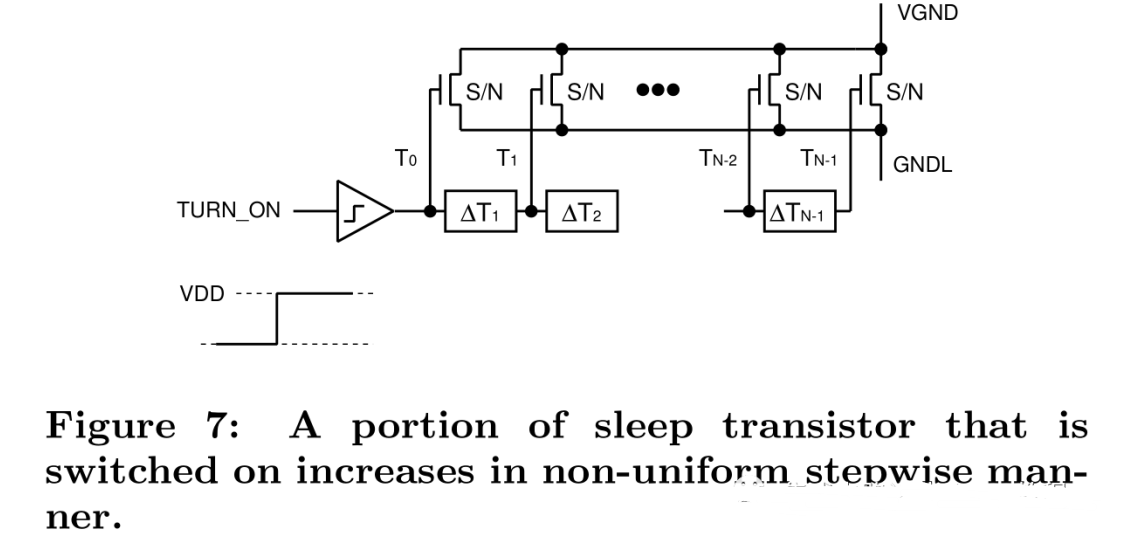

為了避免這種現(xiàn)象,目前的集成電路設(shè)計中廣泛采用如下圖所示的Daisy Chain結(jié)構(gòu),多個Footer或者Header之間插入Buffer,每隔一段時間開啟/關(guān)閉一組,再隔一段時間開啟/關(guān)閉另外一組……直到最后所有的Switching Cell開啟/關(guān)閉為止。

Power Switching Cell的種類與分布

前面我們根據(jù)Power或者Ground Gating來將Switching Cell分為兩種:Header和Footer。

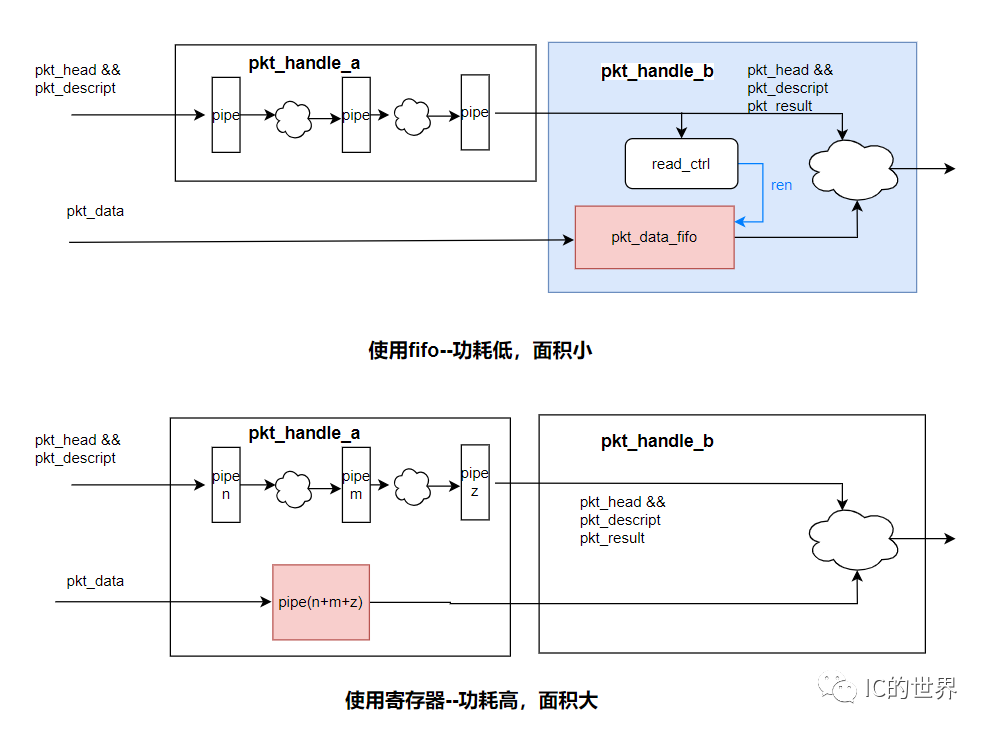

另外,我們還可以根據(jù)Switching Cell控制Cell的形式將它分為兩種:Coarse Grain Power Switch Cell和Fine Grain Power Switch Cell。

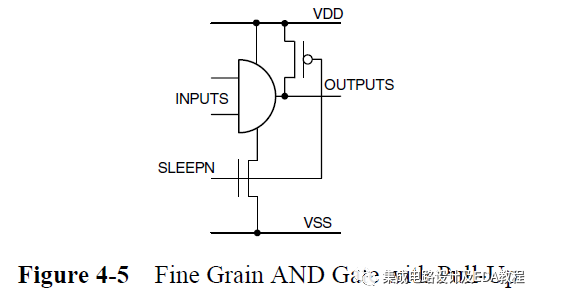

后者是專門在一些邏輯單元內(nèi)設(shè)計的電源控制邏輯,控制簡單,但是面積比較大,如下圖所示:

而前者是分立的Switching Cell,可以在版圖中控制它們的分布,設(shè)計復(fù)雜度大一點,但是面積開銷比較小,現(xiàn)在廣泛采用這種形式。

根據(jù)前面講述的內(nèi)容,Power Switching Cell在物理版圖中的分布有一定的要求。

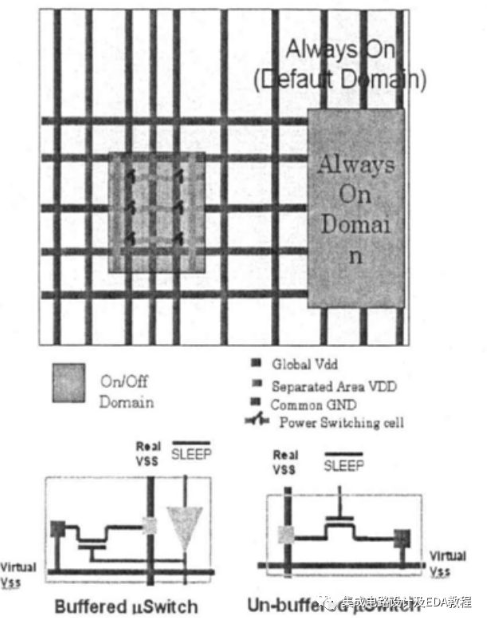

有列狀分布:

還有環(huán)狀分布:

考慮到前面講的Daisy Chain結(jié)構(gòu)以及IR-drop等因素,目前廣泛采用列狀排布。

Power Switching Cell的lib描述

前面講到,Power Switching Cell有兩種,分別為Coarse Grain Power Switch Cell和Fine Grain Power Switch Cell。

下面是一個Coarse Grain Power Switch Cell的Liberty格式描述:

library(《coarse_grain_library_name》) { #library 描述開始

…

lu_table _template ( template_name ) #電壓狀態(tài)template描述,dc_current組中會使用

variable_1 : input_voltage;

variable_2 : output_voltage;

index_1 ( 《float》, … );

index_2 ( 《float》, … );

}

…

cell(《cell_name》) { #某個Power Switching Cell描述開始

switch_cell_type : coarse_grain; #Switching Cell類型是coarse_grain,暫時只支持該類型

…

pg_pin ( 《VDD/VSS pin name》 ) { #聲明電源和地的pg_pin格式

pg_type : primary_power | primary_ground; #他們是主電源和主地

direction : input ; #方向是輸入

…

}

/* Virtual power and ground pins use “switch_function” to describe the logic to

shut off the attached design partition */

pg_pin ( 《virtual VDD/VSS pin name》) { #聲明內(nèi)部電源和地,這就是輸出電源/地的端口

pg_type : internal_power | internal_ground;

direction: output; #方向是輸出

…

switch_function : “《function_string》”; #定義開斷控制功能,例如SLEEP

pg_function : “《function_string》”; #內(nèi)部電源或地功能與輸入的pg_pin一致,對于header switch來說就是premary_power的Pin Name,對于Footer Switch來說就是primary_ground的Pin Name

}

dc_current ( 《dc_current_name》 ) { #定義不同條件下輸出Pin的穩(wěn)定電流值,EDA工具利用該數(shù)據(jù)計算IR Drop,并進(jìn)行Switch的優(yōu)化。

related_switch_pin : 《input_pin_name》; #定義控制開斷的Pin

related_pg_pin : 《VDD pin name》; #定義可以被控制開斷的電源Pin,如果是Footer Switch則是地Pin

related_internal_pg_pin : 《Virtual VDD》; #定義不會被關(guān)閉的內(nèi)部電源Pin,F(xiàn)ooter Switch則是地Pin

values(”《float》, …”); #定義不同狀態(tài)下的該Cell輸出的電流值

}

pin (SLEEP) { #Pin SLEEP定義開始,SLEEP只是舉例

direction : input;

switch_pin : true; #表示該輸入Pin是switch pin,控制電源/地的開斷

…

/* The acknowledge output pin uses “function” to represent the propagated switching signal

*/

pin(《acknowledge_output_pin_name》) { #定義應(yīng)答輸出Pin開始,完成開斷后,與switch pin狀態(tài)一致,有的Switch Cell可能沒有該pin

…

function : “《function_string》”; #功能定義,應(yīng)該與SLEEP狀態(tài)一致

power_down_function : “function_string”; #定義關(guān)斷后電源狀態(tài),如對于Header switch來說可以是!VDD+VSS,而Footer Switch來說可以是!VSS+VDD

direction : output;

…

} /* end pin group */

} /* end cell group */

Fine Grain Power Switch Cell的Liberty格式描述:

cell(《cell_name》) { #Fine Grain Power Switch Cell都是某個Cell內(nèi)的一部分,不單獨(dú)出現(xiàn)

is_macro_cell : true; #定義是不是macro cell

switch_cell_type : coarse_grain | fine_grain; #多數(shù)設(shè)置為fine_grain

pg_pin ( 《power/ground pin name》 ) { #定義電源信號,primary_是可以斷開的,backup_是不會斷開的。

pg_type : primary_power | primary_ground | backup_power | backup_ground;

direction: input | inout | output;

…

}

/* This is a special pg pin that uses “switch_function” to describe the logic to shut

off the attached design partition */

pg_pin ( 《internal power/ground pin name》) { #定義內(nèi)部電源/地

direction: internal | input | output | inout;

pg_type : internal_power | internal_ground;

switch_function : “《function_string》”;

pg_function : “《function_string》”;

…

}

pin (《input_pin_name》) {

direction : input | inout;

switch_pin : true | false; #如果是switch pin就是true

…

}

…

pin(《output_pin_name》) {s

direction : output | inout;

power_down_function : 《function_string》;

…

} /* end pin group */

} /* end cell group */

-

集成電路

+關(guān)注

關(guān)注

5381文章

11382瀏覽量

360850 -

靜態(tài)功耗

+關(guān)注

關(guān)注

0文章

17瀏覽量

8927 -

PMOS

+關(guān)注

關(guān)注

4文章

244瀏覽量

29488 -

低功耗設(shè)計

+關(guān)注

關(guān)注

0文章

80瀏覽量

16146

發(fā)布評論請先 登錄

相關(guān)推薦

低功耗SOC芯片的優(yōu)勢

物聯(lián)網(wǎng)系統(tǒng)中TCP低功耗產(chǎn)品長連接狀態(tài)下降低功耗功能的實現(xiàn)方案

柵極驅(qū)動芯片選型低功耗原因

一款4644芯片低功耗設(shè)計思路解析

OPA454如何降低功耗?

有沒有降低ESp8266功耗的方法?

上拉電阻如何實現(xiàn)低功耗設(shè)計

OTP低功耗語音芯片的工作原理與產(chǎn)品特性

降低電路漏電功耗的低功耗設(shè)計方法

降低電路漏電功耗的低功耗設(shè)計方法

評論