下面是一些基本的數字電路知識問題,請簡要回答之。

(1) 什么是 Setup和 Hold 時間?

答:Setup/Hold Time 用于測試芯片對輸入信號和時鐘信號之間的時間要求。建立時間 (Setup Time)是指觸發器的時鐘信號上升沿到來以前,數據能夠保持穩 定不變的時間。輸入數據信號應提前時鐘上升沿 (如上升沿有效)T 時間到達芯片,這個 T就是建立時間通常所說的 SetupTime。如不滿足 Setup Time,這個數據就不能被這一時鐘打入觸發器,只有在下一個時鐘上升沿到來時,數據才能被打入 觸發器。保持時間(Hold Time)是指觸發器的時鐘信號上升沿到來以后,數據保持穩定不變的時間。如果 Hold Time 不夠,數據同樣不能被打入觸發器。

(2) 什么是競爭與冒險現象?怎樣判斷?如何消除?

答:在組合邏輯電路中,由于門電路的輸入信號經過的通路不盡相同,所產生的延時也就會不同,從而導致到達該門的時間不一致,我們把這種現象叫做競爭。由于競爭而在電路輸出端可能產生尖峰脈沖或毛刺的現象叫冒險。如果布爾式中有相反的信號則可能產生競爭和冒險現象。解決方法:一是添加布爾式的消去項,二是在芯片外部加電容。

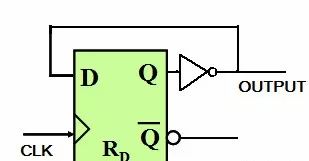

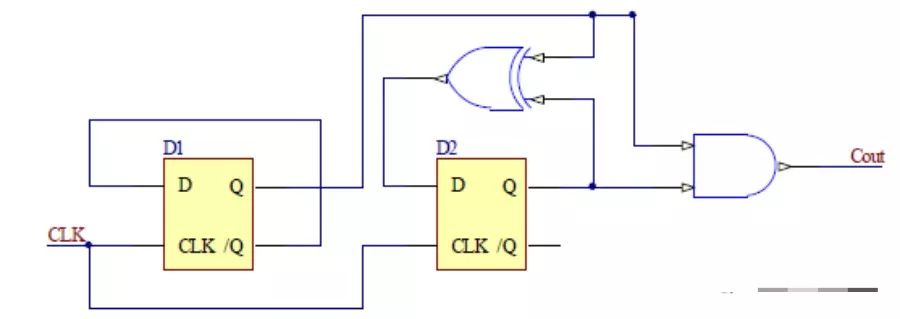

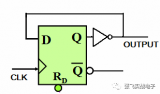

(3) 請畫出用 D 觸發器實現 2 倍分頻的邏輯電路

答:把 D 觸發器的輸出端加非門接到 D 端即可,如下圖所示:

(4) 什么是"線與 "邏輯,要實現它,在硬件特性上有什么具體要求?

答:線與邏輯是兩個或多個輸出信號相連可以實現與的功能。在硬件上,要用 OC 門來實現( 漏極或者集電極開路 ),為了防止因灌電流過大而燒壞 OC 門, 應在 OC 門輸出端接一上拉電阻 (線或則是下拉電阻)。

(5) 什么是同步邏輯和異步邏輯?同步電路與異步電路有何區別?

答:同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系 .電路設計可分類為同步電路設計和異步電路設計。同步電路利用時鐘脈沖使其子系統同步運作 ,而異步電路不使用時鐘脈沖做同步,其子系統是使用特殊的 “開始”和“完成”信號使之同步。異步電路具有下列優點:無時鐘歪斜問題、 低電源消耗、平均效能而非最差效能、模塊性、可組合和可復用性。

(6) 你知道那些常用邏輯電平?TTL 與 COMS 電平可以直接互連嗎?

答:常用的電平標準,低速的有 RS232、RS485 、RS422、 TTL、CMOS 、LVTTL、 LVCMOS、ECL 、ECL、 LVPECL 等,高速的有 LVDS、 GTL、PGTL 、 CML、 HSTL、SSTL 等。

一般說來, CMOS 電平比 TTL 電平有著更高的噪聲容限。如果不考慮速度 和性能,一般 TTL 與 CMOS 器件可以互換。但是需要注意有時候負載效應可能引起電路工作不正常,因為有些 TTL 電路需要下一級的輸入阻抗作為負載才能 正常工作。

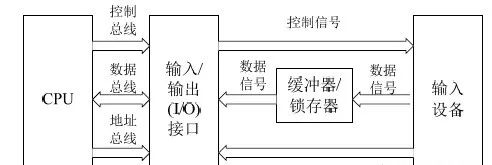

(7) 請畫出微機接口電路中,典型的輸入設備與微機接口邏輯示意圖 (數據接口、控制接口、鎖存器 /緩沖器)

典型輸入設備與微機接口的邏輯示意圖如下:

2你所知道的可編程邏輯器件有哪些?

答:ROM(只讀存儲器)、 PLA(可編程邏輯陣列)、 FPLA(現場可編程邏輯陣列)、 PAL(可編程陣列邏輯)GAL(通用陣列邏輯 ),EPLD( 可擦除的可編程邏輯器件 )、 FPGA( 現場可編程門陣列 )、CPLD( 復雜可編程邏輯器件 )等 ,其中 ROM、 FPLA、 PAL 、GAL、 EPLD 是出現較早的可編程邏輯器件, 而 FPGA 和 CPLD 是當今最流行的兩類可編程邏輯器件。FPGA 是基于查找表結構的,而 CPLD 是基于乘積項結構的。

3用 VHDL 或 VERILOG、ABLE 描述 8 位 D 觸發器邏輯

4請簡述用 EDA 軟件 (如 PROTEL)進行設計 (包括原理圖和PCB圖) 到調試出樣機的整個過程,在各環節應注意哪些問題?

答:完成一個電子電路設計方案的整個過程大致可分:

(1)原理圖設計

(2)PCB 設計

(3)投板

(4)元器件焊接

(5)模塊化調試

(6)整機調試 。

注意問題如下:

(1)原理圖設計階段

注意適當加入旁路電容與去耦電容;

注意適當加入測試點和 0 歐電阻以方便調試時測試用;

注意適當加入 0 歐電阻、電感和磁珠(專用于抑制 信號線、電源線上的高頻噪聲和尖峰干擾)以實現抗干擾和阻抗匹配;

(2)PCB 設計階段

自己設計的元器件封裝要特別注意以防止板打出來后元器件無法焊接;

FM部分走線要盡量短而粗,電源和地線也要盡可能粗;

旁路電容、晶振要盡量靠近芯片對應管腳;

注意美觀與使用方便;

(3)投板

說明自己需要的工藝以及對制板的要求;

(4)元器件焊接

防止出現芯片焊錯位置,管腳不對應;

防止出現虛焊、漏焊、搭焊等;

(5)模塊化調試

先調試電源模塊,然后調試控制模塊,然后再調試其它模塊;

上電時動作要迅速,發現不會出現短路時在徹底接通電源;

調試一個模塊時適當隔離其它模塊 ;

各模塊的技術指標一定要大于客戶的要求;

(6)整機調試

如提高靈敏度等問題

5基爾霍夫定理

KCL:電路中的任意節點,任意時刻流入該節點的電流等于流出該節的電流( KVL同理)

6描述反饋電路的概念,列舉他們的應用

反饋是將放大器輸出信號 (電壓或電流)的一部分或全部,回收到放大器輸入端與輸入信號進行比較 (相加或相減),并用比較所得的有效輸入信號去控制輸出,負反饋可以用來穩定輸出信號或者增益,也可以擴展通頻帶,特別適合于自動控制系統。正反饋可以形成振蕩,適合振蕩電路和波形發生電路。

7負反饋種類及其優點

電壓并聯反饋,電流串聯反饋,電壓串聯反饋和電流并聯反饋

降低放大器的增益靈敏度,改變輸入電阻和輸出電阻,改善放大器的線性和非線性失真,有效地擴展,放大器的通頻帶,自動調節作用

8放大電路的頻率補償的目的是什么,有哪些方法

頻率補償 是為了改變頻率特性,減小時鐘和相位差,使輸入輸出頻率同步相位補償 通常是改善穩定裕度,相位補償與頻率補償的目標有時是矛盾的

不同的電路或者說不同的元器件對不同頻率的放大倍數是不相同的,如果輸入信號不是單一頻率,就會造成 高頻放大的倍數大,低頻放大的倍數小 ,結果輸出的波形就產生了失真

放大電路中頻率補償的目的 :一是改善放大電路的高頻特性,二是克服由于引入負反饋而可能出現自激振蕩現象,使放大器能夠穩定工作。

在放大電路中,由于 晶體管結電容的存在常常會使放大電路頻率響應的高頻段不理想 ,為了解決這一問題,常用的方法就是在電路中引入負反饋。然后,負反饋的引入又引入了新的問題,那就是負反饋電路會出現自激振蕩現象,所以為了使放大電路能夠正常穩定工作,必須對放大電路進行頻率補償。

頻率補償的方法可以分為 超前補償和滯后補償 ,主要是通過接入一些阻容元件來改變放大電路的開環增益在高頻段的相頻特性,目前使用最多的就是鎖相環

9有源濾波器和無源濾波器的區別

無源濾波器:這種電路主要有無源元件 R、L 和 C 組成;

有源濾波器:集成運放和 R、C 組成,具有不用電感、體積小、重量輕等優點。集成運放的開環電壓增益和輸入阻抗均很高,輸出電阻小,構成有源濾波電路后還具有一定的電壓放大和緩沖作用。但 集成運放帶寬有限 ,所以目前的有源濾波電路的工作頻率難以做得很高。

10名詞解釋:SRAM、SSRAM 、SDRAM、壓控振蕩器 (VCO)

SRAM:靜態 RAM ;DRAM:動態 RAM;SSRAM :Synchronous Static Random Access Memory 同步靜態隨機訪問存儲器,它的一種類型的 SRAM。SSRAM 的所有訪問都在時鐘的上升 /下降沿啟動。地址、數據輸入和其它控制信號均與時鐘信號相關。

這一點與異步 SRAM 不同,異步 SRAM 的訪問獨立于時 鐘,數據輸入和輸出都由地址的變化控制。SDRAM:Synchronous DRAM 同步動態隨機存儲器。

11名詞解釋:IRQ、BIOS 、USB、VHDL 、SDR。

(1) IRQ:中斷請求

(2)BIOS:BIOS 是英文"Basic Input Output System"的縮略語,直譯過來后中 文名稱就是"基本輸入輸出系統 "。其實,它是一組固化到計算機內主板上一個 ROM 芯片上的程序,它保存著計算機最重要的基本輸入輸出的程序、系統設置 信息、開機后自檢程序和系統自啟動程序。其主要功能是為計算機提供最底層的、 最直接的硬件設置和控制。

(3) USB:USB ,是英文 Universal Serial BUS(通用串行總線)的縮寫,而其 中文簡稱為“通串線,是一個外部總線標準,用于規范電腦與外部設備的連接和通訊。

(4) VHDL:VHDL 的英文全寫是:VHSIC(Very High Speed Integrated Circuit ) Hardware Description Language.翻譯成中文就是超高速集成電路硬件描述語言。主要用于描述數字系統的結構、行為、功能和接口。

(5) SDR:軟件無線電,一種無線電廣播通信技術,它基于軟件定義的無線通信協議而非通過硬連線實現。換言之,頻帶、空中接口協議和功能可通過軟件 下載和更新來升級,而不用完全更換硬件。SDR 針對構建多模式、多頻和多功 能無線通信設備的問題提供有效而安全的解決方案。

12單片機上電后沒有運轉,首先要檢查什么

首先應該確認電源電壓是否正常。用電壓表測量接地引腳跟電源引腳之間的電壓,看是否是電源電壓,例如常用的 5V。接下來就是檢查復位引腳電壓 是否正常。分別測量按下復位按鈕和放開復位按鈕的電壓值,看是否正確。然后 再檢查晶振是否起振了,一般用示波器來看晶振引腳的波形,注意應該使用示波器探頭的“ X10”檔。另一個辦法是測量復位狀態下的 IO 口電平,按住復位鍵不放,然后測量 IO 口( 沒接外部上拉的 P0 口除外) 的電壓,看是否是高電平,如果不是高電平,則多半是因為晶振沒有起振。另外還要注意的地方是,如果使用片內 ROM 的話( 大部分情況下如此,現在 已經很少有用外部擴 ROM 的了 ),一定要將 EA 引腳拉高,否則會出現程序亂跑的情況。如果系統不穩定的話,有時是因為電源濾波不好導致的。在單片機的電源引腳跟地引腳之間接上一個 0.1uF 的電容會有所改善。如果電源沒有濾波電容的話, 則需要再接一個更大濾波電容,例如 220uF 的。遇到系統不穩定時,就可以并上電容試試 (越靠近芯片越好)。

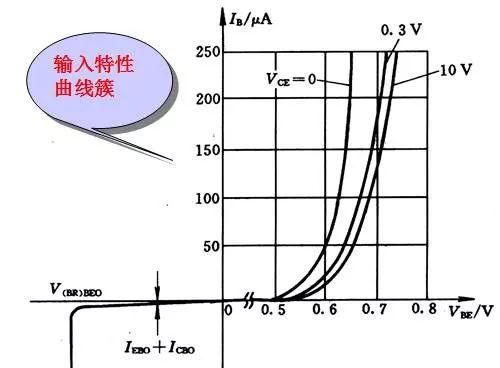

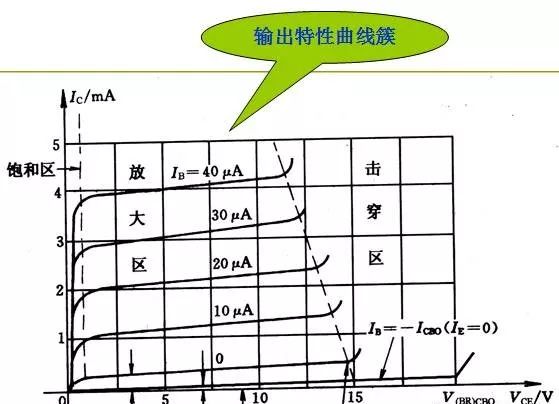

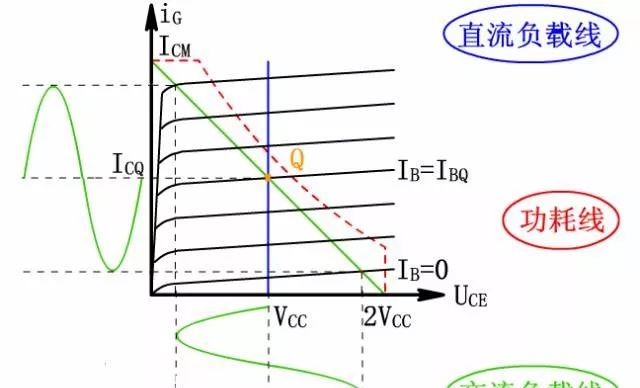

13最基本的三極管曲線特性

答:三極管的曲線特性即指三極管的伏安特性曲線,包括輸入特性曲線和輸 出特性曲線。輸入特性是指三極管輸入回路中,加在基極和發射極的電壓 VBE 與 由它所產生的基極電流 I B 之間的關系。輸出特性通常是指在一定的基極電流 I B控制下,三極管的集電極與發射極之間的電壓 VCE 同集電極電流 IC 的關系

圖(1)典型輸入特性曲線

圖(2)典型輸出特性曲線

圖(3)直、交流負載線,功耗線

14什么是頻率響應,怎么才算是穩定的頻率響應,簡述改變頻率響應曲線的幾個方法

答:這里僅對放大電路的頻率響應進行說明。在放大電路中,由于電抗元件 (如電容、電感線圈等)及晶體管極間電容的存在,當輸入信號的頻率過低或過高時,放大電路的放大倍數的數值均會降低,而且還將產生相位超前或之后現象。也就是說,放大電路的放大倍數 (或者稱為增 益 )和輸入信號頻率是一種函數關系,我們就把這種函數關系成為放大電路的頻 率響應或頻率特性。放大電路的頻率響應可以用幅頻特性曲線和相頻特性曲線來描述,如果一個 放大電路的幅頻特性曲線是一條平行于 x 軸的直線( 或在關心的頻率范圍內平行 于 x 軸 ),而相頻特性曲線是一條通過原點的直線 (或在關心的頻率范圍是條通過 原點的直線),那么該頻率響應就是穩定的

改變頻率響應的方法主要有:

(1) 改變放大電路的元器件參數;

(2) 引入新的 元器件來改善現有放大電路的頻率響應;

(3) 在原有放大電路上串聯新的放大電 路構成多級放大電路。

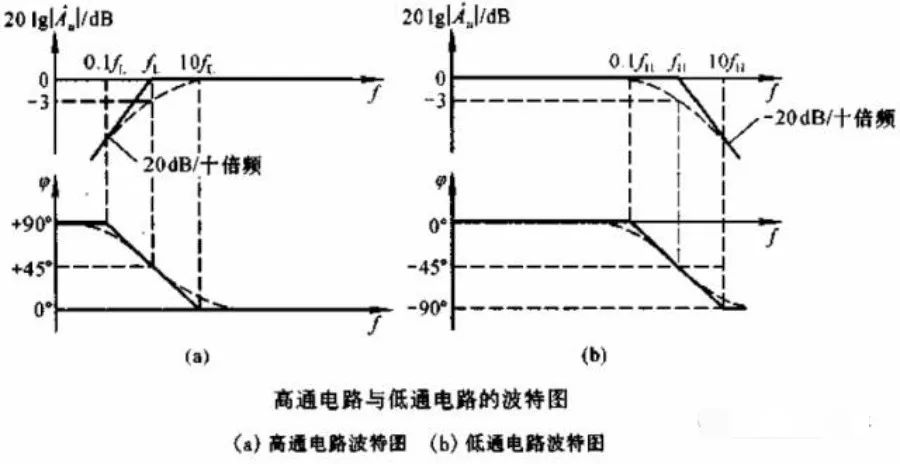

15給出一個差分運放,如何進行相位補償,并畫補償后的波特圖

答:隨著工作頻率的升高,放大器會產生附加相移,可能使負反饋變成正反饋而引起自激。進行相位補償可以消除高頻自激。相位補償的原理是:在具有高放大倍數的中間級,利用一小電容 C(幾十~幾百微微法)構成電壓并聯負反饋 電路。可以使用電容校正、 RC 校正分別對相頻特性和幅頻特性進行修改。

波特圖就是在畫放大電路的頻率特性曲線時使用對數坐標。波特圖由對數幅 頻特性和對數相頻特性兩部分組成,它們的橫軸采用對數刻度 lg f ,幅頻特性的縱軸采用 lg |Au|表示,單位為 dB;相頻特性的縱軸仍用φ表示。

16基本放大電路的種類及優缺點,廣泛采用差分結構的原因

基本放大電路按其接法分為共基、共射、共集放大電路。

共射放大電路既能放大電流又能放大電壓,輸入電阻在三種電路中居中,輸出電阻較大,頻帶較窄

共基放大電路只能放大電壓不能放大電流,輸入電阻小,電壓放大倍數和輸出電阻與共射放大電路相當,頻率特性是三種接法中最好的電路。常用于寬頻帶 放大電路。

共集放大電路只能放大電流不能放大電壓,是三種接法中輸入電阻最大、輸 出電阻最小的電路,并具有電壓跟隨的特點。常用于電壓大電路的輸入級和輸 出級,在功率放大電路中也常采用射極輸出的形式。

廣泛采用差分結構的原因是差分結構可以抑制溫度漂移現象。

17給出一差分電路,已知其輸出電壓 Y+和 Y-,求共模分量和差模分量

設共模分量是 Yc,差模分量是 Yd,則可知其輸

Y+=Yc+Yd Y-=Yc-Yd 可得 Yc=(Y+ + Y-)/2 Yd=(Y+ - Y-)/2

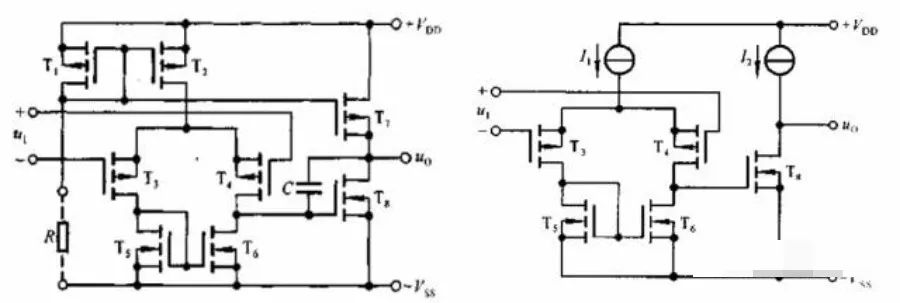

18畫出一個晶體管級的運放電路 ,說明原理

下圖 (a)給出了單極性集成運放 C14573 的電路原理圖,圖 (b)為其放大電路部分:

圖(a) C14573電路原理圖圖(b) C14573的放大電路部分

圖(a)中 T1,T2 和T7管構成多路電流源,為放大電路提供靜態偏置電流, 把偏置電路簡化后,就可得到圖 (b)所示的放大電路部分。

第一級是以 P 溝道管T3 和T4為放大管、以 N 溝道管T5 和T6管構成的電 流源為有源負載,采用共源形式的雙端輸入、單端輸出差分放大電路。由于第二 級電路從T8 的柵極輸入,其輸入電阻非常大,所以使第一級具有很強的電壓放大能力。

第二級是共源放大電路,以 N溝道管T8 為放大管,漏極帶有源負載,因此也具有很強的電壓放大能力。但其輸出電阻很大,因而帶負載能力較差。電容 C起相位補償作用。

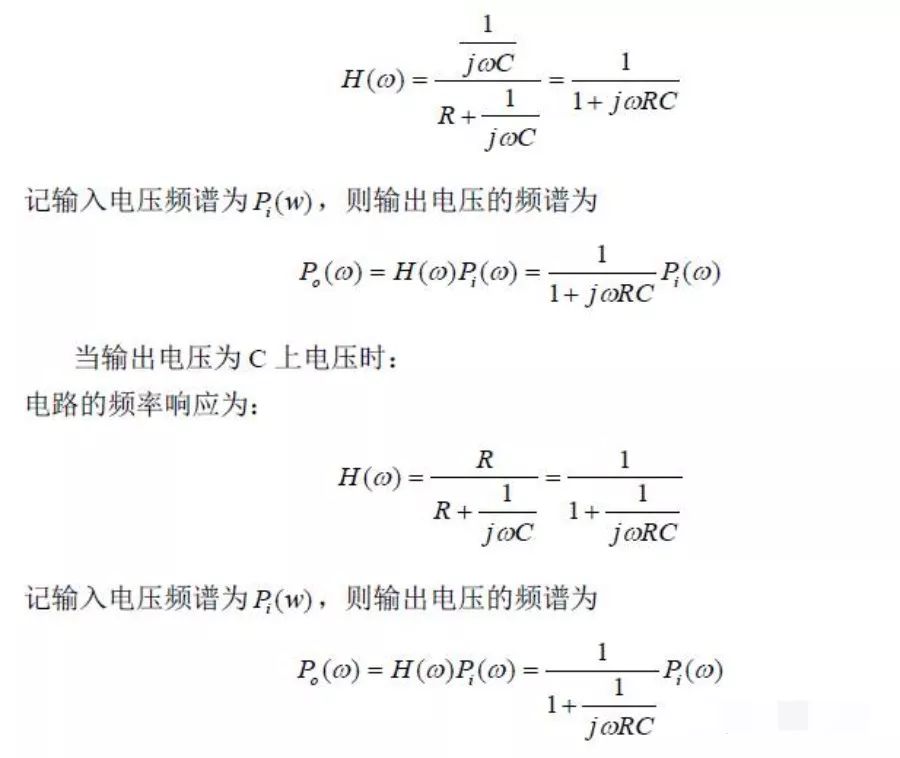

19電阻R和電容 C串聯,輸入電壓為R和C 之間的電壓,輸出電壓分別為 C上電壓和R上電壓,求這兩種電路輸出電壓的頻譜,判斷這兩種電路何為高通濾波器,何為低通濾波器。當 RC<

答:當輸出電壓為 C上電壓時:電路的頻率響應為

從電路的頻率響應不難看出輸出電壓加在 C上的為低通濾波器,輸出電壓加在 R上的為高通濾波器,RC<

20選擇電阻時要考慮什么?

主要考慮電阻的封裝、功率、精度、阻值和耐壓值等。

21在CMOS電路中,要有一個單管作為開關管精確傳遞模擬低電平,這個單管你會用 P管還是N管,為什么

答:用 N 管。N 管傳遞低電平, P 管傳遞高電平。N 管的閾值電壓為正, P 管的閾值電壓為負。在 N 管柵極加 VDD,在漏極加VDD,那么源級的輸出電壓范圍為 0到VDD-Vth ,因為 N 管的導通條件是 Vgs>Vth,當輸出到達 VDD-Vth 時管子已經關斷了。所以當柵壓為 VDD時,源級的最高輸出電壓只能為 VDD-Vth。這叫閾值損失。N 管的輸出要比柵壓損失一個閾值電壓。因此不宜用 N 管傳輸高電平。P 管的輸出也會比柵壓損失一個閾值。同理柵壓為 0時,P 管 源級的輸出電壓范圍為 VDD到|Vth |,因此不宜用 P管傳遞低電平。

22畫電流偏置的產生電路,并解釋。

基本的偏置電流產生電路包括鏡像電流源、比例電流源和微電流源三種。

下面以鏡像電流源電路為例進行說明:

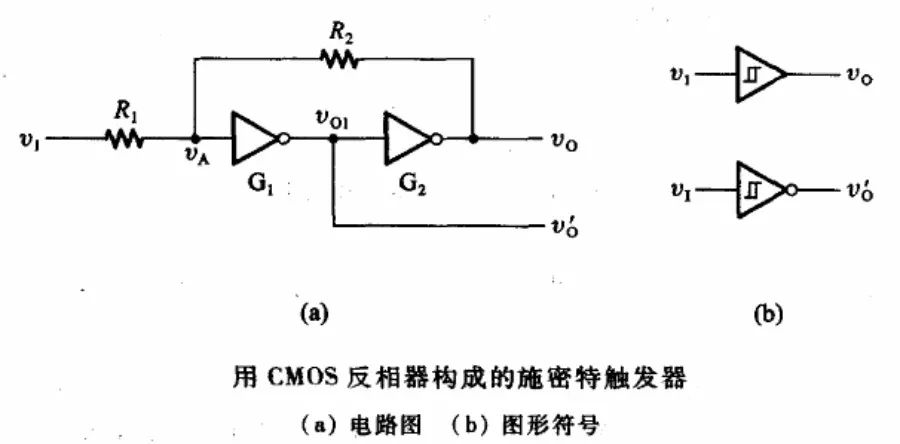

23畫出施密特電路,求回差電壓。

答:下圖是用 CMOS 反相器構成的施密特電路:

因此回差電壓為:

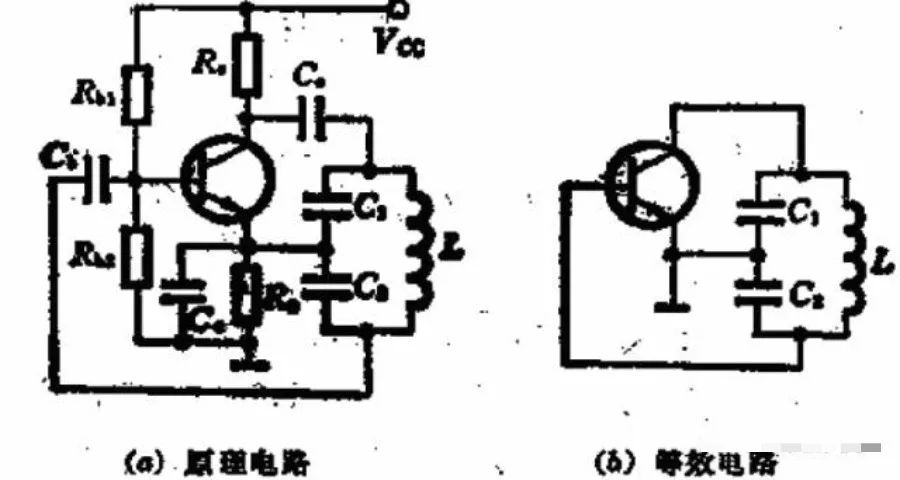

24LC 正弦波振蕩器有哪幾種三點式振蕩電路,分別畫出其原理圖。

答:主要有兩種基本類型:電容三點式電路和電感三點式電路。下圖中 (a)和(b) 分別給出了其原理電路及其等效電路

(a)電容三點式振蕩電路

(b)電感三點式振蕩電路

實現 DAC 轉換的方法有:權電阻網絡 D/A 轉換,倒梯形網絡 D/A 轉換, 權電流網絡 D/A 轉換、權電容網絡 D/A 轉換以及開關樹形 D/A 轉換等。

實現 ADC 轉換的方法有:并聯比較型 A/D 轉換,反饋比較型 A/D 轉換,雙 積分型 A/D 轉換和 V-F 變換型 A/D 轉換。

26A/D 電路組成、工作原理

A/D 電路由取樣、量化和編碼三部分組成,由于模擬信號在時間上是連續信 號而數字信號在時間上是離散信號,因此 A/D 轉換的第一步就是要按照奈奎斯 特采樣定律對模擬信號進行采樣。又由于數字信號在數值上也是不連續的,也就 是說數字信號的取值只有有限個數值,因此需要對采樣后的數據盡量量化,使其 量化到有效電平上,編碼就是對量化后的數值進行多進制到二進制二進制的轉換。

27為什么一個標準的倒相器中 P 管的寬長比要比 N 管的寬長比大?

和載流子有關, P 管是空穴導電,N 管電子導電,電子的遷移率大于空穴,同樣的電場下, N 管的電流大于 P 管,因此要增大 P 管的寬長比,使之對稱, 這樣才能使得兩者上升時間下降時間相等、高低電平的噪聲容限一樣、充電和放電是時間相等

28鎖相環有哪幾部分組成 ?

鎖相環路是一種反饋控制電路,簡稱鎖相環( PLL)鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現 輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。鎖相環在工作的過程中,當輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環名稱的由來鎖相環通常由鑒相器( PD)、環路濾波器(LF)和壓控振蕩器( VCO)三部 分組成。鎖相環中的鑒相器又稱為相位比較器,它的作用是檢測輸入信號和輸出 信號的相位差,并將檢測出的相位差信號轉換成電壓信號輸出,該信號經低通濾 波器濾波后形成壓控振蕩器的控制電壓,對振蕩器輸出信號的頻率實施控制。

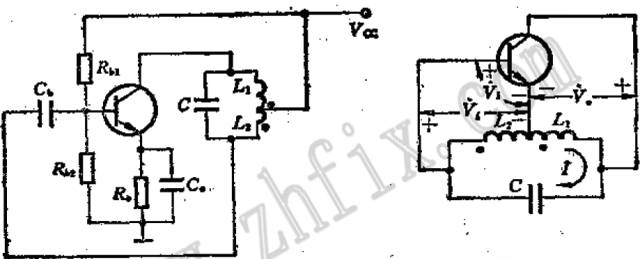

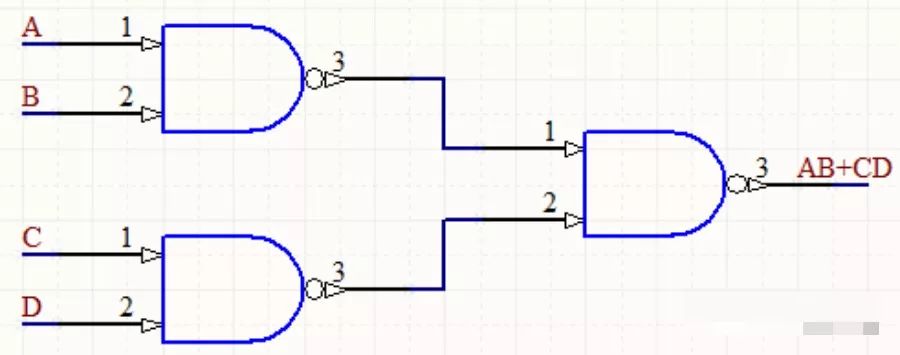

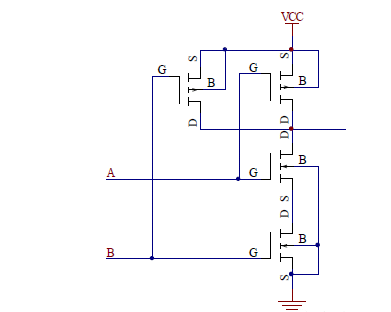

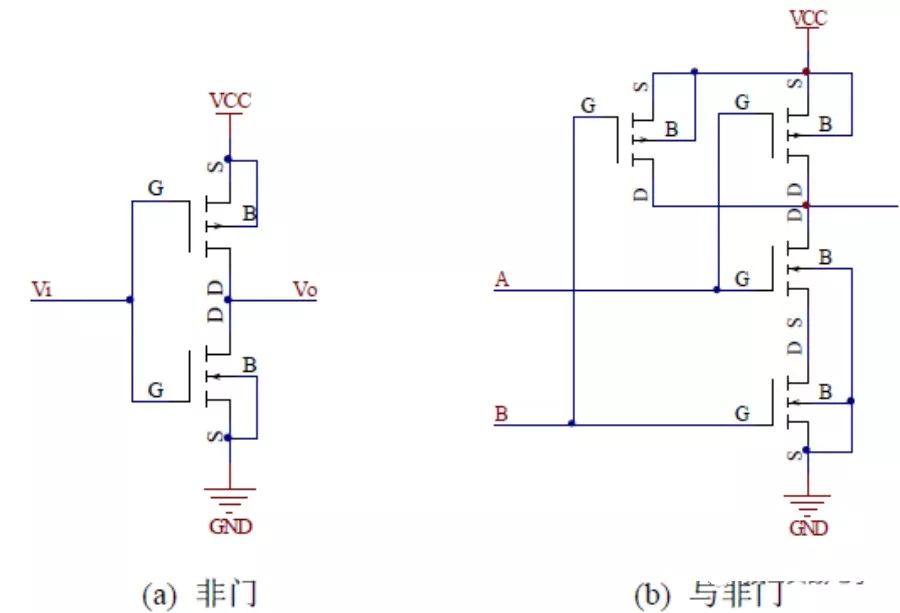

29用邏輯門和 COMS 電路實現 AB+CD

這里使用與非門實現:

(a)用邏輯門實現

(b)用CMOS電路組成的與非門

圖(a)給出了用與非門實現 AB+CD,圖(b) 給出了用 CMOS 電路組成的與非門,將圖 (b)代入圖(a) 即可得到用 CMOS 電路實現 AB+CD 的電路。

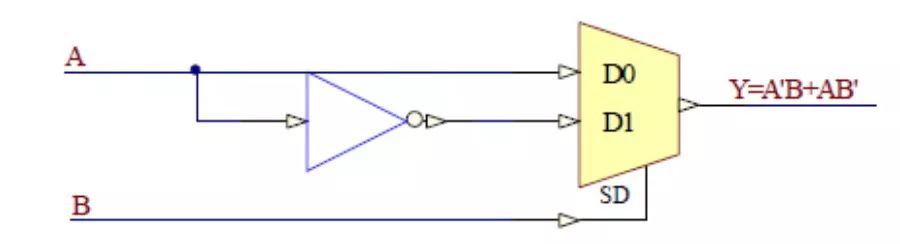

30用一個二選一 mux 和一個 inv 實現異或

假設輸入信號為 A、B ,輸出信號為 Y=A’B+AB ’。則用一個二選一 mux和一個 inv 實現異或的電路如下圖所示:

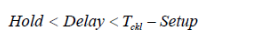

31給了 reg 的 Setup 和 Hold 時間,求中間組合邏輯的 Delay 范圍

假設時鐘周期為 Tclk ,reg 的 Setup 和 Hold 時間分別記為 Setup 和 Hold。則有:

32如何解決亞穩態

亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當 一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在亞穩態期間,觸發器輸出一些中間級電平,或 者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器 級聯式傳播下去。解決方法主要有:(1)降低系統時鐘;(2)用反應更快的 FF;(3) 引入同步機制,防止亞穩態傳播;(4)改善時鐘質量,用邊沿變化快速的時鐘信號;(5)使用工藝好、時鐘周期裕量大的器件

33集成電路前端設計流程,寫出相關的工具。

集成電路的前端設計主要是指設計 IC 過程的邏輯設計、功能仿真,而后端設計則是指設計 IC 過程中的版圖設計、制板流片。前端設計主要負責邏輯實現,通常是使用 verilog/VHDL 之類語言,進行行為級的描述。而后端設計,主要負責將前端的 設計變成真正的 schematic&layout,流片,量產。

集成電路前端設計流程可以分為以下幾個步驟:(1)設計說明書;(2)行為級 描述及仿真;(3)RTL 級描述及仿真;(4)前端功能仿真。

硬件語言輸入工具有 SUMMIT,VISUALHDL ,MENTOR 和 RENIOR 等;圖形輸入工具有: Composer(cadence), Viewlogic (viewdraw)等;

數字電路仿真工具有:Verolog:CADENCE 、Verolig-XL、 SYNOPSYS、VCS 、MENTOR、 Modle-sim

VHDL:CADENCE 、NC-vhdl、 SYNOPSYS、VSS 、MENTOR、 Modle-sim

模擬電路仿真工具:HSpice Pspice,

34是否接觸過自動布局布線 ,請說出一兩種工具軟件,自動布局布線需要哪些基本元素

Protel99se ORcad Allegro Pads2007 powerpcb 焊盤 阻焊層 絲印層 互聯線 注意模擬和數字分區域放置 敏感元件應盡量避免噪聲干擾 信號完整性 電源去耦

35描述你對集成電路工藝的認識

集成電路是采用半導體制作工藝,在一塊較小的單晶硅片上制作上許多晶體管及電阻器、電容器等元器件,并按照多層布線或遂道布線的方法將元器件組合成完整的電子電路。

(一)按功能結構分類

模擬集成電路和數字集成電路

(二)按制作工藝分類

厚膜集成電路和薄膜集成電路。

(三)按集成度高低分類

小規模集成電路、中規模集成電路、大規模集成電路和超大規模集成電路

(四)按導電類型不同分類

雙極型集成電路和單極型集成電路。

雙極型集成電路的制作工藝復雜,功耗較大,代表集成電路有 TTL、ECL 、HTL、 LST-TL、STTL 等類型

單極型集成電路的制作工藝簡單,功耗也較低,易于制成大規模集成電路,代表集成電路有 CMOS、NMOS 、PMOS等類型

36列舉幾種集成電路典型工藝,工藝上常提到 0.25,0.18指的是什么

制造工藝:我們經常說的 0.18微米、0.13 微米制程,就是指制造工藝了。制造工藝直接關系到 cpu的電氣性能,而0.18微米、 0.13微米這個尺度就是指的是 cpu核心中線路的寬度,MOS管是指柵長。

37請描述一下國內的工藝現狀

38半導體工藝中,摻雜有哪幾種方式

39描述CMOS電路中閂鎖效應產生的過程及最后的結果

Latch-up 閂鎖效應,又稱寄生PNPN效應或可控硅整流器 ( SCR, Silicon Controlled Rectifier )效應。在整體硅的 CMOS管下,不同極性攙雜的區域間都會構成 P-N結,而兩個靠近的反方向的 P-N結就構成了一個雙極型的晶體三極管。因此 CMOS管的下面會構成多個三極管,這些三極管自身就可能構成一個電路。這就是 MOS管的寄生三極管效應。如果電路偶爾中出現了能夠使三極管開通的條件,這個寄生的電路就會極大的影響正常電路的運作,會使原本的 MOS電路承受比正常工作大得多的電流,可能使電路迅速的燒毀。Latch-up狀態下器件在電源與地之間形成短路,造成大電流、 EOS(電過載)和器件損壞。

40解釋latch-up現象和 Antenna effect和其預防措施.

41什么叫窄溝效應

當JFET或 MESFET溝道較短,<1um的情況下,這樣的器件溝道內電場很高,載流子民飽合速度通過溝道,因而器件的工作速度得以提高,載流子漂移速度,通常用分段來描述,認為電場小于某一臨界電場時,漂移速度與近似與電場強成正比,遷移率是常數,當電場高于臨界時,速度飽和是常數。所以在短溝道中,速度是飽和的,漏極電流方程也發生了變化,這種由有況下飽和電流不是由于溝道夾斷引起的而是由于速度飽和

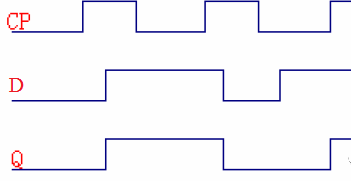

42用波形表示 D 觸發器的功能

以電平觸發為例進行說明, D 觸發器的功能描述如下:當時鐘信號為低電平 時,觸發器不工作,處于維持狀態。當時鐘信號為高電平時, D 觸發器的功能為:若 D=0,則觸發器次態為 0;若 D=1,則觸發器次態為 1。下圖以波形形式來描 述 D 觸發器的功能:

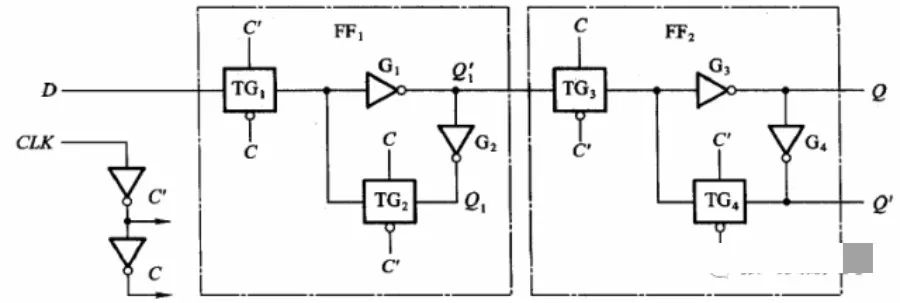

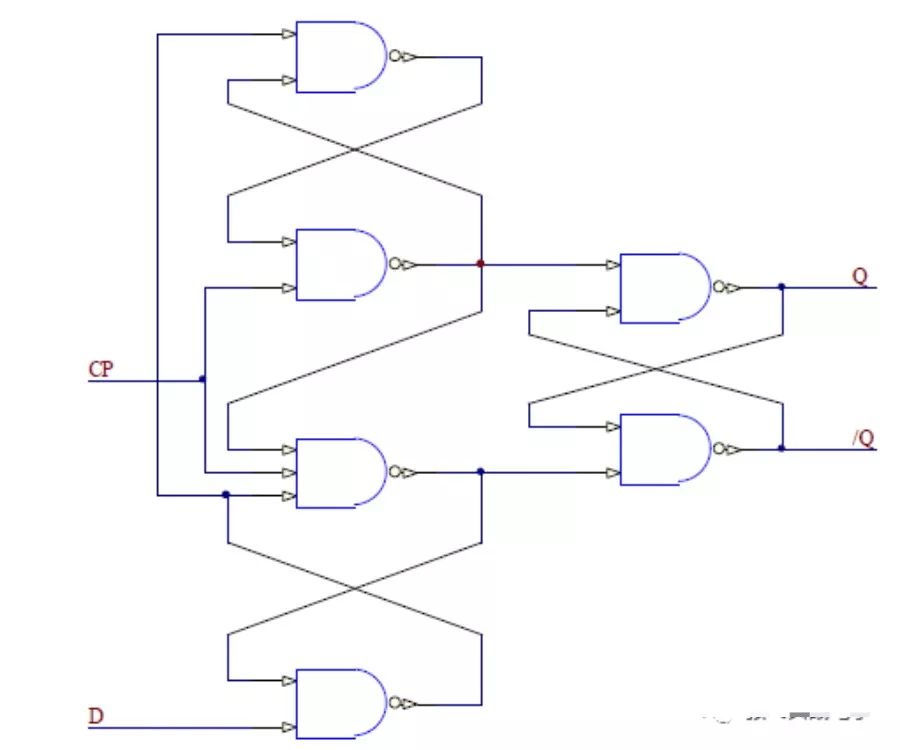

43用傳輸門和倒向器組成的邊沿 D 觸發器如下圖:

44畫狀態機,接受 1、2 、5 分錢的賣報機,每份報紙 5 分錢。

取投幣信號為輸入邏輯變量,投入一枚 5 分硬幣是用 A=1 表示,未投入時用 A=0 表示;投入一枚 2 分硬幣是用 B=1 表示,未投入時用 B=0 表示;投入 一枚 1 分硬幣是用 C=1 表示,未投入時用 C=0 表示。由于每次最多只能投入一 枚硬幣,因此除了 ABC=000、 ABC=001、 ABC=010 和 ABC=100 四種狀態為 合法狀態,其它四種狀態為非法狀態。假設投入 3 個 2 分硬幣或者投入 4 個 1 分硬幣和 1 個 2 分硬幣后,賣報機在給出報紙的同時會找會 1 個 1 分硬幣。這是 輸出變量有兩個,分別用 Y 和 Z 表示。給出報紙時 Y=1,不給時 Y=0 ;找回 1 個 1 分硬幣時 Z=1 ,不找時 Z=0。同時假定未投幣時賣報機的初始狀態為 S0, 從開始到當前時刻共投入的硬幣面值為 1 分記為 S1 ,為 2 分時記為 S2,為 3 分 記為 S3,為 4 分時記為 S4。

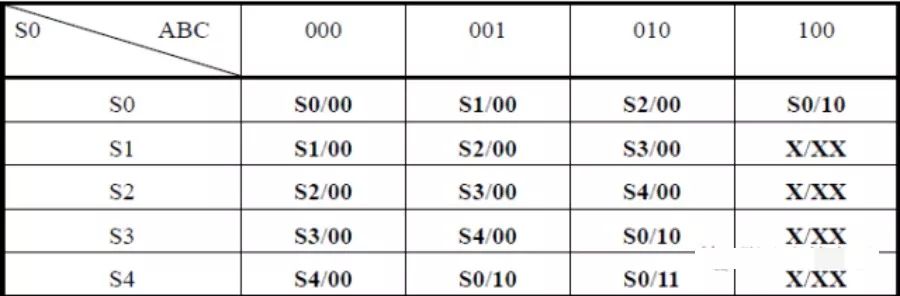

由上面的分析可以畫出該狀態機的狀態轉換表,如下表所示 (方便起見,這里 給出輸入變量為非法狀態時的轉換表 )

狀態圖如下所示

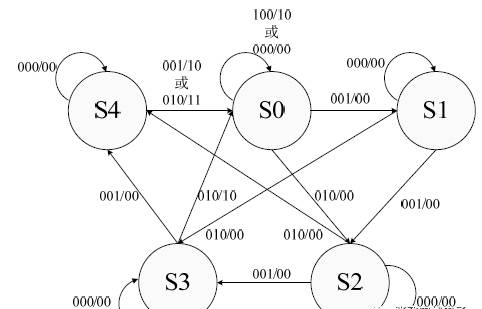

45用與非門等設計全加法器

設加數為 A 和 B ,低位進位為 C,和為 Sum ,進位位為 Cout,則用與非門 設計的全加器如下圖

如果非門也用與非門實現的話,只需將與非門的兩個輸入端連接,置換到非門即可

46RS232c 高電平脈沖對應的 TTL 邏輯是?

首先解釋一下什么是正邏輯和負邏輯。正邏輯:用高電平表示邏輯 1,用低電平表示邏輯 0。負邏輯:用低電平表示邏輯 1,用高電平表示邏輯 0。在數字 系統的邏輯設計中,若采用 NPN 晶體管和 NMOS 管,電源電壓是正值,一般采 用正邏輯。若采用的是 PNP 管和 PMOS 管,電源電壓為負值,則采用負邏輯比 較方便。除非特別說明,一般電路都是采用正邏輯

對于 RS232C 的數據線,邏輯 1(MARK)=-3V~ -15V ;邏輯 0(SPACE)=+3 ~+15V,因此對應的 TTL 邏輯為負邏輯。

47VCO 是什么,什么參數 (壓控振蕩器) ?

VCO 即壓控振蕩器,在通信系統電路中,壓控振蕩器 (VCO)是其關鍵部件, 特別是在鎖相環電路、時鐘恢復電路和頻率綜合器等電路中。VCO 的性能指標 主要包括:頻率調諧范圍,輸出功率, (長期及短期)頻率穩定度,相位噪聲,頻 譜純度,電調速度,推頻系數,頻率牽引等。

48什么耐奎斯特定律,怎么由模擬信號轉為數字信號

49用 D 觸發器做個 4 進制的計數器

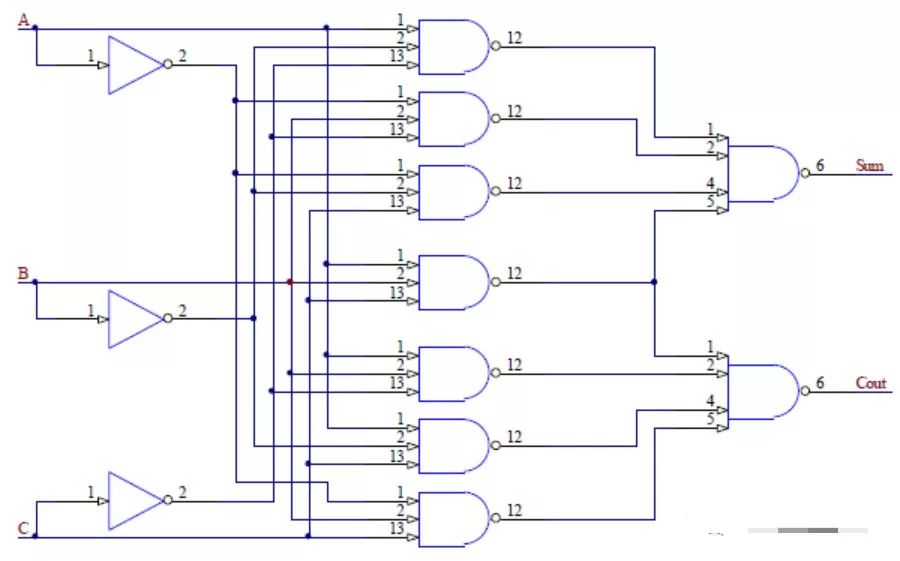

由于是 4 進制計數器,因此只需兩個 D 觸發器即可,記進位輸出為 Cout, 時鐘信號為 CLK,則利用 D 觸發器和門電路組成的 4 進制計數器如下圖:

50鎖存器、觸發器、寄存器三者的區別

觸發器:能夠存儲一位二值信號的基本單元電路統稱為“觸發器”。

鎖存器:一位觸發器只能傳送或存儲一位數據,而在實際工作中往往希望一次傳送或存儲多位數據。為此可把多個觸發器的時鐘輸入端 CP 連接起來,用一個公共的控制信號來控制,而各個數據端口仍然是各處獨立地接收數據。這樣所構成的能一次傳送或存儲多位數據的電路就稱為“鎖存器”。

寄存器:在實際的數字系統中,通常把能夠用來存儲一組二進制代碼的同步時序邏輯電路稱為寄存器。由于觸發器內有記憶功能,因此利用觸發器可以方便地構成寄存器。由于一個觸發器能夠存儲一位二進制碼,所以把 n 個觸發器的時鐘端口連接起來就能構成一個存儲 n 位二進制碼的寄存器。

區別:從寄存數據的角度來年,寄存器和鎖存器的功能是相同的,它們的區別在于寄存器是同步時鐘控制,而鎖存器是電位信號控制。可見,寄存器和鎖存器具有不同的應用場合,取決于控制方式以及控制信號和數據信號之間的時間關系:若數據信號有效一定滯后于控制信號有效,則只能使用鎖存器;若數據信號

提前于控制信號到達并且要求同步操作,則可用寄存器來存放數據

51D 觸發器和 D 鎖存器的區別

D 觸發器是指由時鐘邊沿觸發的存儲器單元,鎖存器指一個由信號而不是時 鐘控制的電平敏感的設備。鎖存器通過鎖存信號控制,不鎖存數據時,輸出端的信號隨輸入信號變化,就像信號通過緩沖器一樣,一旦鎖存信號起鎖存作用,則數據被鎖住,輸入信號不起作用。

52有源濾波器和無源濾波器的原理及區別

濾波器是一種對信號的頻率具有選擇性的電路,其功能就是使特定頻率范圍內的信號通過,而組織其它頻率信號通過。其原理就是當不同頻率的信號通過該電路時,具有不同的幅度衰減,通帶內的信號衰減很小,而阻帶內的信號衰減很 大。

若濾波電路僅由無源元件 (電阻、電容、電感)組成,則稱為無源濾波器;若濾波電路不僅由無源元件,還有有源元件 (雙極型管、單極性管、集成運放 )組成, 則稱為有源濾波器。其區別主要體現在以下幾個方面:

(1) 有源濾波器是電子的,無源濾波器是機械的。

(2) 有源濾波器是檢測到某 一設定好的諧波次數后抵消它,無源濾波器是通過電抗器與電容器的配合形成某 次諧波通道吸收諧波。

(3) 采用無源濾波器因為有電容器的原因,所以可提高功 率因素。采用有源濾波器只是消除諧波與功率因素無關。

(4) 有源濾波器造價是 無源濾波器的 3 倍以上,技術相對不太成熟,且維護成本高;無源濾波器造價相 對較低,技術較成熟,安裝后基本免維護。

(5) 有源濾波器用于小電流,無源濾 波器可用于大電流。

53IIR, FIR 濾波器的異同

IIR 是無限長沖激響應濾波器, FIR 是有限長沖激響應濾波器。兩者的比較 如下:

(1) 在相同的技術指標下,IIR 濾波器由于存在著輸出對輸入的反饋,所以可用比 FIR 濾波器較少的階數來滿足指標的要求,所用的存儲單元少,運算次數少, 較為經濟

(2) FIR 濾波器可得到嚴格的線性相位,而 IIR 濾波器做不到這一點,IIR 濾 波器的選擇性越好,其相位的非線性越嚴重。因而,如果 IIR 濾波器要得到線性相位,又要滿足幅度濾波的技術要求,必須加全通網絡進行相位校正,這同樣會 大大增加濾波器的階數。

(3) FIR 濾波器主要采用非遞歸結構,因為無論是從理論上還是從實際的有限 精度的運算中它都是穩定的,有限精度運算的誤差也越小。IIR 濾波器必須采用 遞歸結構,極點必須在 z 平面單位圓內才能穩定,對于這種結構,運算中的四舍 五入處理有時會引起寄生振蕩。

(4) 對于 FIR 濾波器,由于沖激響應是有限長的,因而可以用快速傅里葉變換算法,這樣運算速度可以快得多。IIR 濾波器則不能這樣運算。

(5) 從設計上看,IIR 濾波器可以利用模擬濾波器設計的現成的閉合公式、數據和表格,因此計算工作量較小,對計算工具要求不高。FIR 濾波器則一般沒有 現成的設計公式,一般 FIR 濾波器設計僅有計算機程序可資利用,因而要借助于 計算機。

(6) IIR 濾波器主要是設計規格化的、頻率特性為分段常數的標準低通、高通、帶通、帶阻、全通濾波器。FIR 濾波器則要靈活得多。

54冒泡排序的原理

冒泡排序 (BubbleSort)的基本概念是:依次比較相鄰的兩個數,將小數放在前面,大數放在后面。即首先比較第 1 個和第 2 個數,將小數放前,大數放后。然 后比較第 2 個數和第 3 個數,將小數放前,大數放后,如此繼續,直至比較最后 兩個數,將小數放前,大數放后。重復以上過程,仍從第一對數開始比較 (因為 可能由于第 2 個數和第 3 個數的交換,使得第 1 個數不再小于第 2 個數 ),將小 數放前,大數放后,一直比較到最大數前的一對相鄰數,將小數放前,大數放后, 第二趟結束,在倒數第二個數中得到一個新的最大數。如此下去,直至最終完成 排序。由于在排序過程中總是小數往前放,大數往后放,相當于氣泡往上升,所以稱 作冒泡排序。

55操作系統的功能

操作系統是管理系統資源、控制程序執行,改善人機界面,提供各種服務,合理組織計算機工作流程和為用戶使用計算機提供良好運行環境的一種系統軟 件。資源管理是操作系統的一項主要任務,而控制程序執行、擴充機器功能、提 供各種服務、方便用戶使用、組織工作流程、改善人機界面等等都可以從資源管 理的角度去理解。下面從資源管理的觀點來看操作系統具有的幾個主要功能:

(1) 處理機管理:處理機管理的第一項工作是處理中斷事件。硬件只能發現中斷事件,捕捉它并產生中斷信號,但不能進行處理,配置了操作系統,就能對中斷事件進 行處理。處理機管理的第二項工作是處理器調度。處理器是計算機系統中一種稀有和寶 貴的資源,應該最大限度地提高處理器的利用率。

(2) 存儲管理:存儲管理的主要任務是管理存儲器資源,為多道程序運行提供有力的支撐,便于用戶使用存儲資源,提高存儲空間的利用率。

(3) 設備管理:設備管理的主要任務是管理各類外圍設備,完成用戶提出的 I/O 請求,加快 I/O 信息的傳送速度,發揮 I/O 設備的并行性,提高 I/O 設備的 利用率,以及提供每種設備的設備驅動程序和中斷處理程序,用戶隱蔽硬件細 節,提供方便簡單的設備使用方法。

(4) 文件管理:文件管理是針對系統中的信息資源的管理。在現代計算機中, 通常把程序和數據以文件形式存儲在外存儲器 (又叫輔存儲器)上,供用戶使用, 這樣,外存儲器上保存了大量文件,對這些文件如不能采取良好的管理方式,就 會導致混亂或破壞,造成嚴重后果。為此,在操作系統中配置了文件管理,它的 主要任務是對用戶文件和系統文件進行有效管理,實現按名存取;實現文件的共 享、保護和保密,保證文件的安全性;并提供給用戶一整套能方便使用文件的操 作和命令。

(5) 網絡與通信管理

56IC 設計中同步復位與異步復位的區別

同步復位在時鐘沿才復位信號,完成復位動作。異步復位不管時鐘,只 要復位信號滿足條件,就完成復位動作。異步復位對復位信號要求比較高,不能 有毛刺,如果其與時鐘關系不確定,也可能出現亞穩態。

57Moore 與 Mealy 狀態機的特征

答:Moore 狀態機的輸出僅與當前狀態值有關 , 且只在時鐘邊沿到來時才會 有狀態變化. Mealy 狀態機的輸出不僅與當前狀態值有關 , 而且與當前輸入值有 關。

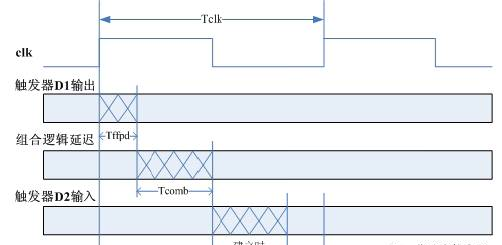

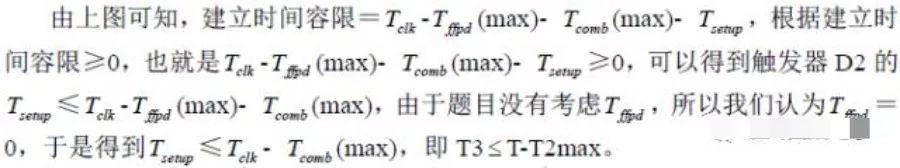

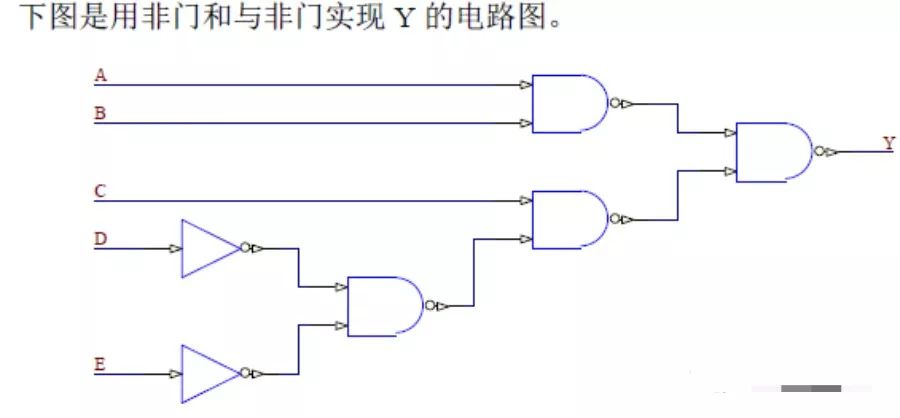

58時鐘周期為 T,觸發器 D1 的建立時間最大為 T1max,最小為 T1min。組合邏 輯電路最大延遲為 T2max,最小為 T2min。問,觸發器 D2 的建立時間 T3 和保 持時間 T4 應滿足什么條件

首先說下建立時間和保持時間的定義。

建立時間 (setup time)是指在觸發器的時鐘信號上升沿到來以前,數據穩定不 變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被打入觸發器;保 持時間(hold time) 是指在觸發器的時鐘信號上升沿到來以后,數據穩定不變的時 間, 如果保持時間不夠,數據同樣不能被打入觸發器。

Tffpd :觸發器的輸出響應時間,也就是觸發器的輸出在 clk 時鐘上升沿到來 后多長的時間內發生變化并且穩定,也可以理解為觸發器的輸出延時。

Tcomb :觸發器的輸出經過組合邏輯所需要的時間,也就是題目中的組合邏輯 延遲。

Tsetup :建立時間

Thold :保持時間

Tclk :時鐘周期

建立時間容限:相當于保護時間,這里要求建立時間容限大于等于 0。

保持時間容限:保持時間容限也要求大于等于 0。

關于保持時間的理解就是,在觸發器 D2 的輸入信號還處在保持時間的時候,如果觸發器 D1 的輸出已經通過組合邏輯到達 D2 的輸入端的話,將會破壞 D2本來應該保持的數據

59給出某個一般時序電路的圖,有 Tsetup、Tdelay、 Tck->q,還有 clock 的 delay, 寫出決定最大時鐘的因素,同時給出表達式

T+Tclkdealy>Tsetup+Tco+Tdelay ;

Thold>Tclkdelay+Tco+Tdelay ;

60說說靜態、動態時序模擬的優缺點。

靜態時序分析是采用窮盡分析方法來提取出整個電路存在的所有時序路徑,計算信號在這些路徑上的傳播延時,檢查信號的建立和保持時間是否滿足時 序要求,通過對最大路徑延時和最小路徑延時的分析,找出違背時序約束的錯誤。它不需要輸入向量就能窮盡所有的路徑,且運行速度很快、占用內存較少,不僅 可以對芯片設計進行全面的時序功能檢查,而且還可利用時序分析的結果來優化 設計,因此靜態時序分析已經越來越多地被用到數字集成電路設計的驗證中。動態時序模擬就是通常的仿真,因為不可能產生完備的測試向量,覆蓋門級網表 中的每一條路徑。因此在動態時序分析中,無法暴露一些路徑上可能存在的時序 問題。

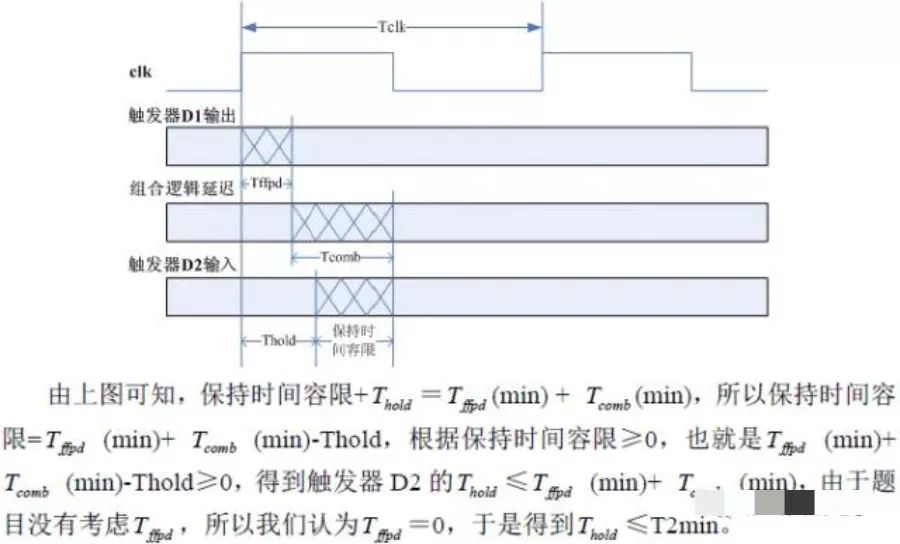

61畫出 CMOS 電路的晶體管級電路圖,實現 Y=A*B+C(D+E)

此類題目都可以采用一種做法,首先將表達式全部用與非門和非門表示,然后將用 CMOS 電路實現的非門和與非門代入即可。非門既可以單獨實現,也可 以用與非門實現(將兩輸入端接在一起即可 )

下圖 (a)和(b) 分別為用 CMOS 實現的非門和與非門

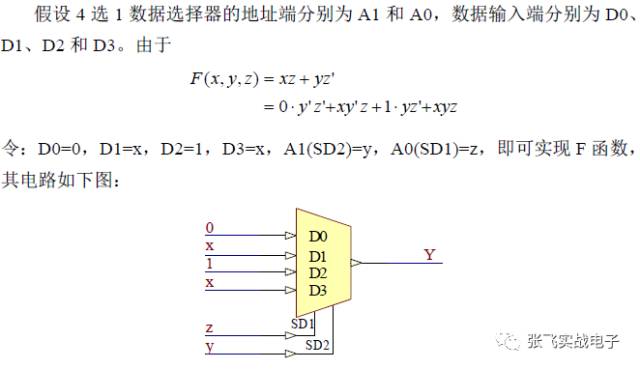

62利用 4 選 1 數據選擇器實現 F(x,y,z)=xz+yz’

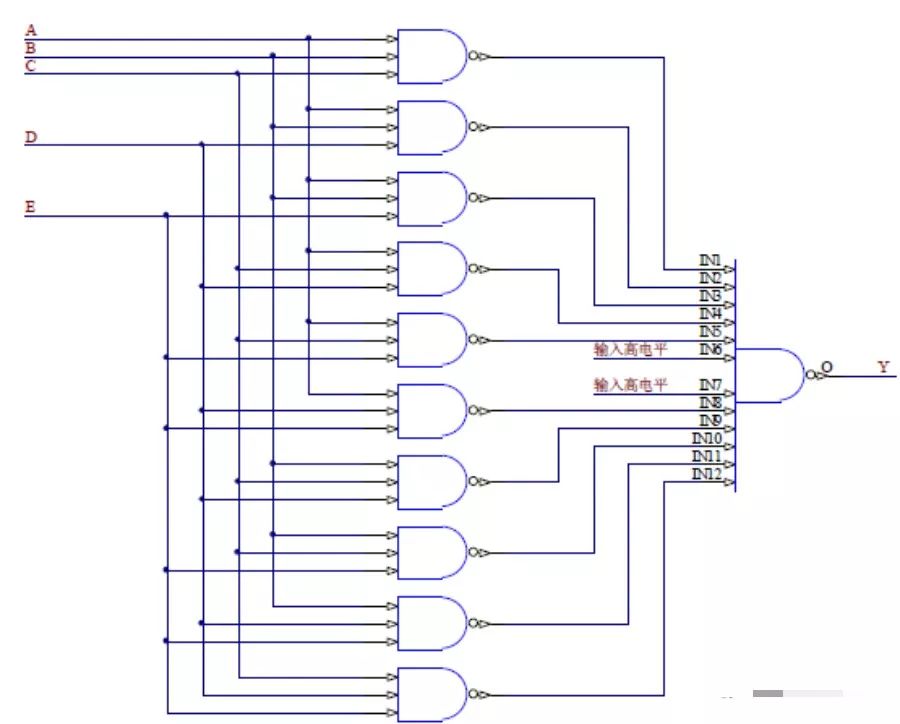

63A、 B、C、 D、E 進行投票,多數服從少數,輸出是 F(也就是如果 A、B 、C、D 、E 中 1 的個數比 0 多,那么 F 輸出為 1 ,否則 F 為 0) ,用與非門實現,輸入 數目沒有限制

記 A 贊成時 A=1,反對時 A=0 ;B 贊成時 A=1,反對時 B=0 ;C、 D、E 亦 是如此。由于共 5 人投票且少數服從多數,因此只要有三人投贊成票即可,其他人的投票結果并不需要考慮。基于以上分析,下圖給出用與非門實現的電路:

64用邏輯門畫出 D 觸發器

65簡述 latch 和 filp-flop 的異同

本題即問鎖存器與觸發器的異同。

觸發器:能夠存儲一位二值信號的基本單元電路統稱為“觸發器”。

鎖存器:一位觸發器只能傳送或存儲一位數據,而在實際工作中往往希望一次傳送或存儲多位數據。為此可把多個觸發器的時鐘輸入端 CP 連接起來,用一個公共的控制信號來控制,而各個數據端口仍然是各處獨立地接收數據。這樣所構成的能一次傳送或存儲多位數據的電路就稱為“鎖存器”

66LATCH 和 DFF 的概念和區別

本題即問 D 鎖存器與 D 觸發器的概念與區別。

D 觸發器是指由時鐘邊沿觸 發的存儲器單元,鎖存器指一個由信號而不是時鐘控制的電平敏感的設備

鎖存器通過鎖存信號控制,不鎖存數據時,輸出端的信號隨輸入信號變化,就像信號 通過緩沖器一樣,一旦鎖存信號起鎖存作用,則數據被鎖住,輸入信號不起作用。

67latch 與 register 的區別,為什么現在多用 register。行為級描述中 latch 如何產生的

latch 是電平觸發,register 是邊沿觸發, register 在同一時鐘邊沿觸發下 動作,符合同步電路的設計思想,而 latch 則屬于異步電路設計,往往會導致時 序分析困難,不適當的應用 latch 則會大量浪費芯片資源。

68How many flip-flop circuits are needed to divide by 16 (Intel)

69用 filp-flop 和 logic-gate 設計一個 1 位加法器,輸入 carryin 和 current-stage , 輸出 carryout 和 next-stage.

考設計具有輸入輸出緩沖功能的加法器,這樣理解的話,題目做起來很簡單,只要將輸入和輸出各加一個觸發器 作為數據鎖存器即可,也就是需要 4 個觸發器。加法功能完全由門電路實現。

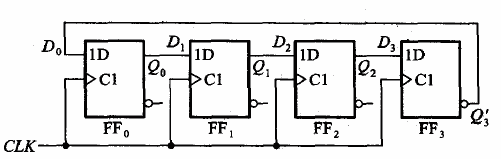

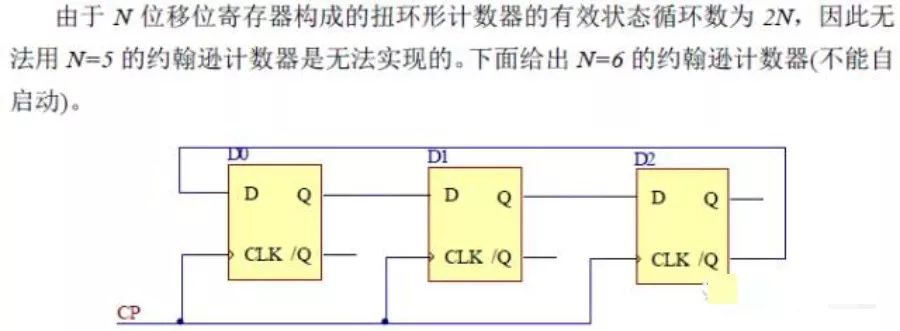

70實現 N 位 Johnson Counter,N=5

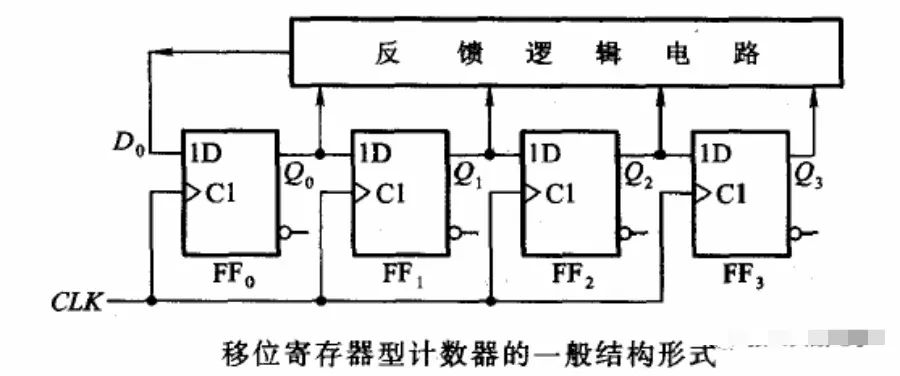

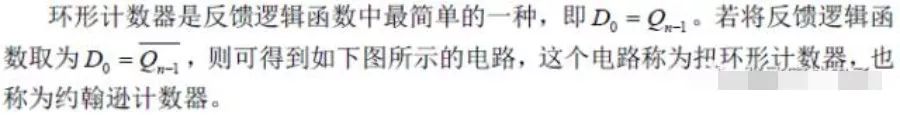

首先給大家解釋下 Johnson Counter,Johnson Counter 即約翰遜計數器,又稱扭環形計數器,是移位寄存器型計數器的一種。

由于環形計數器的電路狀態利用率較低,為了在不改變移位寄存器內部結構的條件下提高環形計數器的電路狀態利用率,只能從改變反饋邏輯電路上想辦法。

事實上任何一種移位寄存器型計數器的結構都可表示為如下圖所示的一般形式。其中反饋邏輯電路的函數表達式可寫成:

71Cache 的主要作用是什么,它與 Buffer 有何區別,DSP

Cache 即是高速緩沖存儲器,Cache 是一個高速小容量的臨時存儲器,可以用高速的靜態存儲器芯片實現, 或者集成到 CPU 芯片內部,存儲 CPU 最經常訪問的指令或者操作數據

Buffer 與 Cache 操作的對象不一樣。Buffer(緩沖) 是為了提高內存和硬盤 (或 其他 I/0 設備 )之間的數據交換的速度而設計的。Cache(緩存) 是為了提高 cpu 和內 存之間的數據交換速度而設計,也就是平常見到的一級緩存、二級緩存、三級緩 存等。

嵌入式 DSP 處理器(Embedded Digital Signal Processor, EDSP) 對系統結構和 指令進行了特殊設計,使其適合于執行 DSP 算法,編譯效率較高,指令執行速 度也較高。在數字濾波、 FFT、譜分析等方面 DSP 算法正在大量進入嵌入式領域, DSP 應用正從在通用單片機中以普通指令實現 DSP 功能,過渡到采用嵌入式 DSP 處理器。嵌入式 DSP 處理器有兩個發展來源,一是 DSP 處理器經過單片化、EMC 改造、增加片上外設成為嵌入式 DSP 處理器,TI 的 TMS320C2000 /C5000 等屬 于此范疇;二是在通用單片機或 SOC 中增加 DSP 協處理器,例如 Intel 的 MCS-296 和 Infineon(Siemens)的 TriCore。

72DSP 和通用處理器在結構上有什么不同

與通用處理器相比, DSP 屬于專用處理器,它是為了實現實時數字信號處理 而專門設計的。在結構上, DSP 一般采用哈佛結構,即數據緩存和指令緩存相分開。DSP 有專門的乘加指令,一次乘加只需一個指令周期即可完成、而通用處理 器中的乘法一般使用加法實現的,一次乘法需要消耗較多的指令周期。

73用你熟悉的設計方式設計一個可預置初值的 7 進制循環計數器,15 進制的呢

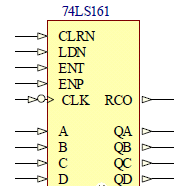

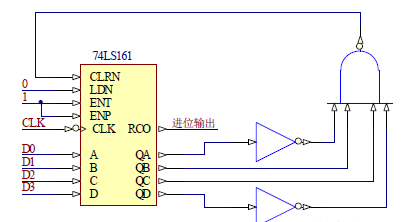

這里選擇用十六進制計數器 74LS161 實現,原理很簡單:用 74LS161 實現 N(N<16)進制計數器,只需當計數器從 0000 增加到 N-1 時讓 74LS161 清零即可。對于 7 進制,當增加到 6(0110)時將計數器清零即可。下面簡單介紹下 74LS161,下圖為 74LS161 的原理圖:

管腳說明:A、B 、C、 D:數據輸入端 QA、 QB、QC 、QD:數據輸出端 RCO:進位輸出端 CLRN:異步清零端,低電平有效 LDN:同步并行置入控制端,低電平有效

ENT、ENP :計數控制端,高電平有效。

下圖為用 74LS161 設計的可預置初值的 7 進制循環計數器, D3 D2 D1D0 為預置數輸入端。

如果想設計 15 進制,只要在 QD QC QB QA=1110 時將 CLRN 置低即可。

74BLOCKING 和 NONBLOCKING 賦值的區別

非阻塞賦值:塊內的賦值語句同時賦值,一般用在時序電路描述中;

阻塞賦值:完成該賦值語句后才能做下一句的操作,一般用在組合邏輯描述。

75PCI 總線的含義是什么, PCI 總線的主要特點是什么

PCI 的英文全稱為 Peripheral Component Interconnect。即外部設備互聯總線, 是于 1993 年推出的 PC 局部總線標準。PCI 總線可以分為 32 位總線和 64 位總線 兩種,一般 PC 機使用 32 位 PCI 總線,服務器和高級工作站都帶有 64 位 PCI 總 線。PCI 總線的主要特點是傳輸速度高,目前可實現 66M 的工作頻率,在 64 位 總線寬度下可達到突發( Burst)傳輸速率 264MB/s,是通常 ISA 總線的 300 倍, 可以滿足大吞吐量的外設的需求。

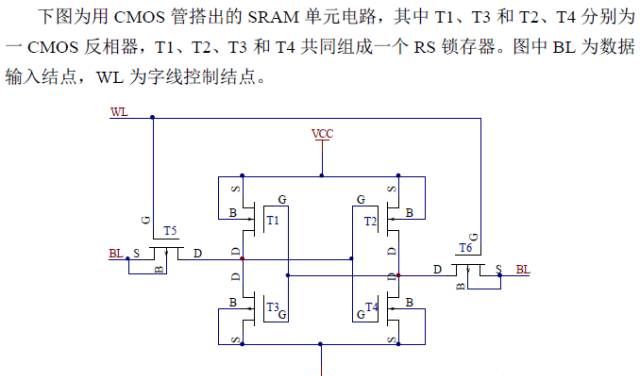

76Please draw schematic of a common SRAM cell with 6 transistors,point out which nodes can store data and which node is word line control

77有一個 LDO 芯片將用于對手機供電,需要你對它進行評估,你將如何設計你的測試項目

LDO 為低壓差線性穩壓器,這里將其用于對手機供電。需要評估的指標主要 有兩個:LDO 的供電電流和供電電壓、 LDO 的輸出電壓噪聲抑制比。由于手機 是電池供電,因此測試該 LDO 芯片是最好選用鋰電池給芯片供電。

供電電流與供電電壓的測試:選擇一臺具有存儲功能的示波器,在對應測試 點測試芯片的輸出電壓和輸出電流 (可能需要用數字萬用表測 ),觀察結果看起輸 出電壓與輸出電流是否滿足手機的正常工作要求。

輸出電壓噪聲抑制比:這個也許需要更精確的儀器去測了,我不是很懂,希 望大家指教。

芯片性能的測試需要長時間測試,而且需要在不同環境下測試,如改變溫度、 濕度,或者在移動條件下測試。此外,還要測試輸入電壓發生變化時輸出電壓和 輸出電流的變化。

-

數字電路

+關注

關注

193文章

1600瀏覽量

80498 -

觸發器

+關注

關注

14文章

1996瀏覽量

61052

原文標題:【別找了全在這】硬件工程師經典筆試題集錦!

文章出處:【微信號:EngicoolArabic,微信公眾號:電子工程技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

硬件工程師經典筆試題集錦!

硬件工程師經典筆試題集錦!

評論