當(dāng)一塊PCB板完成了布局布線,完成連通性和間距的檢查后,還有一個(gè)很重要的步驟--后期檢查。

但是很多初學(xué)者也包括一些有經(jīng)驗(yàn)的工程師由于種種原因容易忽略了后期檢查這一步驟。導(dǎo)致出現(xiàn)一些很基本的BUG,比如線寬不夠,元件標(biāo)號絲印壓在過孔上,插座靠得太近,信號出現(xiàn)環(huán)路等等。從而導(dǎo)致電氣問題或者工藝問題,嚴(yán)重的要重新打板,造成浪費(fèi)。

所以,當(dāng)一塊PCB完成了布局布線之后,別忘了還有一個(gè)很重要的步驟--后期檢查。后期檢查包括哪些細(xì)節(jié)呢?下面給大家一一介紹。

1、布局

(1)IC不宜靠近板邊。

(2)同一模塊電路的器件應(yīng)靠近擺放。比如去耦電容應(yīng)該靠近IC的電源腳,組成同一個(gè)功能電路的器件優(yōu)先擺放在一個(gè)區(qū)域,層次分明,保證功能的實(shí)現(xiàn)。

(3)根據(jù)實(shí)際安裝安排插座的位置。插座都是引線到其他模塊的,根據(jù)實(shí)際結(jié)構(gòu),為了安裝方便,一般采用就近原則,安排插座的位置,而且一般靠近板邊。

(4)注意插座方向。插座都是有方向的,方向反了,線材就要重新定做。對于平插的插座,插口方向應(yīng)該朝向板外。

(5)Keep Out區(qū)域不能有器件。

(6)干擾源要遠(yuǎn)離敏感電路。高速信號、高速時(shí)鐘或者大電流開關(guān)信號都屬于干擾源,應(yīng)該遠(yuǎn)離敏感電路,比如復(fù)位電路,模擬電路。可以用鋪地來隔開它們。

2、布線

(1)線寬大小。線寬要結(jié)合工藝、載流量來選擇,最小線寬不能小于PCB廠家的最小線寬。同時(shí)保證承載電流能力,一般以1mm/A來選取合適線寬。

(2)差分信號線。對于USB、以太網(wǎng)等差分線,注意走線要等長、平行、同平面,間距由阻抗決定。

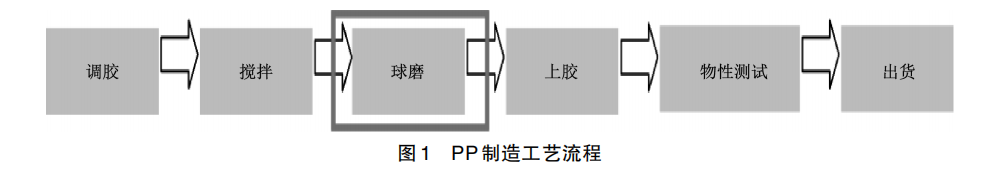

(3)高速線注意回流路徑。高速線容易產(chǎn)生電磁輻射,如果走線路徑與回流路徑形成面積過大,就會形成一個(gè)單匝線圈向外輻射電磁干擾,如圖1。所以走線的時(shí)候要注意旁邊有回流路徑,多層板設(shè)置有電源層和地平面可以有效解決這個(gè)問題。

(4)注意模擬信號線。模擬信號線應(yīng)該與數(shù)字信號隔開,走線盡量避免從干擾源(如時(shí)鐘、DC-DC電源)旁邊走過,而且走線越短越好。

3、元件封裝

(1)焊盤間距。如果是新的器件,要自己畫元件封裝,保證間距合適,焊盤間距直接影響到元件的焊接。

(2)過孔大小(如果有)。對于插件式器件,過孔大小應(yīng)該保留足夠的余量,一般保留不小于0.2mm比較合適。

(3)輪廓絲印。器件的輪廓絲印最好比實(shí)際大小要大一點(diǎn),保證器件可以順利安裝。

4、EMC和信號完整性

(1)端接電阻。高速線或者頻率較高并且走線較長的數(shù)字信號線最好在末端串入一個(gè)匹配電阻。

(2)輸入信號線并接小電容。從接口輸入的信號線,最好在靠近接口的地方并接皮法級小電容。電容大小根據(jù)信號的強(qiáng)度以及頻率決定,不能太大,否則影響信號完整性。對于低速的輸入信號,比如按鍵輸入,可以選用330pF的小電容,如圖2。

(3)驅(qū)動能力。比如驅(qū)動電流較大的開關(guān)信號可以加三極管驅(qū)動;對于扇出數(shù)較大的總線可以加緩沖器(如74LS224)驅(qū)動。

5、絲印

(1)板名、時(shí)間、PN碼。

(2)標(biāo)注。對一些接口(如排陣)的管腳或者關(guān)鍵信號進(jìn)行標(biāo)注。

(3)元件標(biāo)號。元件標(biāo)號要擺放至合適的位置,密集的元件標(biāo)號可以分組擺放。注意不要擺放在過孔的位置。

6、其他

Mark點(diǎn)。對于需要機(jī)器焊接的PCB,需要加入兩到三個(gè)的Mark點(diǎn)。

責(zé)任編輯:ct

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4670瀏覽量

85294 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

42983

發(fā)布評論請先 登錄

相關(guān)推薦

以太網(wǎng)PHY PCB設(shè)計(jì)布局檢查清單

PCB設(shè)計(jì)與PCB制板的緊密關(guān)系

電路仿真和PCB設(shè)計(jì)軟件

PCB設(shè)計(jì)的EMC有哪些注意事項(xiàng)

如何應(yīng)對PCB設(shè)計(jì)中信號線的跨分割呢?

PCB設(shè)計(jì)中的常見問題有哪些?

多層pcb設(shè)計(jì)如何過孔的原理

PCB設(shè)計(jì)阻抗不連續(xù)的原因及解決方法

PCB設(shè)計(jì)優(yōu)化丨布線布局必須掌握的檢查項(xiàng)

PCB設(shè)計(jì)工作中常見的錯(cuò)誤有哪些?

半固化片制造過程中填料球磨工藝變更對PCB漲縮的影響

后期檢查在pcb設(shè)計(jì)過程中有多重要

后期檢查在pcb設(shè)計(jì)過程中有多重要

評論