隨著納米幾何尺寸的生產設計數量的增加,信號完整性(SI)已從一些前沿設計師的關注發展成為一個普遍的噩夢適合所有設計師。

雖然已經發展了幾種方法來解決這些SI挑戰,但是在130納米以下的幾何形狀中,意外電氣效應和迅速增長的設計復雜性的匯合導致了指數SI報告的違規行為。因此,設計受到延長的設計時間表的影響,并且通常會錯過市場窗口。

延長130納米以下設計周期的一個關鍵因素不僅是噪聲靈敏度的提高,而且還有一些SI閉包方法中存在的過度悲觀情緒,特別是SI分析引擎。雖然需要合理的余量來構建必要的保護帶以幫助設計人員充滿信心,過度的悲觀情緒會大大增加設計周期并導致過度設計。

過度設計通常會導致擁堵增加,從而影響產量,增加功率,包括泄漏和#151; 90納米及以下設計的主要問題。

這種過度悲觀主義大部分來自用于估算SI的基礎模型以及用于簡化分析過程的一些權衡。然而,通常,由于過度修復和過度約束設計實現,分析中的快捷方式導致更多的設計迭代。因此,在選擇SI閉包或分析解決方案時,應特別注意確保對錯誤違規進行充分過濾。

2Noise-glitch假失敗過濾

SI分析將確定由于切換相鄰攻擊者網絡而在給定受害者網絡上可能發生的最壞情況故障。在毛刺分析期間,有許多技術可用于過濾悲觀情緒,例如使用邏輯關系和時序窗口來確定可以同時切換的攻擊者網絡集。

這種類型的過濾通常會將毛刺違規次數減少兩到三倍。下一級過濾確定計算的故障是否可能導致功能違規。

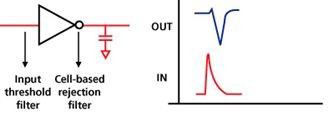

最基本的毛刺檢查是根據預定義的閾值電壓(電源的40%)檢查毛刺的高度。這種方法通常會產生數以千計的違規行為,其中絕大多數都是錯誤的(見圖1)。

這是因為CMOS邏輯門充當低通濾波器,因此大多數噪聲毛刺被接收邏輯門衰減。如果噪聲在到達存儲元件(如觸發器或鎖存器)之前被抑制,則不會導致功能問題。

圖1&#151 ;基本噪聲干擾濾波

第二級故障濾波超出了簡單的噪聲峰值閾值濾波。它是基于單元的拒絕,依賴于毛刺在通過一個邏輯階段傳播時的行為方式。基于單元的拒絕確定接收器輸入處的噪聲是否會傳播到輸出。

檢查細胞排斥有兩種方法。一種是使用預先表征的拒絕曲線,另一種是利用相關的寄生效應對接收機進行實時仿真,以了解它在存在計算的噪聲時的行為。

后一種方法更加真實,并且會過濾更多違規行為,因為前一種方法必須使用毛刺的悲觀近似作為等腰三角形。然而,雖然基于單元的拒絕通常會比輸入峰值檢查減少5-10倍的噪聲干擾,但這種方法在低于90納米的幾何尺寸下耗盡了蒸汽,并且仍然報告了許多不一定構成任何問題的悲觀故障。設計問題(見圖1)。

3高級毛刺濾波

噪聲傳播擴展了基于單步的基于單元的抑制方法,并在多個邏輯門之間傳播SI毛刺以注冊端點。允許這些毛刺與沿路徑的其他串擾引起的毛刺相結合。

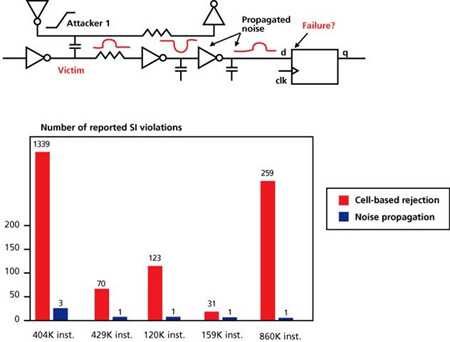

實際上,只有那些大到足以導致順序元件(鎖存器/觸發器)發生功能故障的毛刺才會被標記。幾個真實的客戶設計已經證明,使用噪聲傳播與基于單元的抑制相比,報告的SI毛刺數量顯著減少,通常為一個或兩個數量級(參見圖2)。

圖2 - 噪聲傳播和毛刺悲觀減少

噪聲傳播通過邏輯門傳播毛刺并檢查確保功能有效性寄存器不是不穩定的。與傳統方法相比,噪聲傳播到寄存器端點可將誤判數量減少一個數量級。

噪聲傳播最好通過即時晶體管級仿真實現,而不是通過預先表征傳播表。傳播表不能準確地考慮噪聲源的組合,例如在多個輸入處具有毛刺的單元,或傳播噪聲,電源噪聲(IR降或接地反彈)和串擾的組合。

當毛刺通過接收器傳播時,它會動態降低接收器的保持強度,使其對輸出端的串擾更加敏感。此外,傳播表的表征是繁瑣的,通常需要數周時間來創建必要的數據以涵蓋所有可能的輸入毛刺場景。

4SI延遲減少悲觀

雖然邏輯和時序窗口的使用將減少SI延遲計算的悲觀性,但由于SI而具有幾納秒的額外負余量并不罕見。因此,在存在SI的情況下關閉時間是非常具有挑戰性的。很多SI延遲悲觀主義是由于悲觀的時序窗口迭代,噪聲轉換(轉換)的表示和傳播,以及攻擊者和受害者網絡的對齊方式。

5定時窗口迭代

由于SI延遲變化取決于時序窗口,時序窗口取決于SI,因此精確分析需要在SI延遲計算和靜態時序分析之間進行迭代。加速SI分析的一種常用技術是首先計算SI延遲效應(忽略時序窗口),然后僅在關鍵路徑上進行迭代。然而,這種加速會增加悲觀情緒,因為非關鍵網絡的時間窗和時滯會被高估。因此,非關鍵網絡攻擊關鍵網絡的影響也將是悲觀的,并導致過度的延遲變化。

更好的方法是從標稱時序窗口開始,對所有網絡執行快速迭代,逐步重新計算時序窗口發生變化的網絡。這樣,用于最終SI延遲變化計算的所有網絡都使用實際的時序窗口和轉換。

6SI轉換傳播

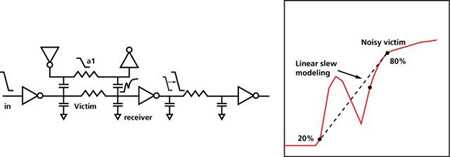

大多數時序和SI分析儀使用線性斜坡來模擬轉換,但這對于具有顛簸非線性轉換的噪聲網絡來說并不是一個很好的近似。線性斜坡往往更加悲觀,特別是如果它們以相同的方式測量轉換,以用于噪聲和非噪聲轉換。使用傳統測量(例如20-80%的電源)將極大地高估噪聲轉換對下游邏輯路徑的影響。

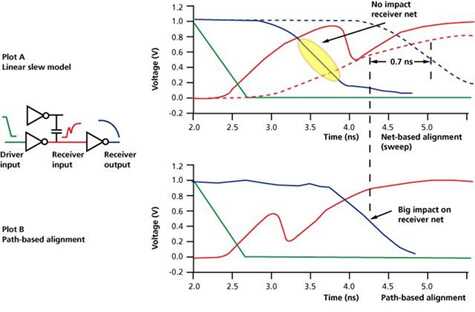

例如,在圖3中,攻擊者A1定時在受害者切換為高電平的同時切換為低電平,從而導致SI引起的路徑延遲增加。由此產生的紅色凹凸上升波形很難用線性回轉模型精確建模。

如果轉換閾值是Vdd的20-80%,則會報告大的轉換退化,導致下游路徑上出現相當大的延遲悲觀。所需要的是SI延遲方法,其準確地考慮接收器輸出的有效轉換影響。

圖3—由于線性回轉造型不足造成的悲觀情緒

另一個錯誤來源是受害者網絡的驅動模型。通常,驅動程序使用2D表進行建模,其中表具有一組輸入轉換和輸出負載。

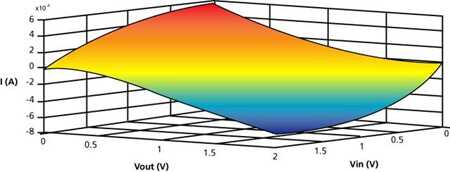

但是,將開關波形映射到相應的轉換值是“多對一”映射。換句話說,可能存在具有相同轉換值的許多不同波形。受串擾影響的開關波形恰好存在這種情況,導致不準確的串擾路徑延遲。為了精確地模擬這樣的波形,基于電流源需要更精確的驅動器模型,或者在非線性波形的情況下,基于驅動器的實際晶體管。如圖4所示,基于電流的延遲模型獨立于特征化的“良好表現”的轉換值,有助于消除傳統延遲表的不準確性。給定任意輸入波形,它可以精確計算接收器門輸出的延遲。

圖4—延遲測量和基于電流的延遲模型

接收器輸入和輸出的轉換和延遲的精確計算可以通過基于電流的延遲模型來實現,該模型將輸出電流表征為輸入和輸出電壓以及內部電容的函數,包括米勒電容。

攻擊者的位置

受害者的延遲根據攻擊者的相對切換時間,網絡可能會發生很大變化。 SI延遲分析將確定對齊攻擊者所造成的最壞情況延遲變化,同時尊重受害者和攻擊者時間窗口施加的約束。

然而,這種方法存在兩種悲觀來源。首先,最壞情況的攻擊者/受害者對齊可能發生在受害者的時間窗口的中間,因此可能不會改變其前沿或后沿到達時間。其次,受害者網絡的最壞情況延遲可能是由于過渡后沿的噪聲而發生的 - 太遲而無法影響接收門。

為了解決第一個悲觀來源,攻擊者對齊應該找到最大化受害者時間窗口擴展的,同時應該拒絕其他對齊。即使是那些產生較大延遲但對時序窗口影響較小的那些。

為了解決悲觀的第二個來源,應在接收器輸出而不是輸入端進行SI延遲測量,以確保攻擊者的對齊確實會對下游邏輯產生最大的影響。這種稱為基于路徑的對齊(見圖5)的技術消除了局部的基于網絡的最壞情況結果(局部最大值),而是提供了考慮下游路徑的全局最壞情況結果(全局最大值) )。

圖5—基于路徑的對齊和SI延遲悲觀減少

如圖5中的情節A所示,傳統對齊會在接收器輸入的波形尾部產生噪聲沖擊(紅色),但是這對接收器輸出波形(藍色)沒有影響。然而,線性回轉模型將接收器輸入波形解釋為點紅色波形,這導致悲觀接收器輸出點藍色波形。

在圖B中,基于路徑的對齊導致最壞情況的接收器輸出波形(藍色),這是由受害者網絡上更早的攻擊者對齊引起的。請注意,接收器輸出波形中沒有可感知的壓擺性能下降。最終結果是線性回轉模型的路徑延遲悲觀減少了700ps。

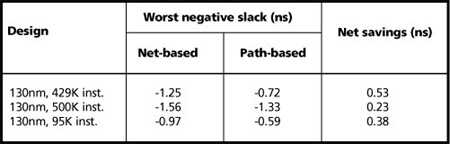

基于路徑的對齊已經證明,在幾種工業設計中,SI對延遲的不良悲觀情緒顯著減少(見表1)。

表1—基于路徑的對齊悲觀減少結果

表1比較了三種130nm設計中基于路徑的對齊與最差情況下基于網絡的對齊的使用。當使用基于路徑的對齊時,最壞情況下的負松弛顯著減少,使得更容易實現SI閉合。

基于路徑的對齊的另一個好處是它能夠利用接收器的固有濾波,以便在明確定義的平滑接收器輸出上執行轉換和延遲測量。即使對于毛刺幅度大于電源電壓一半的非常崎嶇的波形也是如此。因此,接收器輸出上的壓擺測量也不那么悲觀。非常重要,因為它影響下一個邏輯階段的延遲。

8結論

隨著工藝技術的縮小,潛在的SI問題的數量非線性增加。這使得設計閉合幾乎無法實現,除非工程師采用使用先進濾波技術(如噪聲傳播和基于路徑的對齊)的精確SI分析。這些技術將使設計人員能夠處理少數真實的SI違規行為,按時完成設計項目并按時交付。

期待65納米工藝及以下工藝將需要在減少SI分析悲觀主義方面取得進一步進展。特別是,需要基于統計和概率的技術來逼真地處理片上工藝變化,并且沿著長關鍵路徑的最壞情況SI延遲的不可能累積增加。

責任編輯:ct

-

pcb

+關注

關注

4318文章

23022瀏覽量

396426 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42990

發布評論請先 登錄

相關推薦

怎樣減少信號完整性悲觀

怎樣減少信號完整性悲觀

評論