在PCB設計中,如何區分高速信號與低速信號?很多人有一個誤區,一般認為頻率高的信號就是高速信號,對于GHz這樣的信號來說無可厚非,但卻不能一概而論。

凡是大于50MHz的信號,就是高速信號;

信號是否高速和頻率沒有直接關系,而是信號上升/下降沿小于50ps時就認為是高速信號;

當信號所在的傳輸路徑長度大于1/6λ,信號被認為是高速信號;

當信號沿著傳輸路徑傳輸,發生了嚴重的趨膚效應和電離損耗時,被認為是高速信號。

所以說高速信號并不是以頻率高低來界定的,那么應該怎樣區分高低速信號呢?

在高速信號的設計中,一般考慮的并不是信號的周期頻率F,一般是有效頻率F1,T代表信號的時鐘周期,T1代表信號的10%-90%的上升時間,則有:

周期頻率定義:F=1/T

有效頻率定義:F1=0.5/T1

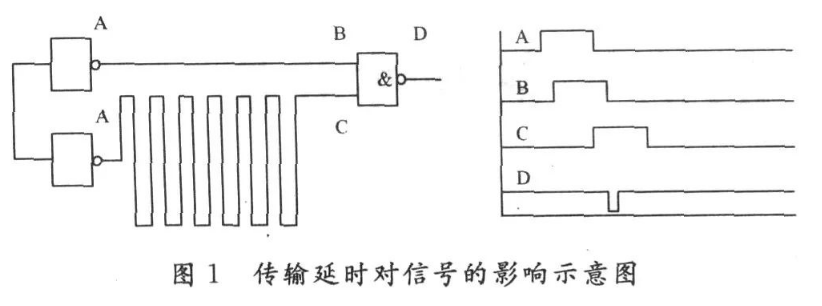

低速信號中,各個點的電平相差不大,但高速信號中,需要用分布式的思維來考慮問題,在傳輸路徑中,每個點的路徑相差很大,所以高低速信號的劃分還與信號的傳輸路徑有關。

信號的傳輸長度小于信號波長的1/6時,可認為是低速信號,反之高速。λ是信號波長,c是信號在PCB上傳輸速度,F是信號的有效頻率。

λ=c/F

在C為常數的情況下,λ與F成反比,即頻率F越高,波長越短,可以劃分的高低速信號線的分水的線長越短。

總結:高速信號與低速信號的區分方法

1、獲得有效頻率F1及走線長度L

2、利用有效頻率F1計算信號的波長λ

3、判斷L與1/6*λ的大小關系,L大為高速信號,反之為低速。

補充:一般有效頻率可以由專業儀器測量得到,也可以估算,可假設上升沿為信號周期的7%,假如信號頻率是10MHz,可以假設有效頻率是70MHz。

-

pcb

+關注

關注

4318文章

23022瀏覽量

396428 -

高速信號

+關注

關注

1文章

223瀏覽量

17677

原文標題:干貨| PCB設計中高速信號與低速信號的區分

文章出處:【微信號:eqpcb_cp,微信公眾號:快點兒PCB學院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速pcb與普通pcb的區別是什么

高速PCB設計,信號完整性問題你一定要清楚!

stm32的高低速外設是怎么區分的?

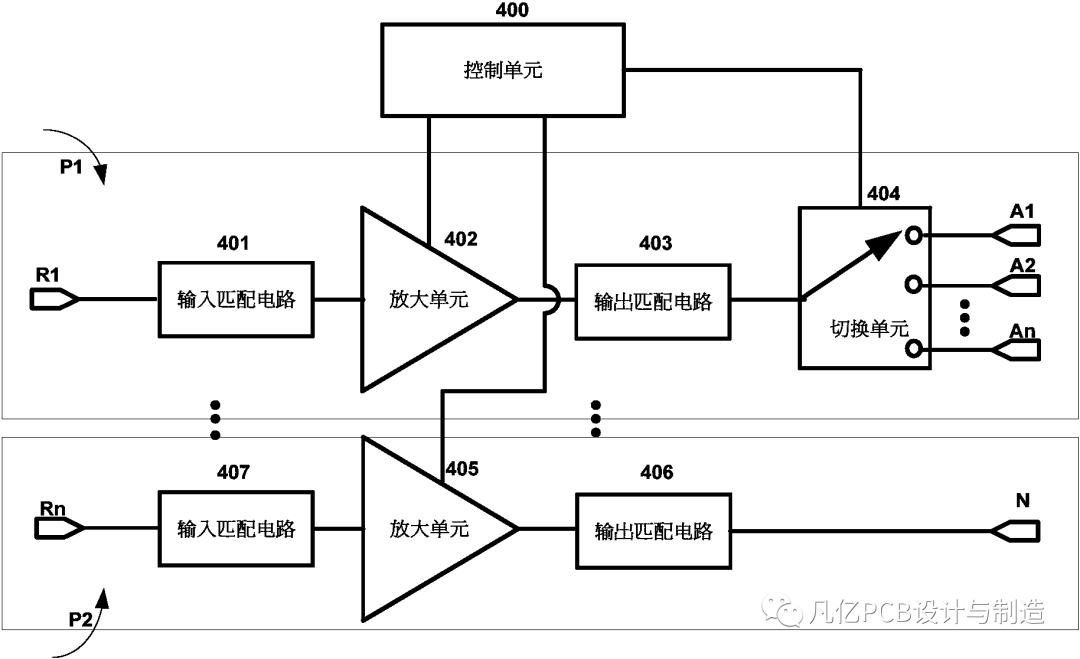

分析高速數字PCB設計信號完整性解決方法

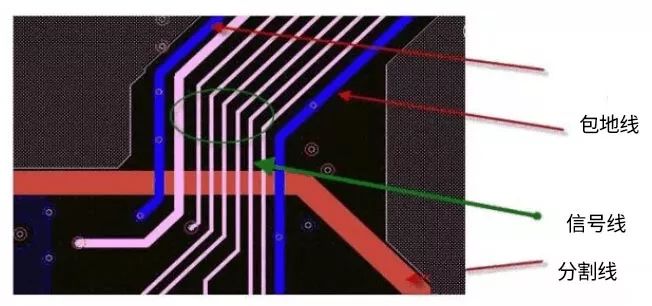

高速PCB信號走線的九大規則

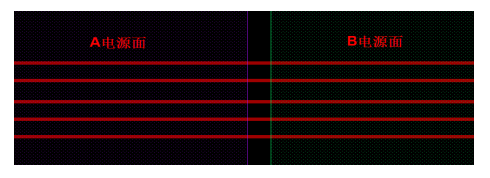

PCB設計信號線跨分割會有什么影響

混合信號PCB設計問題

詳解PCB設計中高速背板設計過程

在高速電路設計中,如何應對PCB設計中信號線的跨分割

PCB設計中高速信號與低速信號如何區分

PCB設計中高速信號與低速信號如何區分

評論