每當我們在PCB上從一個數字集成電路向另一個發送信號時,我們就需要改變信號的狀態。這種狀態的變化和其伴隨的電磁場的變化可以描述為一種在電路中移動的波。波是一種將能量從一個位置通過導線的引導,傳遞到另一個位置的現象。

當導線的電位發生變化時,導線周圍的磁能會發生變化

當電磁波從一種介質傳播到另一種介質的邊界時,就會產生反射噪聲。當波與邊界相交時,一部分能量會作為信號傳輸,另一部分能量會被反射回來。

當波從一種介質傳播到另一種介質時,

并非所有能量都被傳輸,會有一部分能量被反射回其源頭

對于電氣工程師來說,通常會把這種邊界出現的介質叫做電阻抗來,也就是說,邊界是阻抗發生變化的地方。

阻抗由電阻和電抗元件組成,電阻以熱的形式耗散電路的能量。電路中的可回收能量存在于電磁場中,電磁場滲透并包圍著導體、電感器和電容器。

當電路中的阻抗發生變化時,就會發生一定程度的反射。反射波將返回到下一個邊界(阻抗變化的位置)并再次發生反射。

這幅一維波圖顯示了兩點之間反射的波脈沖,能量隨時間/距離衰減

該過程將無限期地持續,直到能量被電路吸收或消散到環境中。

為什么反射噪聲是一個問題

對于信號線而已,你的驅動器和接收器上都會有反射點。工程師的工作就是通過阻抗匹配來最小化反射信號的數量和最大化傳輸信號的數量。

如果上述情況不能實現,額外積累的能量需要在淹沒一個有噪聲的信號之前消散。

如果反射脈沖的能量在下一個脈沖產生之前沒有消散,能量將積累并疊加。幸運的是,信號通過電阻元件時能量會衰減。所以一個簡單的串聯電阻是可以消除大部分噪聲的。

評估數字信號中的噪聲

傅立葉定理告訴我們,任何波或波脈沖都可以分解成一系列正弦波和/或余弦波。如果上升/下降的時間足夠短,一個脈沖就可以容納幾十個小振幅波。

在下圖中,可以看到無阻尼數字信號轉換邏輯狀態從低到高。

它捕捉到的無阻尼數字信號(黃色,通道1)

看下面的圖像,左邊的圖像顯示了一個復合波脈沖,它是通過原始波的振幅奇次諧波的連續疊加而產生的,我們可以將波形分解為一系列正弦波。

如果你真的設法制造駐波,那將會制造出巨大的噪聲源,可以壓倒附近的任何信號線。

這幅圖顯示,在特定波長上反射的波(橙色)可以與反射波(藍色)結合,形成高振幅駐波(綠色)。這種現象會發生在1/2波長的奇數整數倍處,波長是軌跡長度的兩倍。

如何降低反射噪聲

在設計中,有幾種方法可以用來調整反射噪聲。下面是一些你可以使用的技術的概述:

一、保持恒定阻抗

你應該考慮的第一件事是如何盡可能保持跟蹤的恒定阻抗。請記住:阻抗變化時會發生反射。

計算記錄道的阻抗

為了保持恒定的阻抗,你需要能夠計算跡線的阻抗。你的PCB程序應該允許你這樣做,但也有在線工具可用。一旦你確定了你的軌跡和空間寬度,就沿著你的路線保持住。

跨記錄道一致性

為保持差分對或單端走線的恒定阻抗,必須保持恒定的走線寬度,恒定間距以及與所有其他導線的恒定間隔。如果使用隨機跡線在阻抗控制對上進行路由,則將更改阻抗并創建反射點。

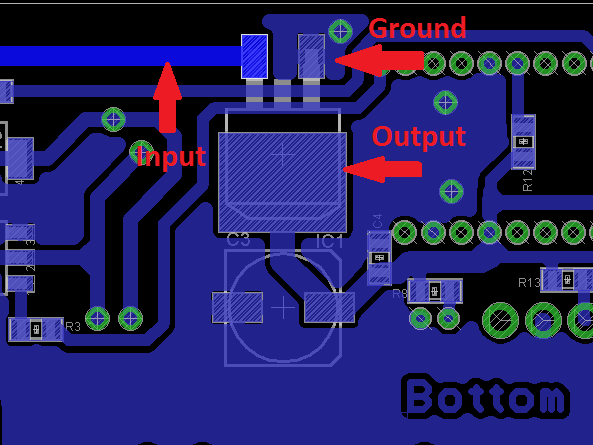

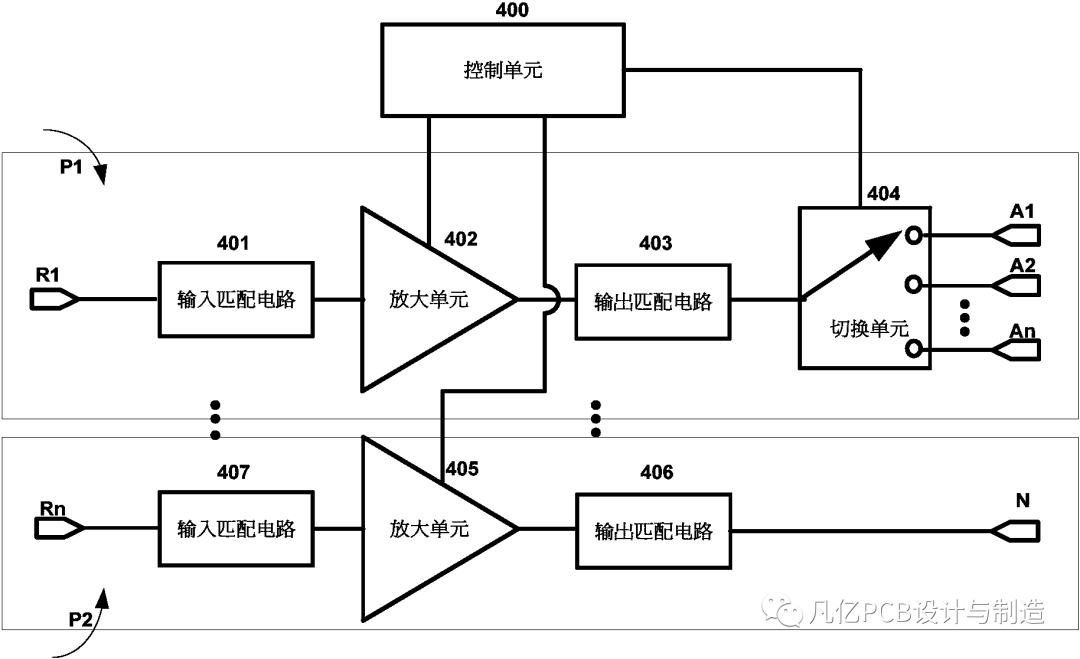

在阻抗變化的地方使用阻抗匹配電路

當你必須改變阻抗(例如從線性放大器到天線)時,使用阻抗匹配電路(用史密斯圖表、在線工具等計算)。

二、減少反射點

你還可以首考慮如何減少反射點的出現。

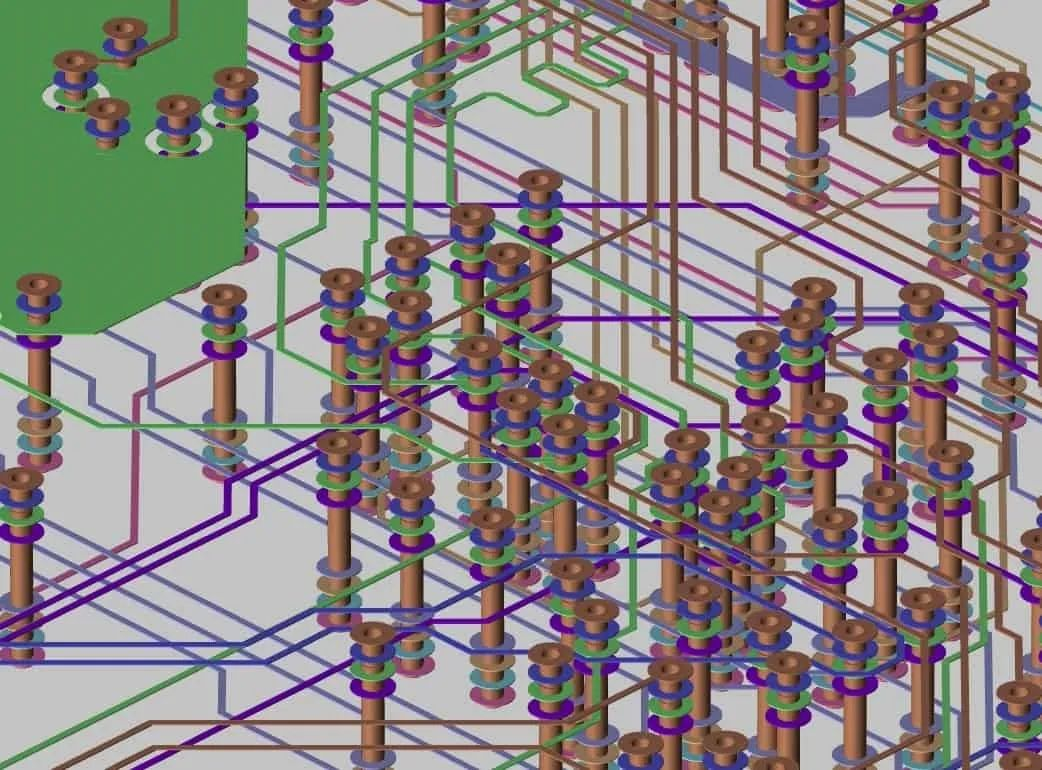

在板的邊緣觀察你的通孔

通孔可能是高速電路設計者的一個問題。如果通孔延伸到信號軌跡以外的未使用層,電路的阻抗會突然改變。在電路板邊緣的轉換處,當記錄道離開VIA(~50-150Ω)進入空氣(~377Ω)時,會出現阻抗不匹配。這會在該位置創建一個反射點,從而嚴重降低信號。

向后鉆你的通孔

解決方案是讓你的PCB制造商“反鉆”你的通孔,以從未使用的外層板上移除通孔,反鉆通孔顯著改善了邏輯轉換。

Sanmina Sci背面鉆孔過孔的圖像

三、減輕現有反射噪聲

使用阻尼電阻

另一項重要技術是在所有驅動信號源附近串聯使用阻尼電阻,并可以快速上升/下降。這通常被稱為緩沖電阻器。

發生的任何信號反射都將通過電阻快速衰減。這些電阻通常小于100Ω,靠近驅動信號源(例如,時鐘源、GPIO等)。

一般的想法是創建一個阻尼電路,在這個電路中,信號上升到適當的邏輯電平一次,沒有過度的波動。

-

pcb

+關注

關注

4317文章

23006瀏覽量

396299 -

電磁波

+關注

關注

21文章

1443瀏覽量

53747

原文標題:如何消除PCB設計中的反射噪聲[20190428]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB設計中的爬電距離:確保電路板安全可靠

pcb設計中如何設置坐標原點

精益思維在PCB設計中的應用實踐

PCB設計與PCB制板的緊密關系

儲能PCB設計與制造思考 探討儲能PCB設計與制造中的關鍵要素

PCB設計中的反射噪聲怎樣消除

PCB設計中的反射噪聲怎樣消除

評論