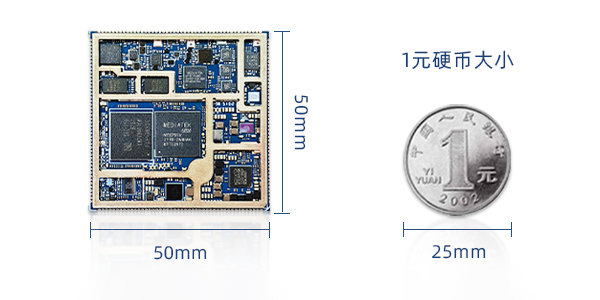

昨天,聯發科(MediaTek)曝光了其首款集成5G調制解調器的7nm SoC,采用ARM Cortex-A77 CPU 核心、以及 Mali-G77 GPU。

據了解,MTK 首顆 5G SoC 采用了臺積電的 7nm 制程,集成了聯發科自家的 Helio M70 調制解調器。

這款基帶支持 6GHz 以下的 5G NR 頻譜、高達 2x 的載波聚合、以及獨立 / 非獨立的 5G 網絡架構。全球首款采用先進7nm工藝的5G 芯片,在極小的封裝中實現大幅節能。高速吞吐:峰值吞吐量達到4.7Gps下載速度(Sub-6GHz頻段),支持新空口(NR)二分量載波(CC),支持非獨立(NSA)與獨立(SA)5G組網架構。強大的多媒體與影像性能:支持60fps的4K視頻編碼/解碼,以及超高分辨率攝像機(80MP)。

那么研發一款類似的芯片需要多少錢?

芯片代工行業在制程邁入10nm以內后,面臨的成本壓力也越來越高。據SemiEngineering報道,IBS的測算顯示,10nm芯片的開發成本已經超過了1.7億美元,7nm接近3億美元,5nm超過5億美元。如果要基于3nm開發出NVIDIA GPU那樣復雜的芯片,設計成本就將高達15億美元。而上面所提到的聯發科開發的是一款既有ARM CPU又有基帶處理部分的SoC芯片,上面用到了眾多的IP核和復雜的異構工藝部分,甚至比NVIDIA GPU還要復雜。我們試著分析一下成本。

1、流片費用:7nm FinFET工藝流片費用約3000萬美金(參考下面麒麟990流片費用,同時兼顧考慮聯發科與臺積電同屬***地區,可能有優惠),合2億人民幣;根據業內人士@手機晶片達人在微博上的爆料稱,麒麟990處理器目前正在用臺積電7nm Plus EUV的工藝設計中,預計將在明年第一季流片。同時這位業內人士還表示,此次麒麟990處理器僅流片費用就高達3000萬美金,足以表明華為的決心。

上面提到的FinFET工藝,其實就是華人科學家胡正明教授發明的(胡正明教授還提出了著名的BSIM模型)。也是為了解決芯片做到更小尺寸的一種方法,據說16nm FinFET工藝的價格,不管芯片的面積有多大,起步價500萬美金。

2、IP授權購買費:主要是購買了ARM最新的Cortex-A77CPU、Mali-G77GPU授權,估計其他一些小的模塊應該也有購買的,如音視頻編解碼器什么的。按生命周期5000萬顆算,各種ip授權購買費按每顆40元算,這大概20億。單ARM CPU授權一項,據悉,每次約1億美金。

3、自研部件費用:聯發科這款5G SoC 集成了自研的最先進的獨立AI處理單元APU完全保證用戶對于5G網絡環境下手機的使用需求。除比較復雜的APU外,自研部件還包括多模通訊基帶(2G3G4G5G等),相機isp,各種控制開關,微核等。這部分很難估算,而且是長期的研發的成果。這部分成本暫復算為10億人民幣。

4、高通專利費:按5000萬顆算,每顆交10元,合5億人民幣。

5、研發工程師工資獎金。1000名工程師每年按50萬計算,3年合計15億。

以上各項共計2+20+10+5+15=52億人民幣。而這些還不包括架構開發,生態構建等的費用。

也許大家覺得這種復雜的SoC芯片比較特殊,需要花費的成本價當然比較高。那么咱們可以看一下一款普通的NAND FLASH控制器芯片需要多少錢才能開發出來?

研發一款商用的普通NAND FLASH接口控制器芯片需要多少錢?

大家知道,NAND FLASH控制器芯片其實功能很單一,僅僅只是通過PCIe接口按照NVMe之類的協議來把指令交給FLASH芯片,同時把數據在HOST主機和FLASH芯片及DDR上搬來搬去而已。

下圖來自于實際商用NAND FLASH產品宣傳時的PPT,從圖中可以看出,開發一顆NAND FLASH主控芯片前期投入(軟件、硬件、IP及人力和時間費用,軟件工具費,設計服務費及儀器測試費用等)的開發費用折合人民幣約為1.35億人民幣,而后期流片、封測等費用為2200萬元人民幣,共計約1.57億人民幣。

2018年,NAND Flash正式進入3D制程發展,其相關控制芯片之晶圓制造制程則在近兩年正式進入1x納米時代,因此NAND Flash控制芯片的設計愈加復雜、所需要運用的人力及資金等資源耗費較市場成長的幅度高,以目前全球PCIe規格效能跑分評鑒最佳的群聯電子SSD控制芯片PS5012-E12來看,該顆芯片的成功除了累積數十年的功力外,在研發人力、時間、設計工具、晶圓先進制程光罩費、3D NAND驗證費…等等資源全數換算為可被評價的費用,總計超過1.55億人民幣。

有同學可能說,如果做更簡單的芯片呢?沒有上面所說的購買IP、人力成本、甚至軟件成本都不考慮,自己寫RTL代碼,自己做后端版圖,那么剩下的最大的成本恐怕就剩下流片了。當然,這種情況在高校和一些研究機構可能存在。軟件工具如果按照市場價格從仿真、綜合到后端布局布線,每一步驟都有相應的軟件,而這些軟件LICENSE的使用費用(主要是Cadence和Synopsys等之類的工具),每一種半年的LICENSE使用費用都在100萬人民幣以上(只是一個key的價格,多個人還需要買多個)。 所以,從上面的兩個例子來看,華為海思十年間在芯片上投入的資金就達到3940個億,這個近4000億的投資多嗎?

不多。

流片費用是成本里較大的組成部分

工藝進入28nm后,芯片的流片成本成指數級增長。“如果說2014年開一個28nm的芯片200-300萬美元對很多公司來說已是不堪重負,那么,未來,開一款16nm的芯片成本將在千萬美元左右,而開一款10nm的芯片,從現在各項投入來看,可能需要達到1.3億美元。”在“2014上海FD- SOI論壇”上,芯原微電子公司技術市場和應用工程師資深總監汪洋說道。不過,盡管如此昂貴,他透露國內仍有一些真土豪提出要開16nm的芯片,主要是那些為挖金幣而定制的處理器芯片。

幾年前,采用不太先進的16nm工藝,流片費用需要1500萬美金以上。

如果是這兩年,采用7nm的工藝,流片費用需要準備1-3億美金以上。

而十年前,海思給出的平均每顆商用芯片的研發成本僅為4000萬人民幣。

這里面有太多太多的原因。要研制出一塊芯片很容易,但是要在控制溫度、成本以及功耗的情況下實現量產,卻不是一件容易的事,換句話來說,就是芯片制造一共有兩個難點,首先就是在試驗階段投入的資金非常的高昂,一次大概需要10萬塊錢,從設計到加工的過程中走過的工序差不多就有3000到5000道,而且一次耗費的時間差不多就是一年,在時間和金錢的制約下,對于其精度的要求是極其的高。其次就是排錯難度大,雖然芯片看上去的體積非常小,但是在上面卻分布著數億個晶體管,可以被檢測出來的信號最多也就只有幾百條,能夠看到如果哪條晶體管出了差錯,那都是難上加難!除了這些技術方面的原因之外,還有國際因素,因為有專利權和出口協定的管控,因此我們想從一些擁有芯片技術的老牌國家中獲取先進的技術根本是不可能的事情,而且中國每年進口一臺相關的儀器,其中的專利費就高得嚇人,像前段時間買入中國的阿斯麥光刻機,一臺價值就要8億元!

當然,如果想辦法,做芯片還是有不少省錢的辦法的。不用買IP,在高校里面找廉價的學生來設計(沒有研發成本),租用高校里面的EDA工具,自己從RTL代碼一直坐到GDSII,再采用便宜的MPW,選擇非常古老的工藝線,不用量產,僅做做實驗,那么計算下來一顆芯片流片一次的費用也至少需要幾十萬元人民幣。如果是項目要用的稍微復雜一點的芯片,那么一次流片至少也需要幾百萬人民幣。如果一次流片后還有BUG,再流片的話還得花費五六百萬,如此反復的燒錢。

可做芯片成本這么高,聽說有的地方的學生學一門課,然后全班的學生都可以自己做出來一顆芯片來交作業?

高校里上一門課然后布置所有學生都做出一顆芯片的作業現實中存在嗎?

是存在的。

有人曾經看到過***的大學芯片專業的學生全班同學都可以流片,好像覺得流片跟做個PCB板子差不多一樣,其實不是這樣的。***有個組織叫CIC(國研院晶片中心),只針對***的業界、學術界有優惠,CIC設立的初衷就是為***的IC產業提供良好的服務和保障,TSMC 28nm工藝的,小面積下大約是23.5萬人民幣每平方毫米;45nm大約是12萬人民幣每平方毫米(CIC公開報價)。其實毫米非常小,做芯片隨隨便便就有N個平方毫米。前面所說的全班都可以流片的就是TSMC的180nm工藝線(教育線),比如平時大學本科的模電課,一學期上完了,全班都可以申請流片做個放大器什么的,畢業設計就更不用說了。這個教育線在***地區幾乎是免費的。所以,幾乎可以人人做芯片,這也是為什么***地區的芯片設計和制造比較厲害的關鍵原因。

這種把流片當做跟吃飯一樣隨便的地方澳門也有。

比如,IEEE fellow,IET fellow、中國科學院海外特聘專家,現任澳門大學教授、微電子研究院副院長、模擬與混合信號超大規模集成電路國家重點實驗室副主任麥沛然教授課題組。

3年21篇ISSCC頂級會議論文,憑什么?

除了自身實力之外,憑的就是不斷的流片實驗的經驗積累。培養幾屆學生專盯某一個具體的點,工作具有良好的延續性。精心設計,用先進工藝,測試結果的優勢就出來了。而且,芯片小,一個學生就可以負責一顆,一方面可以用心打磨,另一方面可以快速出多篇優化方案。選擇小點突破,為工程準備預案。如果咱們也有這樣的環境和條件,流片如吃飯般容易,是否也可以做成這種效果?仔細想想,似乎不難,就針對某種電路往死里優化,先仿真出來,再去流片驗證,是不是也不難啊?電路結構千千萬,即便是數字的,如果有這種燒錢的條件,肯定會有一兩個點會突破的。難就難在流片費用太高,資金不足。

說實話,大陸高校里面每年能有一兩次流片機會的高校都屈指可數,更別提如上面的例子中根據需要盡情的流片的高校是完全不存在。當然,國內還是有不少渠道能夠減免一些流片費用的,比如去年中興事件后,各地政府部門出臺的一些扶植芯片的政策,有的地方甚至可以申請免費流片(其實費用是政府部門出了)。

希望今后大陸的集成電路制造業也能夠飛速發展,至少讓教育界的老師和學生們能夠實現“流片自由”。

附錄:芯片是一層一層長出來的

CPU芯片的成本構成是這個樣子滴

1、晶片成本

要制造CPU,第一步是制造晶圓(將晶圓切成小片后即可得到晶片)。晶圓的成分是硅,是地殼內第二豐富的元素(沙子的主要成分就是二氧化硅)。制取晶圓分為三個步驟:

一是制取電子級硅。通過碳和二氧化硅在電弧熔爐中反應得到冶金級硅,再對其進一步提純,將粉碎的冶金級硅與氣態的氯化氫進行氯化反應,生成液態的硅烷,通過蒸餾和化學還原工藝,得到電子級硅,其純度高達99.999999%。

二是制取硅錠。將電子級硅放在石英坩堝中,并用石墨包圍不斷加熱,溫度維持在大約1400℃,爐中充斥著惰性氣體,使電子級硅熔化的同時,不會因化學反應而摻雜雜質。

隨后將一顆籽晶浸入坩堝中,由拉制棒帶著籽晶與坩堝旋轉方向逆向旋轉,采用旋轉拉伸法緩慢將籽晶垂直拉出,熔化的多晶硅會粘在籽晶的底端,最終得到圓柱體的硅錠。

三是切割圓晶。將得到的硅錠橫向切割成圓形的單個硅片,然后進行研磨,將凹凸的切痕磨掉,再用化學機械拋光工藝使其至少一面光滑如鏡。

目前,國際主流采用的是12英寸晶圓。就國內而言,中芯國際和華力微都有12英寸晶圓廠,英特爾、三星、海力士等公司在大陸也有12英寸晶圓廠。

雖然12英寸晶圓廠的投資遠遠大于8英寸晶圓廠,但是晶圓尺寸越大,意味著單片晶圓能夠切割出的芯片越多,芯片成本也就越低。 在設備成本被以億為單位的芯片出貨量平攤后,采用尺寸更大的晶圓,不僅芯片價格可以更具競爭力,還能以細水長流的方式獲取更多利潤。

因此,晶片成本就是以二氧化硅制取晶圓所耗費的資金分攤到每一片晶片后的成本,可以簡單理解為每一片芯片所用的材料(硅片)的成本。

2、掩膜成本

在得到晶圓后,要制造CPU,還要進行以下步驟:

一是濕洗。用各種化學藥劑清洗晶圓,確保晶圓表面沒有雜質。

二是光刻。使用光刻機將激光光束穿透畫著線路圖的掩膜,經物鏡補償各種光學誤差,將電路圖成比例縮小后映射到硅片上,然后使用化學方法顯影,得到刻在硅晶片上的電路圖。

光刻示意圖。最上方的是掩膜,中間的是物鏡,用來補償各種光學誤差,最后將電路圖成比例縮小后映射到硅片上。

三是離子注入。在硅晶片不同的位置嵌入不同的物質,進而形成場效應管(晶體管)。

四是蝕刻。使用刻蝕機將晶片上多余的部分去掉,得到所想要的結構。

五是等離子沖洗。用較弱的等離子束轟擊整個芯片,達到清潔的效果。

六是熱處理。瞬間把晶圓加熱到1200攝氏度以上,然后慢慢地冷卻下來,使得注入的離子能更好地被啟動以及熱氧化,并在晶片中形成場效應管的柵極。

七是氣相淀積。通過物理、化學氣相淀積設備進一步精細處理晶片表面,并給晶片鍍膜。

八是電鍍、化學、機械表面處理。

因此,掩膜成本就是晶片加工成本以及光刻機、刻蝕機、物理、化學氣相淀積設備的折舊成本等等。掩膜成本的高低和制程工藝的關系非常大,像40/28nm的工藝已經非常成熟,成本也低,40nm低功耗工藝的掩膜成本為200余萬美元;28nm SOI工藝為400萬多美元;28nm HKMG成本為600多萬美元。

但在最新的制程工藝問世之初,耗費則頗為不菲。在2014年剛出現14nm制程時,曾有消息稱其掩膜成本為3億美元。

當然,隨著時間的推移和臺積電、三星掌握14/16nm制程,現在的價格應該不會這么貴。英特爾正在研發的10nm制程,根據英特爾官方估算,掩膜成本至少需要10億美元。

新制程工藝之所以貴,一方面是貴在新工藝高昂的研發成本和偏低的成品率,另一方面也是因為光刻機、刻蝕機等設備的價格異常昂貴。

以前道光刻機為例,國內商業化量產依舊停滯在90nm,40/65nm的光刻機雖然取得技術突破,但依舊沒有商業化量產,有可能還處于實驗室狀態。

中芯國際、華力微等晶圓廠的28nm光刻機完全依賴進口,而且價格頗為不菲——ASML主流技術水平的光刻機售價為幾千萬美元,最先進的EUV光刻機問世時售價曾高達1億美元……

光刻機

每片CPU的掩膜成本=掩膜總成本/總產量,因此,如果產量小,CPU的成本會因為掩膜成本而較高,只要產量足夠大,比如每年出貨以億計,掩膜成本被巨大的產量分攤到微乎其微。 3、封測成本

晶圓倒裝機

在晶片完成上述光刻、刻蝕等步驟后,還需要用后道光刻機、減薄機、劃片機、裝片機、引線鍵合機、倒裝機等制造設備給晶片裝個殼,將之前加工好的晶片和基片、散熱片堆疊在一起,最終形成我們日常見到的四四方方、帶針腳和商標的CPU。

封裝成本就是這個過程所需要的資金。在產量巨大的一般情況下,封裝成本一般占硬件成本的5%-25%左右,不過IBM的有些芯片封裝成本占總成本一半左右,據說最高曾達到過70%.。..。.

測試可以鑒別出每一顆處理器的關鍵特性,比如最高頻率、功耗、發熱量等,并決定處理器的等級,比如將一堆芯片分門別類為:i54460、i54590、i54690、i54690K等,之后英特爾就可以根據不同的等級,開出不同的售價。如果芯片產量足夠大的話,測試成本在CPU總成本的占比可以忽略不計。

以已經非常成熟的40nm低功耗工藝為例,采用該制程工藝的CPU,其測試成本約為2美元,封裝成本約為6美元。

4、設計成本

設計成本主要包括專利成本、開發工具成本、工程師工資和場地費用等。

一是專利成本。目前,國內只有像龍芯、申威等少數走獨立自主技術路線的IC設計公司可以做到自己設計的CPU/微結構不含第三方IP,比如申威411、申威1621,龍芯3A2000/3B2000/3A3000/3B3000,以及微結構GS464E皆不含第三方IP。而國內其他IC設計公司基本上還處于購買國外IP做集成的階段,主要的IP供應商都是國外公司。

以海思、展訊、聯芯、全志、瑞芯微、新岸線等ARM陣營IC設計公司為例,這些公司無一例外依賴于ARM的IP授權——海思的麒麟950就購買了ARM Cortex A53和A72,不僅要一次性支付一筆不菲的授權費,而且每生產一片芯片,還要支付一定的專利費……

這種購買IP授權的商業模式,實際效果是ARM猶如開啟了印鈔機,而國內IC設計公司只能賺一點辛苦錢,直接導致國內ARM陣營IC設計公司“操的是賣白粉的心,賺的是賣白菜的錢”。

二是開發工具成本。要設計CPU就離不開EDA(電子設計自動化)工具的輔助,比如前端設計的仿真環境,低功耗流程設計工具,時序仿真工具,芯片后端設計的工具等等。

要購買這些EDA工具,同樣耗費頗為不菲,特別是國內IC設計公司的EDA工具大多數都依賴于國外公司的情況下(國內研發EDA工具做的最好的是華大九天,但市場份額比較小)。

三是工程師的工資等成本。像IBM、AMD、Marvell等IC設計公司中,有5年以上經驗的工程師的月薪在25K-50K之 間,國內海思、展訊、聯芯有5年以上經驗的工程師的月薪也在15K-30K之間。

假設一個IC設計公司有500人(英特爾公司有約10萬員工),每個員工以月薪20K計算,光工資成本一年就需要1.2億元……

四是其他成本。比如公司場地租用、宣傳營銷、行政開銷等零零碎碎的成本開銷,這些開銷因各個公司的情況有所不同,而且有的差距會非常大。

國產CPU售價為何居高不下

為了形象地解釋這個問題,我們假設兩款國產CPU:CPU-X和CPU-Y。

首先看晶片成本。

假設CPU-X采用40nm制程,芯片面積200平方毫米;CPU-Y采用28nm制程,芯片面積140平方毫米(制程越小,晶片面積越小)。

一片12寸晶圓價格為4000美元,面積約為7萬平方毫米。經計算可以得出,一片12寸晶圓可以切割出299個CPU-X或495個CPU-Y(40/28nm技術已經非常成熟,切割成本差異非常小,就忽略不計了)。

由于在將晶圓加工、切割成晶片的時候,并不能保證100%成果,因而存在一個成品率的問題,以49%的成品率計算,一片12寸晶圓可以切出146個符合良品標準CPU-X或242個CPU-Y,最后12寸晶圓的價格/切割出的成品晶片,可以得出結論: 采用40nm制程的CPU-X的晶片成本為27.3美元;采用28nm制程的CPU-Y的晶片成本為16.5美元。

可以看出,采用更先進的制程,能夠有效降低晶片成本。

其次看掩膜成本。

上文已經提到過40/28nm的工藝已經非常成熟,40nm低功耗工藝的掩膜成本約為200萬多美元。如果CPU-X的產量為10萬片,則分攤到每一片CPU上的成本為20美元;如果CPU-X的產量為100萬片,則分攤到每一片CPU上的成本為2美元;如果CPU-X的產量為1000萬片,則分攤到每一片CPU上的成本為0.2美元; 28nm HKMG掩膜成本為600多萬美元,如果CPU-Y的產量為10萬片,則分攤到每一片CPU上的成本為60美元;如果CPU-Y的產量為100萬片,則分攤到每一片CPU上的成本為6美元;如果CPU-Y的產量為1000萬片,則分攤到每一片CPU上的成本為0.6美元。

由此可見,在使用相同工藝的情況下,隨著CPU的產量增加,CPU的掩膜成本會逐步降低,如果產量以億為單位,即便使用最昂貴的14/16nm制程工藝,其掩膜成本也可以被壓縮到3美元以內。

再次看封測成本。

封裝成本一般占硬件成本的5%-25%左右,之前講過,比如CPU-X采用非常成熟的40nm制程,其測試成本約為2美元,封裝成本約為6美元。

最后看設計成本和其他成本。

設計成本非常不好量化,因為各家IC設計公司員工數量不同,購買IP的耗費、購買EDA工具的成本各異。其他成本同樣不好量化,各家公司場地租用、宣傳營銷、行政開銷等所耗費的資金差距非常大。 由于設計成本和其他成本非常不好量化,筆者按國際通用的低盈利芯片設計公司的定價策略8:20定價法來計算最后的售價,也就是硬件成本為8的情況下,定價為20(在不購買國外IP的情況下,一般能做到這個定價)。 別覺得這個定價高,其實已經比較低了,英特爾一般定價策略為8:35,AMD歷史上曾達到過8:50……

CPU硬件成本包括晶片成本+掩膜成本+測試成本+封裝成本四部分。 如果CPU-X的產量達到10萬片,則掩膜成本為20美元,加上27.3美元的晶片成本和8美元的封測成本,其硬件成本為55.3美元,采用8:20定價法,其售價為138.25美元。如果將CPU-X的產量達到100萬片,其硬件成本為37.3美元,采用8:20定價法,其售價為93.25。如果CPU-Y的產量為10萬片,則掩膜成本為60美元,之前計算過晶片成本為16.5美元,加上封測成本,那么硬件成本為85美元左右,采用8:20定價法,其售價為212.5美元。如果CPU-Y的產量為100萬片,則掩膜成本為6美元,硬件成本約為30美元,其售價約為75美元。

顯而易見,雖然使用更先進的制程會導致掩膜總成本提升,但卻可以降低晶片成本。

而只要產量足夠大,就可以使每片CPU的掩膜成本大幅降低,使擁有“更貴的制程工藝+更大的產量”屬性的CPU,會比擁有“便宜的制程工藝+較小的產量”屬性的CPU的成本更低,特別是在產量相差100倍的情況下,成本上的差距會猶如鴻溝。 那國產CPU的產量為何上不去呢?

像龍芯、申威等自主CPU,由于另起爐灶,自建技術體系,必然和現有的Wintel(微軟+英特爾)體系不兼容,在PC市場被Wintel壟斷的情況下,自然導致市場化進程步履維艱。

而兆芯雖然同樣采用X86指令集,可以跑Windows,不存在軟件生態問題,但在技術上完全依賴于威盛公司,自然提高了成本,加上性能孱弱,不具備市場競爭力——即便一味擴大產能,也只能是產量越大,虧得越多,所以只能在黨政軍市場尋求機會,產量自然非常有限。

總之,拋開國內IC設計公司和英特爾在設計能力的差距不談,單純講制程工藝和產量對性能和成本的影響,在國產CPU產量非常小的情況下,即便使用非常便宜的制程工藝流片,依舊導致其成本比英特爾的CPU要高,價格也更貴。 而英特爾則可以依靠市場的壟斷地位,即便使用了最貴的制程工藝,以龐大的產量壓低成本,攫取超額利潤,使自己的利潤率高達60%。

-

芯片

+關注

關注

453文章

50406瀏覽量

421829 -

聯發科

+關注

關注

56文章

2657瀏覽量

254557 -

5G

+關注

關注

1353文章

48367瀏覽量

563382

發布評論請先 登錄

相關推薦

請問mx880 5G數據終端可以設置優先5G網絡嗎?

聯發科-基于迅鯤平臺的XY8791 5G AI 智能模塊性能有多強?

2024年全球與中國7nm智能座艙芯片行業總體規模、主要企業國內外市場占有率及排名

Ethernovia推出全球首款采用7nm工藝的汽車PHY收發器系列樣品

研發一款7nm工藝的5G芯片的成本到底有多高

研發一款7nm工藝的5G芯片的成本到底有多高

評論