高速信號不遵循阻力最小的路徑;他們遵循阻抗最小的路徑。本系列文章介紹了下一個項目的PCB設計布局。

昨天的電子產品非常寬容。糟糕的原理圖設計和糟糕的PCB布局仍然會產生功能板。技能可以隨著時間的推移而增加,但運氣最終會耗盡。

當工程師第一次開始使用固態電子產品時,芯片的工作電壓更高,上升時間比現在制造的芯片更慢。但是,為了使PCB和微芯片更小,我們還降低了工作電壓,降低了噪聲容限。隨著我們繼續推動降低和降低IC工作電壓,工程師需要越來越多地考慮他們的選擇,以確保他們的設計無需昂貴且耗時的重新設計。

那么什么類型的噪聲要注意,以及如何改進設計以避免它們?

本文是受到主題演講啟發的幾篇文章之一,由Eric Bogatin博士在Altium Live 2018上發表。

故意路線返回路徑!傳播延遲

電磁場沿著并圍繞導體并滲透其附近的物體。這些場中存在的能量將被轉移到你想要的位置。

電磁場的變化以快速但有限的速度傳播,并且需要一些時間。現場變化到達電路的遠端。

當玩簡單的電路并查看頁面上的原理圖時,很多人會想象電路中的變化立即發生:按下開關并出現指示燈瞬間閃耀。很容易產生一種錯誤的直覺,即開關狀態的變化會立即改變光的狀態。

誤解的發生是因為狀態的變化超過了人類感知的極限,達到了很多個數量級。當處理傳播變化的時間(傳播延遲)與改變狀態所需的時間(上升時間/下降時間)相當或超過的電路時,您必須澄清您的思維過程以適應傳播延遲。/p》

電磁場的變化將以光速的一小部分傳播到整個電路中。 PCB走線上的狀態變化(邏輯低至邏輯高)沿著產生電流的長度建立電勢。該電流在導體周圍產生電磁場。但由于電磁場的變化需要時間傳播,因此跡線的兩端可能處于兩種不同的狀態,其中一個過渡點沿著長度移動。

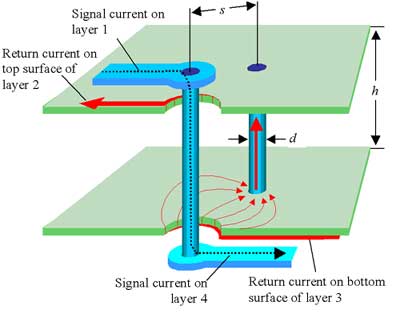

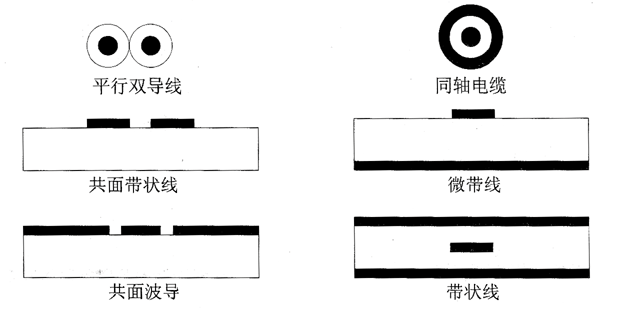

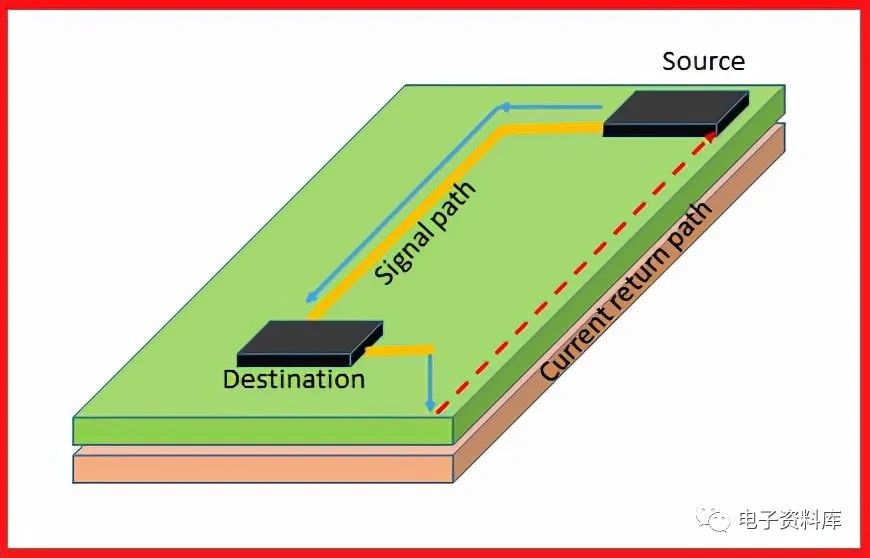

此圖顯示兩個導電PCB兩側的跡線。當電流開始在頂部跡線中流動時,在底部跡線中立即建立返回電流。

如果您沒有提供立即返回路徑您的走線和過孔,不需要的電流將在附近的導體中形成,特別是如果您有快速轉換(《1ns)。

最佳實踐規定如下:始終在同一層或相鄰層中提供接地返回路徑用于單端信號,差分對和電源層的層。

始終在同一層或相鄰層中為單端信號,差分對和電源層提供接地返回路徑。

地面返回途徑。來自“高速信號傳播”的Howard Johnson博士的圖片,圖5.33,第353頁,來自Signal Consulting,Inc。

高速信號和最小阻抗路徑

高速信號不遵循阻力最小的路徑;它們遵循阻抗最小的路徑。

當新工程師設計PCB時,他們傾向于完全忘記電路返回路徑中阻抗的無功部分,并嚴格關注電阻。當老工程師設計PCB時,他們傾向于做同樣的事情。誰又能責怪他們呢?很少有人能夠使用電磁模擬器,使他們可以看到電路在不同頻率下的行為。

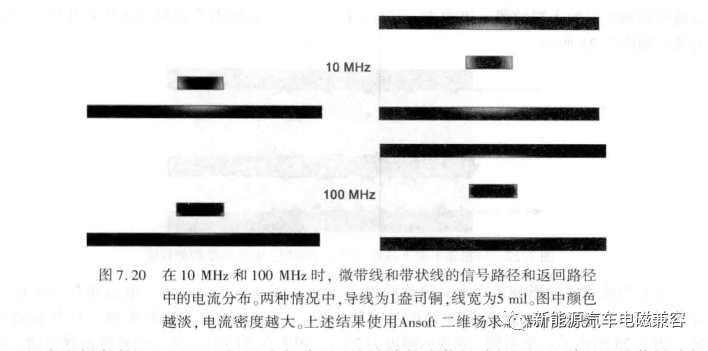

在考慮返回路徑時,請記住,隨著頻率的增加,阻抗的無功部分變得越來越重要,隨著上升/下降時間減少。

在均勻的適度頻率下,電流的返回路徑將嘗試直接在導體下方流動。如果你沒有提供這條路徑,它會發現一條不太理想的路徑通過電路的其他部分 - 也許是沿途創建天線。

返回電流尋找阻抗最小的路徑。在低頻時,地平面中的大部分返回電流直接從負載流到源。負載和源之間的這條直線表示最小電阻的路徑,并且在低頻時表示最小阻抗的路徑。隨著頻率的增加,走線和走線正下方銅線之間的互感會產生一個低阻抗路徑,導致接地層中的返回電流跟隨信號層上的走線。

如何在PCB設計中使用返回路徑

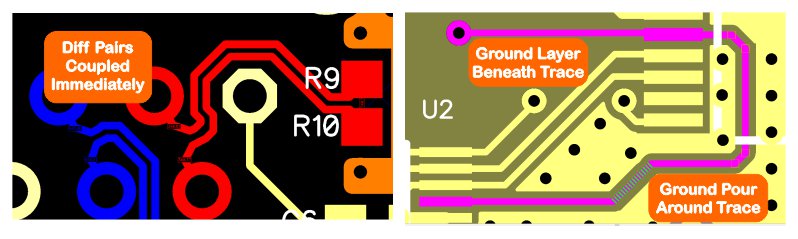

在PCB上,路由快速變化的信號,并在其附近有返回路徑。差分走線應從封裝引腳出來并立即緊密接近。時鐘信號和其他快速上升時間/下降時間信號應由地面澆注包圍和/或在其下方具有完整的,不間斷的接地平面,以最大限度地減少輻射EMI噪聲。如果您的設計需要FCC測試,您甚至可能需要路由兩個接地層之間的快速變化信號,并用通孔縫合環繞它們。

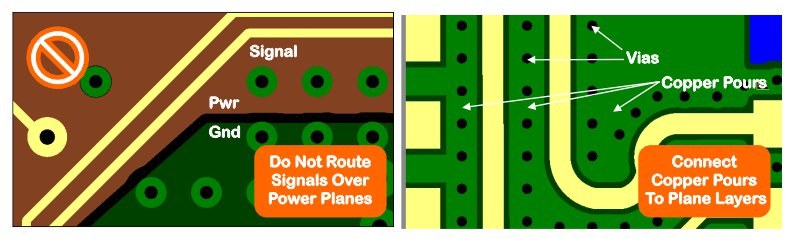

以下兩個圖像展示了PCB布局示例,展示了兩種降低接地噪聲的方法:

通過整個路徑將差分對保持在一起

在信號線的正下方或旁邊提供接地返回路徑

耦合在一起的差分對

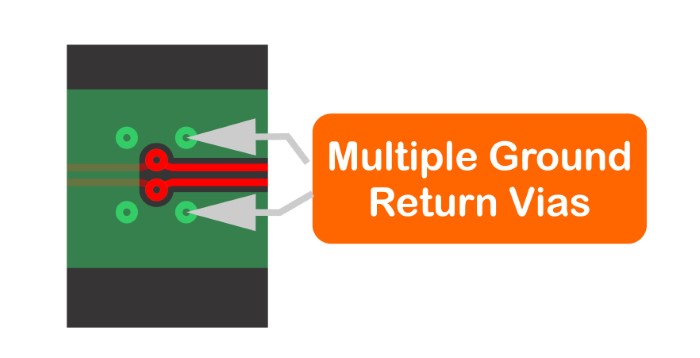

在差分對過孔附近放置接地回路過孔,為信號在層與層之間傳播時提供接地回路。

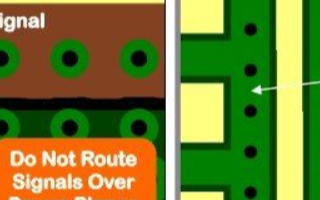

在下面的例子中,左邊的PCB la您將從上方(信號,電源,接地,信號)顯示多個PCB層,并演示通過電源層布線。在到達接地層之前,移動電源的信號將與電源平面共享其電場,并且平面的噪聲會在信號線中產生噪聲。

右側的PCB部分顯示了接地澆注和縫合兩個信號線附近。如果銅線沒有連接到下面的地平面,則銅線在互連線周圍會變成輻射元件。

結論:利用地面返回通孔和接地回路

仔細而有意地規劃接地回路,可以防止不必要的電流在電路的某些部分形成。為所有信號提供有意的接地回路過孔和接地回路 - 尤其是高速開關信號。

-

電路

+關注

關注

172文章

5849瀏覽量

171911 -

pcb

+關注

關注

4317文章

23006瀏覽量

396305

發布評論請先 登錄

相關推薦

高速電路PCB “地”、返回路徑、鏡像層和磁通最小化

高速PCB設計——回流路徑分析

淺談建模返回路徑阻抗效應

PCB EMC問題:最常見的返回路徑不連續資料下載

返回路徑平面寬度不同的情況VS完整返回路徑平面S參數情況

PCB設計之平衡銅技術介紹

高速電路PCB“地”、返回路徑、鏡像層和磁通化

使用返回路徑實現更好的PCB設計步驟概述!

使用返回路徑實現更好的PCB設計步驟概述!

評論