本文介紹了四層板疊加的常用選項。

PCB疊層是指構成電路板的銅層和絕緣層的排列。我們選擇的疊加可以通過幾種不同的方式在電路板性能中發揮重要作用。例如,良好的疊層可以降低電路板接地結構的阻抗并限制輻射和串擾。

電源和接地層的疊層

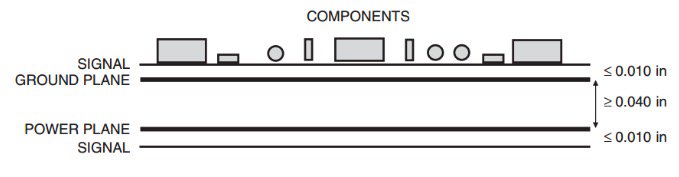

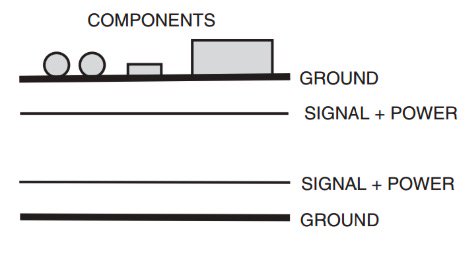

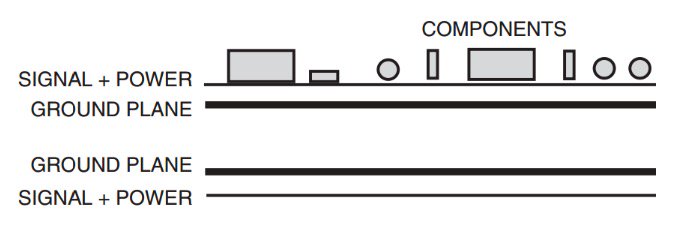

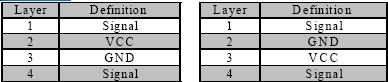

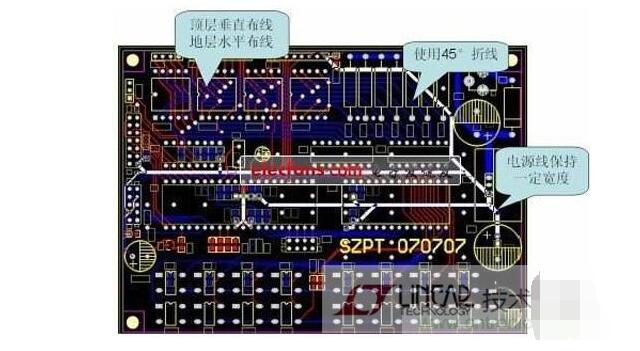

圖4和圖2顯示了四層板的兩種常見疊層。對于這兩塊板,訂單這些層的厚度完全相同,但它們的厚度不同。這似乎是一個小修改,但我們會看到不同層之間的適當間距可以提高電路板性能。

圖1。圖片由電磁兼容工程提供。

圖2。圖片由電磁兼容工程提供。

如您所見,兩個信號層都位于平面層(地平面或電源平面)旁邊。因此,給定信號的返回電流可以在相鄰平面上流動。這通過最小化由電流產生的環路面積來最小化電流返回路徑電感。低電感返回路徑可改善噪聲性能并減少電路板輻射(差分和共模發射)。

通常,與實施的相同電路相比,四層電路板的輻射可降低約20 dB在雙層板上。保持信號接近實心平面是這里發揮作用的關鍵因素。因此,為了進一步改善噪聲和EMI性能,我們可以使信號層與其相鄰平面之間的絕緣體更薄。這個簡單的技巧為我們提供了圖2所示的改進的疊層,其中信號層和平面之間的耦合以降低地面和電源平面之間的耦合為代價而增加。這可能不是嚴重的缺點,因為實際上這兩個堆疊中的任何一個都不能提供足夠的平面到平面耦合。我們將在一分鐘內更詳細地討論這個問題。請注意,兩個疊層具有相同的整體電路板厚度。

圖1和圖2的疊層是常用的,但它們有兩個缺點,這兩個缺點都來自于地面的事實和電源層彼此不夠接近,因此,它們之間只存在很小的平面間電容。

常規四層堆棧的缺點

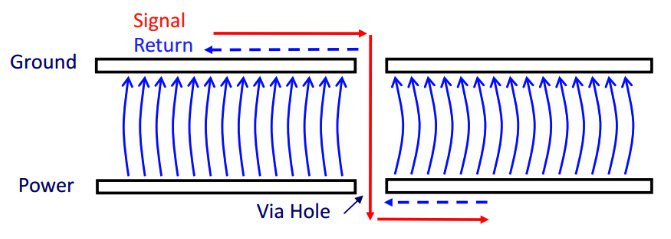

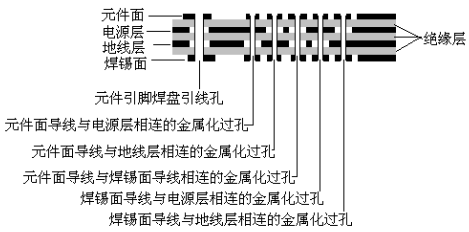

圖1和圖2中的堆棧的第一個問題出現在跟蹤將層從第1層更改為4或反之亦然。如圖3所示。

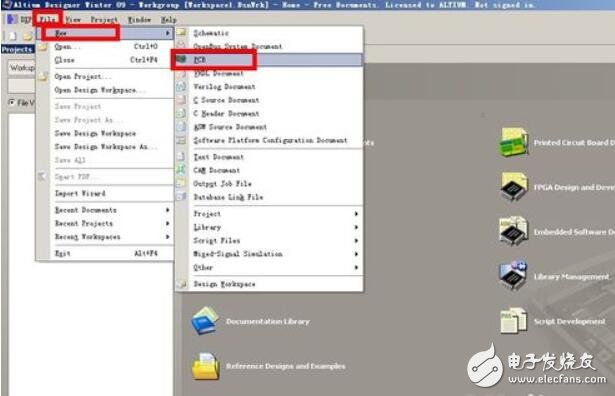

圖3. 圖片由Altium提供。

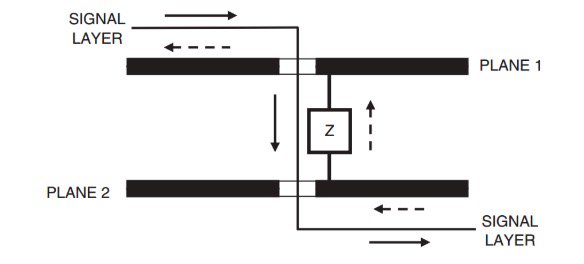

該圖顯示當信號跡線從第1層到第4層(紅線)時,返回電流也必須改變平面(藍線)。如果信號的頻率足夠高并且平面靠近在一起,則返回電流可以流過地面和電源平面之間存在的平面間電容。然而,沒有直接導電連接的返回電流會在返回路徑中產生中斷,我們可以將這種中斷視為平面之間的阻抗(見圖4)。

圖4。圖片由電磁兼容工程提供。

如果層間電容不夠大,電場將擴散到電路板的相對較大區域,這樣平面之間的阻抗就會減小,返回電流也會流動回到頂層飛機。在這種情況下,由此信號創建的字段可能會干擾更改圖層的附近信號的字段。這根本不是所希望的。不幸的是,在0.062英寸的4層電路板上,這些平面彼此遠離(至少0.020英寸,如圖1和圖2所示),并且平面電容很小。因此,我們將有上述電場干擾。這可能不會導致信號完整性問題,但我們肯定會產生更多的EMI。這就是為什么在使用圖1和圖2所示的疊層時,我們最好避免更換層,特別是對于時鐘等高頻信號。

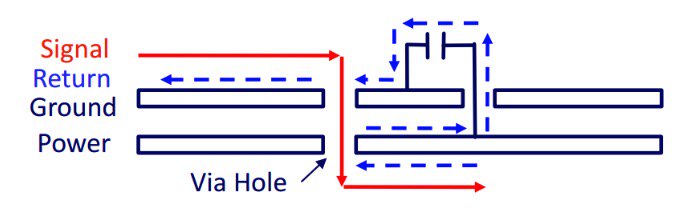

添加去耦通常是一種好習慣。電容靠近過渡通孔,以降低返回電流的阻抗(見圖5)。然而,這種去耦電容器對于非常高頻的信號是無效的,因為它們的自諧振頻率低。對于頻率高于約200-300 MHz的交流信號,我們不能依靠去耦電容來創建低阻抗返回路徑。因此,我們需要一個去耦電容(低于200-300 MHz)和一個相對較大的內層電容,用于更高的頻率。

圖5圖片由Altium提供。

通過不改變關鍵信號層可以避免上述問題。然而,四層板的小型內部電容導致另一個嚴重問題:功率輸送。時鐘數字IC通常需要大的瞬態電源電流。隨著IC輸出的上升/下降時間減少,我們需要以更高的速率提供能量。為了提供充電源,我們通常將去耦電容放置在非常靠近每個邏輯IC的位置。然而,存在一個問題:當我們超越自諧振頻率時,去耦電容不能有效地存儲和傳遞能量,因為在這些頻率下,電容器將像電感器一樣工作。

從今天的大部分時間開始IC具有快速上升/下降時間(約500 ps),我們需要額外的去耦結構,其自諧振頻率高于去耦電容的自諧振頻率。板的平面間電容可以是有效的去耦結構,只要這些平面彼此足夠接近以提供足夠的電容即可。因此,除了采用常用的去耦電容外,我們更傾向于使用緊密間隔的電源和接地層,為數字IC提供瞬態功率。

請注意,我們之間通常沒有薄的絕緣體。由于共同的板制造工藝,四層板的第二和第三層。在第2層和第3層之間使用薄絕緣體的四層板可能比傳統的四層板成本高得多。

兩個改進的疊層

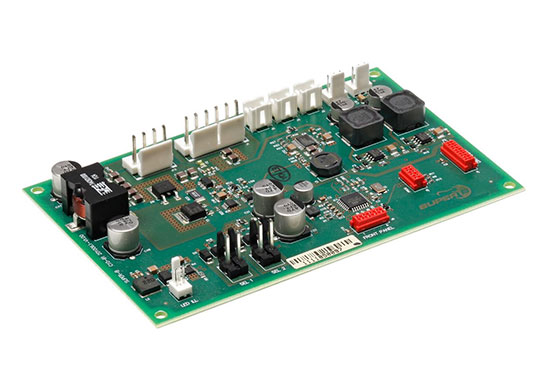

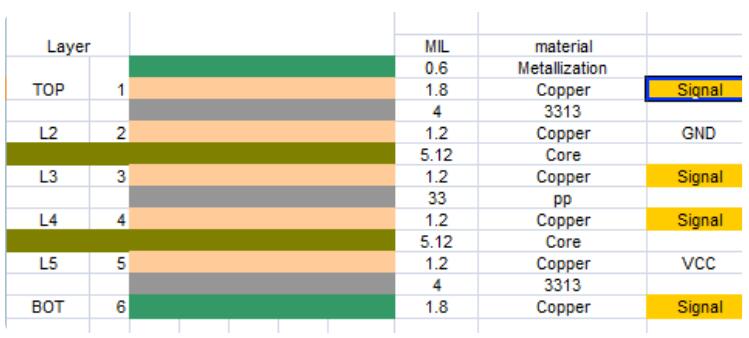

下面的圖6和圖7顯示了兩層改進的四層板疊加。

圖6. 圖片由電磁兼容工程提供。

圖7。圖片由電磁兼容性工程提供。

與圖1和圖2的疊層一樣,信號走線應與平面相鄰,電流返回路徑電感應最小化。在這方面,圖6中的疊層可能并不理想,因為安裝的元件將阻止我們在第1層上具有堅固的接地層。假設我們可以將大部分信號走線布線在地平面的實體部分上,我們觀察到信號層和平面之間的絕緣體很薄,這是非常需要的。

圖6和圖7中的疊層有兩個接地層。這使我們能夠采用低阻抗接地結構并減少共模輻射。而且,在圖6中,接地平面包圍信號層。作為屏蔽,平面可以包含來自高速信號跡線的輻射。我們甚至可以在電路板的外圍放置縫合過孔,將兩個接地層連接在一起。這將創建法拉第籠并進一步包含輻射。圖7中的疊層平面不能作為屏蔽。

通過這兩個疊層,我們沒有電源平面。我們可以使用電力灌注或網格電源結構。如果我們可以對信號和電源走線進行布線并將元件安裝在一層(第1層)上,那么可以采用圖7中的疊層(這種疊層具有堅固的接地層)。但是,如果我們沒有足夠的空間用于所有這些,我們可以使用圖6中的疊加。

雖然這兩個疊層沒有固態電源平面,但是電源注入是靠近地平面。結果,功率注入和接地平面將產生相對大的電容,其可以在高頻下充當去耦結構。眾所周知的PCB設計師Rick Hartley提供了測量數據,證實圖6和圖7的功率澆注和平面之間的去耦優于傳統四層板的接地和電源平面提供的去耦(圖1和圖2) )。利用改進的疊層的去耦結構以及通常的去耦電容,我們可以更容易地為高速數字IC提供瞬態功率。

最后,隨著圖6和圖6的改進疊加如圖7所示,高速信號可以改變層,因為所有信號都以地平面為參考(在傳統的疊層中,信號參考地平面或電源平面)。因此,我們可以通過靠近過渡通孔放置一個平面到平面,為返回電流提供低阻抗路徑。有關詳細信息,請參閱“電磁兼容性工程”一書的第16.3.3節。

結論

在本文中,我們研究了幾種不同的堆棧 - 用于四層板。我們看到堆疊選擇可以通過幾種不同的方式在電路板性能中發揮重要作用。良好的疊層可以降低電路板接地結構的阻抗并限制輻射和串擾。此外,電路板疊加會影響瞬態功率傳輸和更改圖層時的信號路由策略。

-

pcb

+關注

關注

4317文章

23010瀏覽量

396326 -

四層板

+關注

關注

0文章

28瀏覽量

13463

發布評論請先 登錄

相關推薦

PCB四層板設計原理下載

四層板布線原則

四層板怎么畫

pcb單層板、雙層板、四層板、六層板、八層板、十層板、十二層板圖文解釋

電路板四層板和兩層板有什么區別?

四層板疊加的常用選項介紹

四層板疊加的常用選項介紹

評論