在上一篇文章中,我們探討了是否連接電容器的問題通過走線或通過一對過孔將電容去耦到IC電源引腳。我們看到通孔技術(shù)是優(yōu)越的,因?yàn)樗档土穗姼校?dāng)我們試圖確保去耦電容在50-100 MHz的頻率下有效時(shí),電感是我們必須克服的主要障礙。高達(dá)數(shù)百兆赫。

過孔和平面

在本文中,我們將探討去耦電感的問題。通孔和平面層配置。然而,在我們進(jìn)入討論之前,我們需要明確以下幾點(diǎn):隨著我們深入探討高速去耦領(lǐng)域,我們越來越關(guān)注平面連接,直到最終看起來很大程度上忽略了跟蹤。以下注意事項(xiàng)將有助于將此現(xiàn)象置于語境中:

高電感

正如我們在上一篇文章中所看到的,與連接相比,跡線僅具有過多的電感依賴于過孔和平面層。

平面電容

去耦電容與平面相互作用的方式似乎成為主導(dǎo)因素隨著運(yùn)行頻率的增加。科學(xué)在這里開始變得復(fù)雜,我理解細(xì)節(jié)的能力有限,甚至解釋它們的能力也越來越差。我在本文中發(fā)現(xiàn)的一個(gè)有趣和直接的陳述表明,在某些情況下,去耦電容本身受到電感的阻礙,以至于它無法真正為IC提供電流。相反,平面電容提供瞬態(tài)去耦電流,電容器的工作是為平面充電。

擁擠的布局

高速數(shù)字系統(tǒng)通常涉及復(fù)雜的空間受限布局,這些布局將大部分PCB空間專用于組件。幾乎沒有跡線的空間,因此電路板設(shè)計(jì)師很樂意盡可能使用過孔。

分布式電容與離散電容

如果平面電容是在某些高速數(shù)字設(shè)計(jì)中真正的去耦電荷源,電容真的需要“盡可能靠近引腳”嗎?位置是否重要?質(zhì)疑正確解耦的基本原則之一的有效性似乎令人震驚,但這正是Hubing等人的觀點(diǎn)。在這篇研究論文中做過。用另一篇論文的作者的話來說,Hubing等。聲稱在某些條件下電容器的位置“不重要”,盡管它們可能已將其結(jié)論擴(kuò)展到“研究的有效性范圍之外”。無論如何,這是電容器之間相互作用重要性的另一個(gè)例子。在平板上到處都有“分布電容”的平面層。

最小化電感

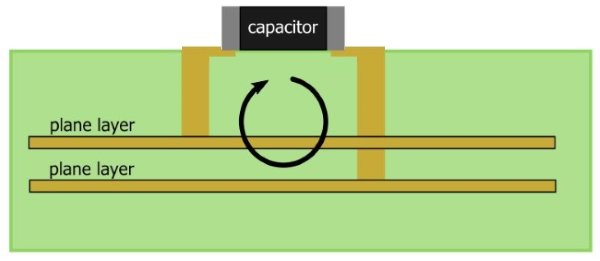

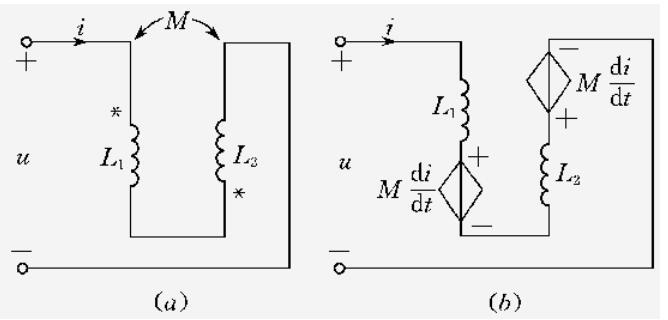

去耦電容的總電感取決于由電容,過孔和平面形成的電流環(huán)的面積。

如您所見,環(huán)路區(qū)域受兩個(gè)過孔之間的間隔以及電容器與平面層之間的距離的影響。因此,如果目標(biāo)是改善去耦性能,那么到平面和通過分離的距離是需要解決的關(guān)鍵因素。

與飛機(jī)的距離

如果您正在設(shè)計(jì)一個(gè)典型的四層板,那么您可以做的就是減少與飛機(jī)的距離 - 去耦帽將始終接近一個(gè)平面層并且遠(yuǎn)離另一個(gè)平面層。

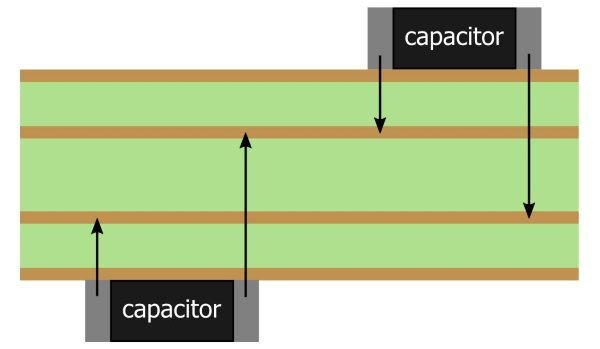

如果但是,電路板有四層以上,您可以靈活地優(yōu)化去耦電容相對于電源和接地層的位置。此外,現(xiàn)在是指出如果不將電源和接地層放置在相鄰層上,將會損失大量分布電容的好時(shí)機(jī)。在我看來,高速數(shù)字設(shè)計(jì)將從以下配置中受益匪淺:

在兩個(gè)組件層之一上放置盡可能多的高速IC(讓我們說它是頂部)。

布置電源和接地層,使它們相鄰并靠近頂層。

將所有去耦帽放在頂層,使它們具有短連接

通過分離

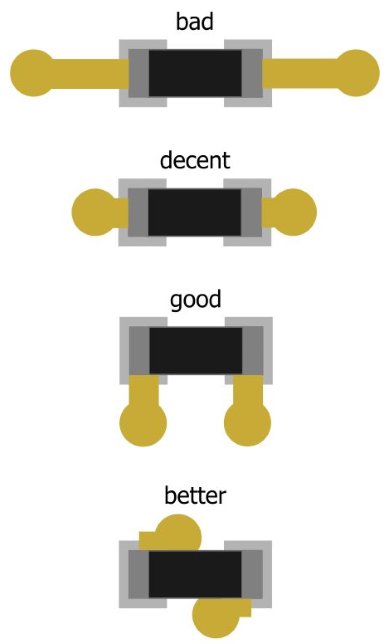

減少通孔分離的第一種方法是使用較小的去耦電容。在我的電路板上,我使用0603封裝,因?yàn)槲医?jīng)常手工組裝它們;如果電路板由機(jī)器組裝,0402是更好的選擇。

現(xiàn)在最小化電感是選擇最佳通孔配置的問題:

改編自 本文件第29頁的圖表 。

請注意,我們主要關(guān)注兩個(gè)過孔之間的距離。因此,第三個(gè)圖表標(biāo)記為“良好”,第二個(gè)圖表標(biāo)記為“正常”,盡管“體面”配置使用較短的走線將電容器端子連接到過孔。

結(jié)論

我希望本文能讓您深入了解高速數(shù)字PCB設(shè)計(jì)的復(fù)雜世界。我認(rèn)為很明顯,最小化環(huán)路面積是降低電感并因此改善高頻性能的關(guān)鍵,但我不確定如何考慮在整個(gè)電路板上隨機(jī)分配去耦電容的可能性(在某些情況下)。如果您對此主題有任何想法,請隨時(shí)在評論中分享。

-

電容器

+關(guān)注

關(guān)注

64文章

6208瀏覽量

99337 -

電感

+關(guān)注

關(guān)注

54文章

6114瀏覽量

102179 -

去耦

+關(guān)注

關(guān)注

2文章

50瀏覽量

18266

發(fā)布評論請先 登錄

相關(guān)推薦

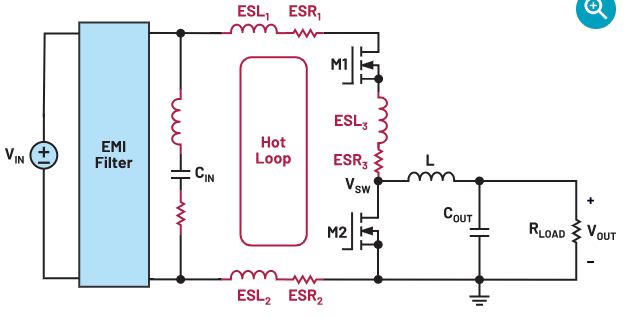

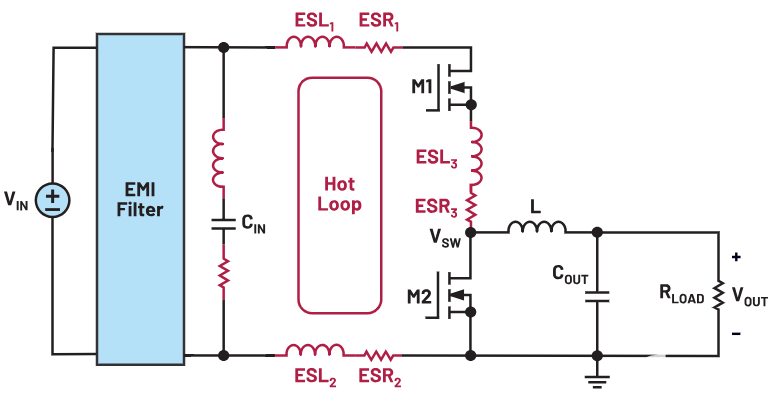

如何通過最小化熱回路PCB ESR和ESL來優(yōu)化開關(guān)電源布局

LabVIEW最小化的使用

PCB布局提示和技巧:最小化去耦電感

vrf設(shè)置程序窗口最小化

基于DITC的開關(guān)磁阻電機(jī)轉(zhuǎn)矩脈動最小化研究

基于帶權(quán)核范數(shù)最小化的去噪模型

如何通過最小化熱回路來優(yōu)化開關(guān)電源布局?

如何通過最小化熱回路PCB ESR和ESL來優(yōu)化開關(guān)電源布局

如何通過最小化熱回路來優(yōu)化開關(guān)電源布局?

最小化去耦電感有哪些技巧

最小化去耦電感有哪些技巧

評論