數字信號(包括串口和 GPIO 口)的走線注意事項如下:

1. 數字信號應盡量遠離晶體和 RF 走線。

2. 數字信號應盡可能用地圍起來,以減少相互串擾。

3. 在布線不合理或走線太長情況下,串口 CSB,FCSB,SDIO,SCLK 管腳容易受到干擾,功率輸出(20dBm)越大,工作頻率越低,受干擾的概率越大。

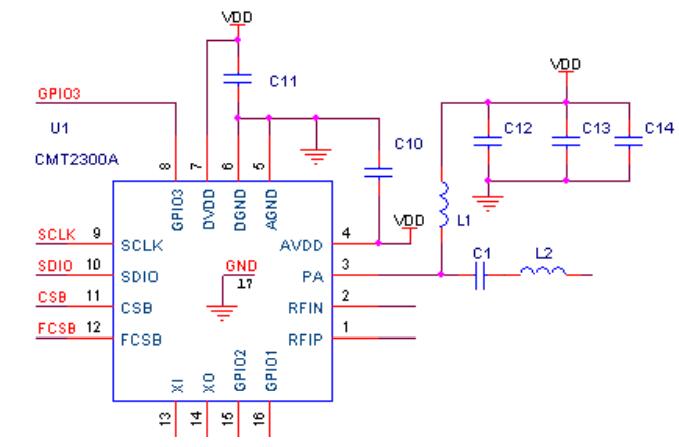

為了減輕電源上的噪聲紋波對芯片的影響,及 PA 輸出對電源的影響,用戶應當在以下幾處設計濾波電容。

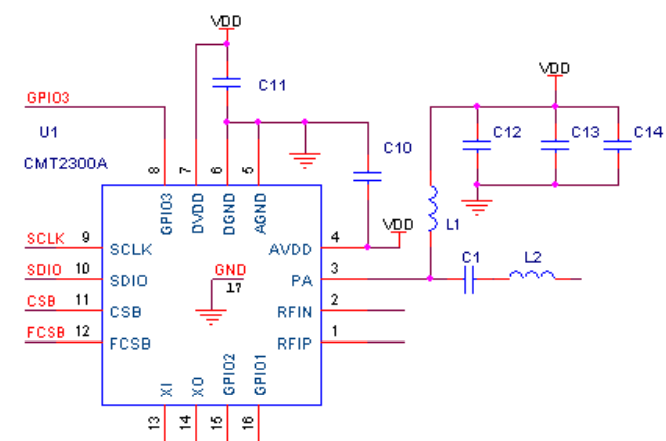

1. C10 靠近芯片的 AVDD 管腳處。

2. C11 靠近芯片的 DVDD 管腳處。

3. C12, C13 靠近扼流電感, 建議 C13 保留以應對高次諧波。

4. C14 根據 PA 輸出功率和供電電路性能,推薦值 4.7 - 10uF。

鋪地設計

說明如下:

1. 參考地層:射頻走線需要在相鄰層有大片的連續地做參考平面,以實現高效的功率輸出和最佳接收靈敏度。

2. 射頻走線兩側包地并打過孔到參考地平面以減小雜散輻射。

3. 各層地網絡打過孔到參考地層,減小回路路徑,從而使回路的輻射減少。

4. 線路板邊沿盡量鋪地,且過孔間距不超過 λ/10,從而減小輻射和增強抗 ESD 能力。

5. IC 襯底一定要有幾個過孔到地層,有利于提升芯片的射頻性能指標。

6. 晶體電路對干擾敏感,用包地隔離。

-

芯片

+關注

關注

454文章

50425瀏覽量

421856 -

濾波電路

+關注

關注

46文章

631瀏覽量

69594 -

GPIO

+關注

關注

16文章

1196瀏覽量

51919

發布評論請先 登錄

相關推薦

CMT2300A無線數據收發模塊資料

電源地 信號地 模擬地 數字地 射頻的分析與布局

為什么說CMT2300A是Sub-1GHz超低功耗的射頻收發器

超低功耗Sub-1GHz性價比首選方案:CMT2300

超低功耗Sub-1GHz性價比首選方案:CMT2300

DSP芯片外圍電路典型設計(數字信號處理器芯片TMS320F

CMT2300A 超低功耗Sub-1GHz射頻收發器的詳細中文資料免費下載

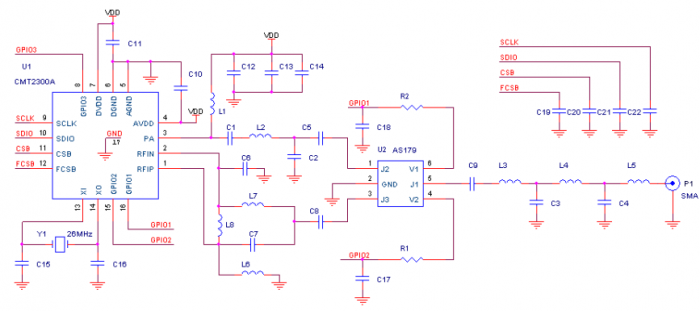

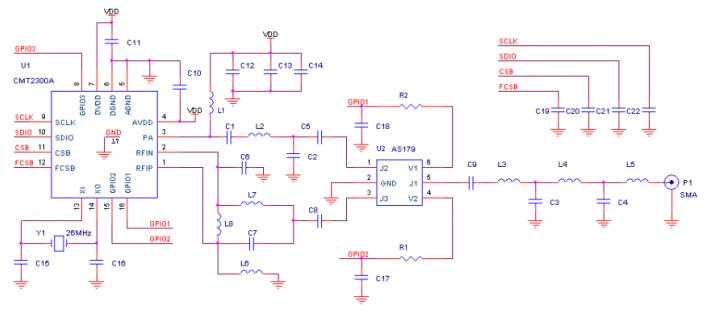

使用CMT2300A芯片設計開關射頻匹配網絡電路的詳細概述

CMT2300A的開關射頻匹配網絡電路設計

CMT2300A 433MHz無線收發芯片

使用CMT2300A芯片設計射頻匹配網絡的數字信號和電源濾波電路與鋪地

使用CMT2300A芯片設計射頻匹配網絡的數字信號和電源濾波電路與鋪地

評論