高效能運算領域的領導廠商arm與晶圓代工龍頭臺積電26日共同宣布,發布業界首款采用臺積電先進的CoWoS封裝解決方案,內建arm多核心處理器,并獲得硅晶驗證的7納米小芯片(Chiplet)系統。

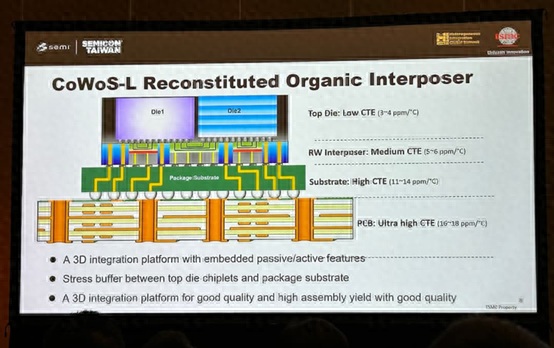

臺積電表示,此款概念性驗證的小芯片系統成功地展現在7納米FinFET制程及4GHz arm核心的支援下打造高效能運算的系統單芯片(System-on-Chip,SoC)之關鍵技術。同時也向系統單芯片設計人員演示運作時脈4GHz的芯片內建雙向跨核心網狀互連功能,及在臺積電CoWoS中介層上的小芯片透過8Gb/s速度相互連結的設計方法。

臺積電進一步指出,不同于整合系統的每一個元件放在單一裸晶上的傳統系統單芯片,將大尺寸的多核心設計分散到較小的小芯片設計更能完善支持現今的高效能運算處理器。

此高效的設計方式可讓各項功能分散到以不同制程技術生產的個別微小裸晶,提供了靈活性、更好的良率、及節省成本的優勢。

小芯片必須能夠透過密集、高速、高頻寬的連結來進行彼此溝通,才能確保最佳的效能水準,為了克服這項挑戰,此小芯片系統采用臺積電所開發的Low-voltage-INPackage-INterCONnect(LIPINCONTM)獨特技術,資料傳輸速率達8Gb/s/pin,并且擁有優異的功耗效益。

另外,此款小芯片系統建置在CoWoS中介層上由雙個7納米生產的小芯片組成,每一小芯片包含4個arm Cortex–A72處理器,以及一個芯片內建跨核心網狀互連匯流排,小芯片內互連的功耗效益達0.56pJ/bit、頻寬密度1.6Tb/s/mm2、0.3伏LIPINCON介面速度達8GT/s且頻寬速率為320GB/s。此小芯片系統于2018年12月完成產品設計定案,并已于2019年4月成功生產。

arm資深副總裁暨基礎設施事業部總經理Drew Henry表示,這次與我們長期伙伴臺積電協作的最新概念性驗證成果,結合了臺積電創新的先進封裝技術與arm架構卓越的靈活性及擴充性,為將來生產就緒的基礎架構系統單芯片解決方案奠定了絕佳的基礎。

臺積電技術發展副總經理侯永清博士表示,此款展示芯片呈現出我們提供客戶系統整合能力的絕佳表現,臺積電的CoWoS先進封裝技術及LIPINCON互連介面能協助客戶將大尺寸的多核心設計分散到較小的小芯片組,以提供更優異的良率與經濟效益。arm與臺積電的本次合作更進一步釋放客戶在云端到邊緣運算的基礎架構應用上高效能系統單芯片設計的創新。

-

芯片

+關注

關注

450文章

49631瀏覽量

417106 -

ARM

+關注

關注

134文章

8966瀏覽量

365007 -

臺積電

+關注

關注

43文章

5534瀏覽量

165696 -

CoWoS

+關注

關注

0文章

122瀏覽量

10396

發布評論請先 登錄

相關推薦

arm與臺積電共同發布業界首款CoWoS封裝解決方案 提供更多優勢

arm與臺積電共同發布業界首款CoWoS封裝解決方案 提供更多優勢

評論